2018112103 이지환 10/3(화) 요약정리 과제

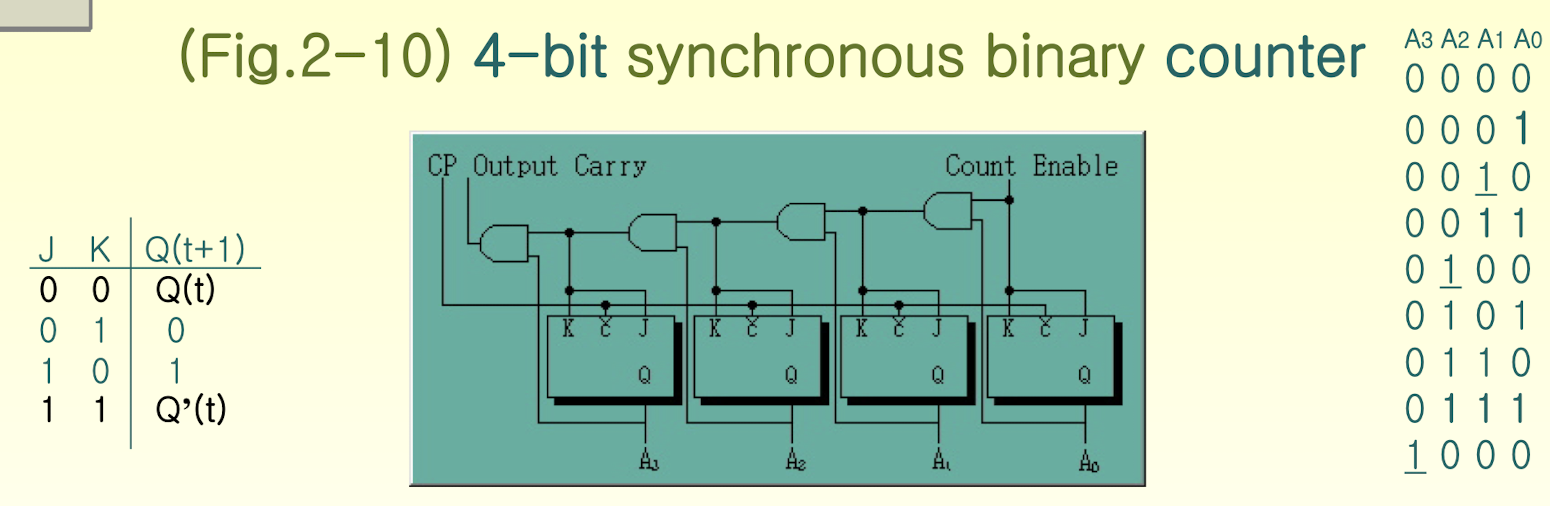

이 0에서 1로 바뀌는 경우

—> 외부에서 1이 들어올 때

이 0에서 1로 바뀌는 경우

—> A(0)가 1이었을 때, 그리고 외부에서 1이 들어온 경우

이 1에서 0으로 바뀌는 경우

—> A(0)가 1이었을 때, 그리고 외부에서 1이 들어온 경우

이 0에서 1로 바뀌는 경우

—> , 이 둘다 1이고 외부에서 1이 들어온 경우

이 1에서 0으로 바뀌는 경우

—> , 이 둘다 1이고 외부에서 1이 들어온 경우

가 0에서 1로 바뀌는 경우

—> , , 이 모두 0이고 외부에서 1이 들어온 경우

가 1에서 0으로 바뀌는 경우

—> , , 이 모두 0이고 외부에서 1이 들어온 경우

- 우리가 사용하는 JK F/F 조건들 4가지 중 실제로 사용하는 건 2가지(0,0 / 1,1)밖에 없음

위에 바뀌는 경우를 보면, 이전 비트들이 전부 1이고 외부에서 들어오는 값이 1인 경우에 변화가 생김.

만약 6-bit counter를 만들고 싶으면 J/K F/F 2개와 AND gate 가 이루는 Stage 2개를 추가해주기만 하면 됨.

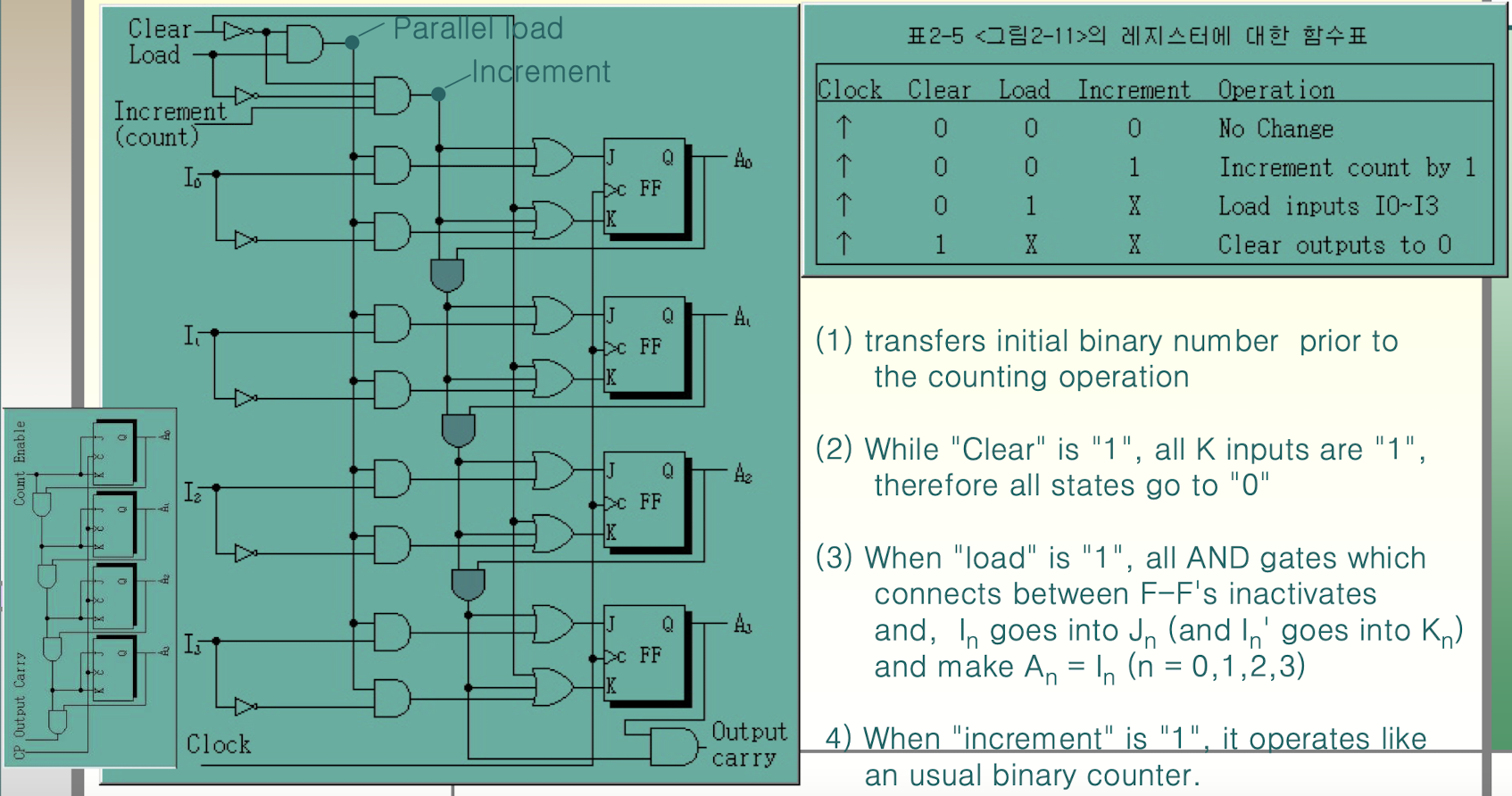

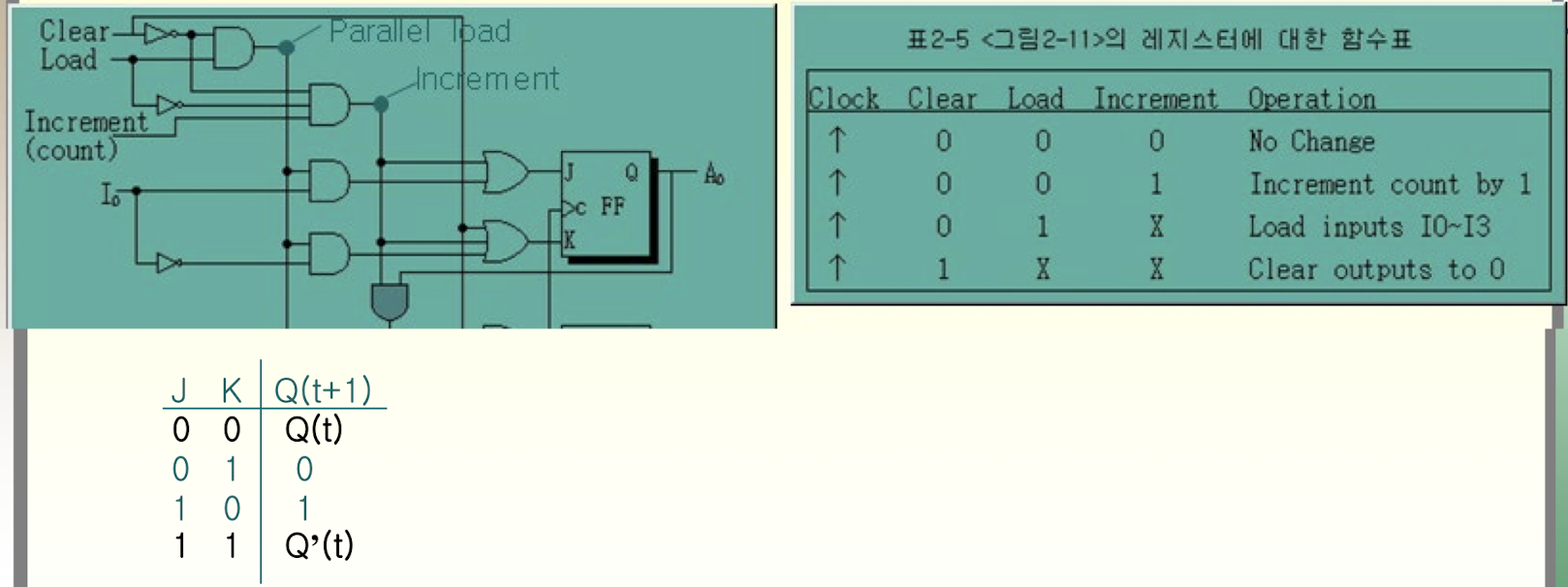

- 4-bit binary counter with parallel load and synchronous clear

parallel load : 외부값을 F/F에 들어가도록 함

synchronous clear : F/F안에 들어있는 모든 값을 0으로 초기화 (k단자에 1이 들어가면 됨)

- 구조

- 외부에 Clear Load 단자 1개 존재

- Parallel load 수행을 위해 시그널 존재

- Increment는 count 기능을 수행 : 들어오는 입력값이 1이면 count함.

회로의 동작을 정리한 것이 위의 표 2-5임.

- 동작 검증

-

Clear, Load, Increment가 모두 0

—> 어떻게 해도 J, K단자에 모두 0이 들어갈 수 밖에 없어서 다음상태 값 Q(t+1)은 현 상태 Q(t)와 같다

-

Increment 단자가 1이면

—> J/K단자 모두 1의 값이 들어가게 된다. Q’(t) : (compliment)

-

Load 단자가 1이면

—> 가 0일 경우 NOT gate 통과 후 AND gate → J=0, K=1, 다음 상태는 0이 된다. 이 1이라면 J는 1, K는 NOT gate 통과 후 AND gate → 0이 되고, 다음 상태는 1이 된다.

-

Clear가 1이면

—> J = 0, K = 1, 다음 상태값은 0이 된다.

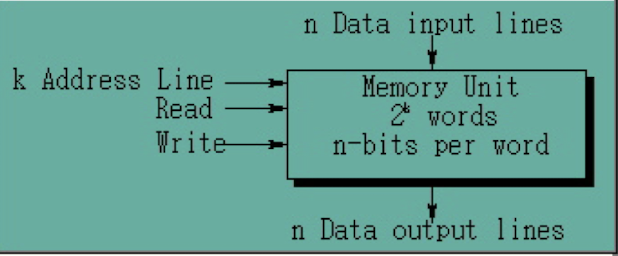

2-7. Memory Unit

1) 입출력 작업을 위한 회로를 갖춘 storage cell의 집합

2) Word 단위로 읽기/쓰기 작업이 이루어진다. Input/Output 작업이 Word base로 이루어짐.

→ 만약, 4바이트 word인 경우, 32비트 정보가 parallel 하게 읽기 모드에서 읽혀지고, 쓰기 작업에서는 메모리 안으로 들어간다.

3) 8 M memory = 8 M bytes memory

→ DRAM의 경우는 다름. 4 M DRAM : 4 M bits DRAM을 뜻함.

4) 메모리의 전체적인 크기는 word 개수 x 한 word가 몇 비트로 구성이 되느냐

ex) 한 Word가 4바이트(32비트)로 구성, 즉 32비트 x (Word 개수) 가 됨.

5) 각 word는 ADDRESS라고 부르는 유니크한 주소를 하나씩 가지고 있음.

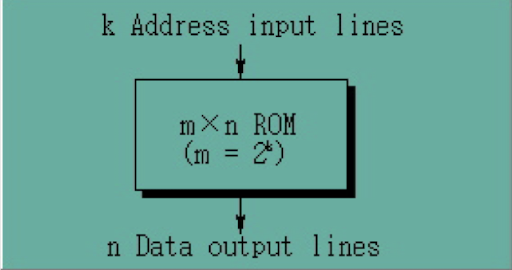

짜리 word다 —> 개 만큼의 word를 가지고 있고, 그만큼의 주소를 가지고 있어야 함.

첫 주소가 0번지면 맨 마지막 주소는 이 됨.

(4 address lines → 0 ~ 개 (15개) word)

6) 두개 유형의 메모리

-

RAM(Random Access Memory) : 주소값을 받으면 한 번에 접근해서 읽기나 쓰기가 가능함

DRAM(Dynamic) / SRAM(Static)으로 구분되어짐.

RAM은 volatile의 특성을 가진다. 전기적 특성의 영향을 받는다 ex) 전기가 끊기면 정보가 다 날아감

-

ROM(Read Only Memory) : non-volatile. 전기적 특성 x

mask ROM : 공장에서 메모리 안에 들어갈 정보가 모두 쓰여진 다음에 출하

PROM(programmable ROM) : 한 번(one time)은 정보를 삽입 가능. 연구실 내 랩실에서 많이 사용됨

EPROM(Erasable PROM) : 지울 수 있는 PROM (특수한 경우에만 지울 수 있음. 지우기 위해 UV라는 특수한 장치 사용)

EEPROM(Electrically EPROM) : 전기적은 신호로 EPOM의 정보를 지울 수 있다

7) RAM의 경우 메모리 안에 어디에 위치해있든 똑같은 시간 안에 접근 가능

-> 읽기 쓰기 작업 가능

반대 개념 : Sequential access(순차적 접근). 대용량의 백업을 받기 위한 저장공간. ex) 테이프, 뒤에 있는 정보에 접근하기 위해 앞에 있는 테이프를 모두 감아줘야함(이런 방식)

Word의 개수가 몇개냐에 따라 각 워드마다 주소 공간이 할당.

→ 개 word가 있으면 k개 address line이 존재

전체적인 메모리의 크기 : , n은 한 Word의 길이 (n 비트)

- 쓰기 작업(Write operation) 절차

→ k Addres Line을 통해 주소값을 전달을 해줘야 함. 그 다음 저장 시켜야 하는 데이터가 n Data input line을 통해 전달. 그리고는, 쓰기 작업을 하겠다는 신호가 와야함(Activate write strobe). 이제 메모리에 k Address Line을 통해, 전달된 위치에 쓰기 작업이 이뤄지는 것.

- 읽기 작업(Read operation) 절차

몇 번지부터 읽어라 라고 할테니까, k Address Line을 통해 주소값이 전달이 되고 그 다음에는 쓰기 작업과 똑같이 신호(Activate read strobe)가 켜지면, 메모리 안의 정보를 읽어 밖으로 내보낸다.

워드의 크기가 n비트라 했으니 word단위로 쓰기/읽기 작업이 이루어짐.

8) ROM : 공장에서 이미 다 정보가 쓰여진 채로 출하되므로 일반적으로 읽기만 가능. 결국 읽기작업만 가능한 것이고, 마찬가지로 주소값 전달해주면 그 위치에서 읽어서 그 값을 밖으로 빼주면 되는 것임.