💻CPU

📚개념

메모리에서 명령어를 인출하고 해석하여 명령을 실행하는 장치

🔨 기능

- 전송 기능

- 메모리 <-> 레지스터 간 데이터 전송 및 교환

- CPU와 입출력 장치간 데이터 전송 기능

- 연산 기능

- 제어 기능

🔍구성

- 산술연산 장치(ALU)

실제 CPU에서 연산을 수행하는 장치(유닛)

연산을 위해 레지스터 또는 메모리로부터 데이터가 입력되고(Load) 그 처리 결과가 레지스터 중의 하나 또는 메모리에 저장됨(Store)

- 제어 장치

명령어, 데이터의 입출력과 ALU 동작 제어

- 프로그램/코드/명령어를 해석하고 이의 실행을 위한 제어 신호들을 순차적으로 발생

- 명령을 읽고 실행하는데 필요한 CPU 내부의 각 장치 간의 데이터 흐름을 제어

- 어느 장치/레지스터에게 전송할 것인가를 지시하고 동작 시간을 결정한다.

- 프로그램 카운터(레지스터)를 사용

프로그램 카운터 : 다음에 인출할 명령어 주소를 임시 저장하는 레지스터

- 레지스터

메모리와 유사하나 훨씬 비싸고 빠른 소규모 임시 저장장치

-

범용 레지스터/ 누산기

- 연산의 중심 역할

레지스터의 비트 수 == CPU 1회 연산에 처리 가능한 데이터 비트 수

-

용도 지정 레지스터

(명령어 관련)

- 프로그램 카운터

- 명령어 레지스터 : 가장 최근에 인출된 명령어를 임시 저장하는 레지스터

(데이터, 주소 관련)

- 데이터 레지스터 : 데이터 버스(CPU와 메모리 사이의 데이터 전달을 위한 연결)에 데이터를 읽고 쓰기 위해 잠시 저장해두는 버퍼 레지스터

- 주소 레지스터 : 주소 버스에 주소를 출력하기 전에 임시 저장하는 레지스터 (다른말로 포인터라 함)

(입출력 관련)

- 입출력 레지스터 : 주변 장치와 CPU 간에 데이터 전송/ 중개를 전담

- 캐시

컴퓨터 메모리 버퍼를 지칭함

- CPU와 주 기억장치 사이에 물리적으로 존재하는 버퍼 형태의 고속 기억장치

- 사용 이유 : CPU와 주기억장치 사이의 속도 차이를 완화시킴

- 캐싱 알고리즘 : LFU / LRU , hit율이 높을수록 cache의 기능이 향상

- 캐시 메모리의 종류

- L1 cache (Level 1/Primary) : 프로세서 core에 내장된 cache 메모리

- L2 cache (Level 2/Secondary) : 프로세서 안에 내장된 것이 아니라 메인보드나 카트리지에 장착되어있음

🍇종류

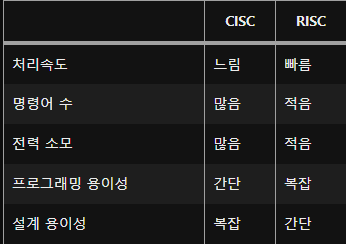

- 명령어 집합 형태에 따른 구분

- CISC (Complex Instruction Set Computer)

- 직접 계산 실행이 가능하다.

- 연산할 값을 메모리 또는 레지스터에 담아두고 한다.

- RISC (Reduced Instruction Set Computer)

- 최소 명령어 집합으로 하드웨어를 단순화 시키고 속도를 높인다

- 오직 레지스터로만 연산을 수행한다.

- load-store 구조 (load : memory -> register / store : register -> memory)CPU 설계 구조 상 2가지 방향

- CISC

명령어 수가 많고 다양한 가변길이의 명령어를 갖는 CPU 구조

상대적으로 많은 전력을 소모한다.

예) Intel 프로세서 - RISC

단순하고 고정 길이의 명령어 집합을 제공하여, 크기를 줄이고 속도를 높이고자 한 CPU 구조

하드웨어 만으로 실행시켜 속도를 높이는 구조

예) 라즈베리파이

- CISC

- CISC (Complex Instruction Set Computer)

출처

K-Digital-Training: 리눅스 시스템 및 커널 전문가 과정

http://www.ktword.co.kr/index.php