1.3 시스템의 구성

1.3.1 CPU와 기억장치의 접속

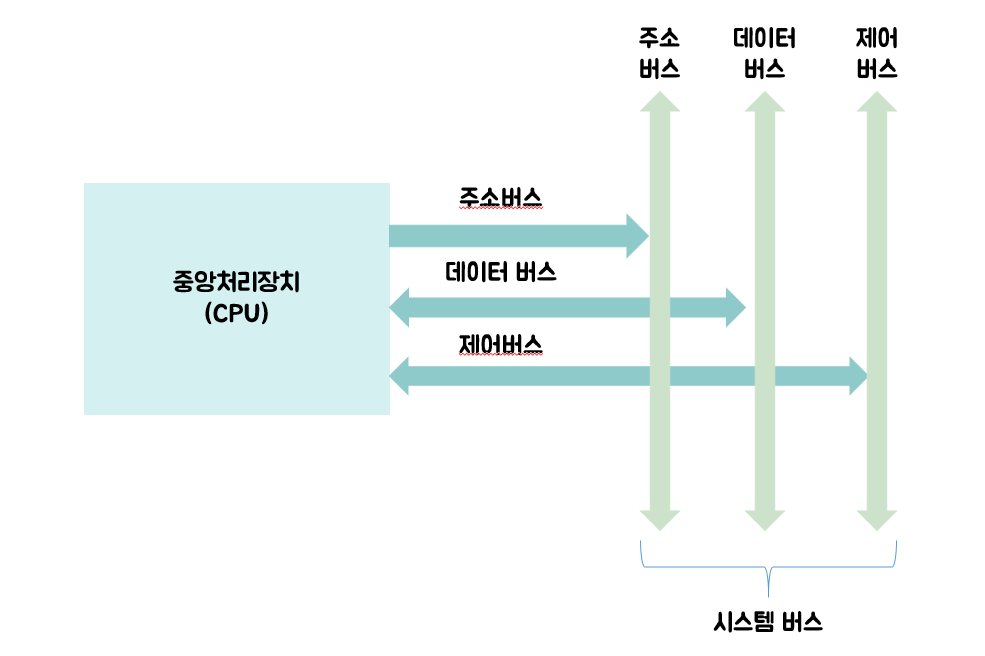

시스템 버스(System Bus)

-

CPU와 시스템 내의 다른 요소들 사이에 정보를 교환하는 통로

-

기본구성

-주소 버스(Address Bus)

-데이터 버스(Data Bus)

-제어 버스(Control Bus)주소 버스(Address Bus)

-

CPU가 외부로 발생하는 주소 정보를 전송하는 신호 선들의 집합

-

주소 선의 수는 CPU와 접속될 수 있는 최대 기억 장치 용량을 결정

ex) 주소 버스의 비트 수 = 16비트라면,

최대 개의 기억 장소들의 주소지정 가능데이터 버스(Data Bus)

-

CPU가 기억장치 혹은 I/O 장치와의 사이에 데이터를 전송하기 위한 신호 선들의 집합

-

데이터 선의 수는 CPU가 한 번에 전송할 수 있는 비트 수를 결정

ex) 데이터 버스 폭 = 32 비트라면, CPU와 기억 장치 간의 데이터 전송은 한 번에 32비트씩 가능제어 버스(Control Bus)

-

CPU가 시스템 내의 각종 요소들의 동작을 제어하기 위한 신호 선들의 집합

ex)

- 기억장치 읽기/ 쓰기(Memory Read/Write)신호

- I/O 읽기/ 쓰기(I/O Read/Write)신호

- 인터럽트(Interrupt) 신호

- 버스제어(Bus Control)신호CPU와 시스템 버스 간의 접속

- 주소버스: 단방향성(Unidirectional)

-주소는 CPU로부터 기억장치 혹은 I/O 장치들로 보내지는 정보 - 데이터 버스, 제어 버스: 양방향성(Bidirectional)

-읽기와 쓰기 동작을 모두 지원

- 주소버스: 단방향성(Unidirectional)

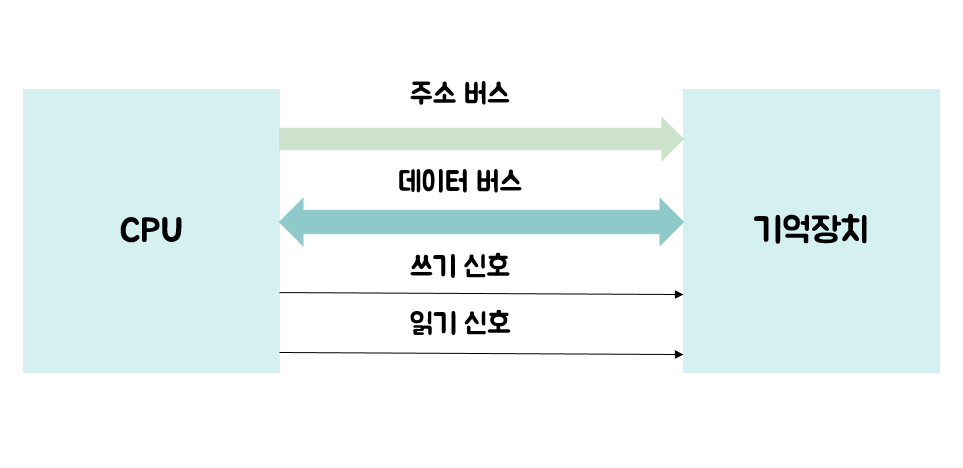

CPU와 기억장치 간의 접속

- 필요한 버스 및 제어신호

-주소 버스

-데이터 버스

-제어 신호: 기억장치 읽기(Memory Read)신호, 기억장치 쓰기(Memory Write) 신호

-

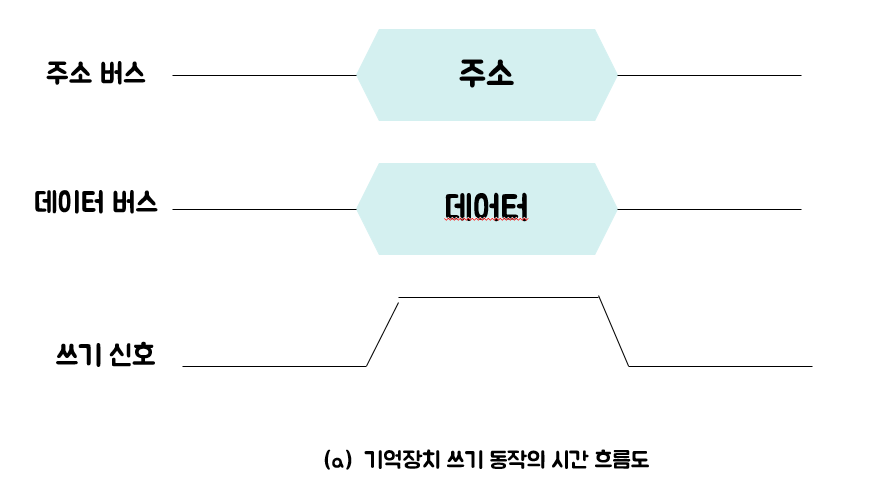

기억장치 쓰기 동작: CPU가 데이터를 저장할 기억 장소의 저장할 데이터를 각각 주소 버스와 데이터 버스를 통하여 보내는 동시에, 쓰기 신호를 활성화

-

기억장치 쓰기 시간(Memory Write Time): CPU가 주소와 데이터를 보낸 순간부터 저장이 완료될 때까지의 시간

-

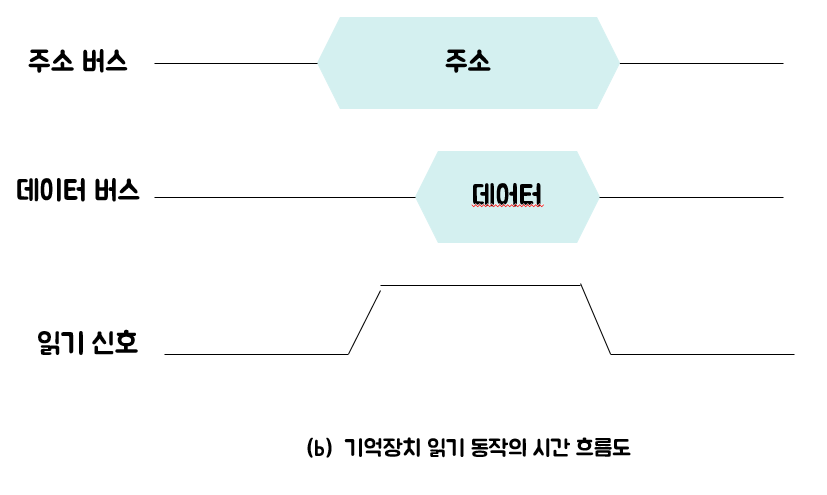

기억장치 읽기 동작

-CPU가 기억장치 주소를 주소 버스를 통하여 보내는 동시에, 읽기 신호를 활성화

-일정 지연 시간이 경과한 후에, 기억장치로부터 읽혀진 데이터가 데이터 버스 상에 실리고, CPU는 그 데이터를 버스 인터페이스 회로를 통하여 읽음

-

기억장치 읽기 시간(Memory Read Time): 주소를 발생한 시간부터 기억장치의 데이터가 CPU에 도착할 때까지의 시간

기억장치 액세스(읽기/쓰기) 동작의 시간 흐름도