[OSTEP] 19. Translation Lookaside Buffers

이 포스팅은 Operating Systems: Three Easy Pieces, Remzi H. Arpaci-Dusseau & Andrea C. Arpaci-Dusseau을 읽고 개인 학습용으로 정리한 글입니다.

CH 22. 페이징: 더 빠른 변환 (TLB)

변환-색인 버퍼(translation-lookaside buffer, TLB)

-

자주 참조되는 가상 주소-물리 주소 변환 정보를 저장하는 주소-변환 캐시(address-translation cache)

-

칩의 메모리 관리부(memoty-management unit, MMU)의 일부

-

가상 메모리 참조 시, 하드웨어는 먼저 TLB에 원하는 변환 정보가 있는지를 확인

-> 만약 있다면 페이지 테이블을 통하지 않고 변환을 빠르게 수행한다

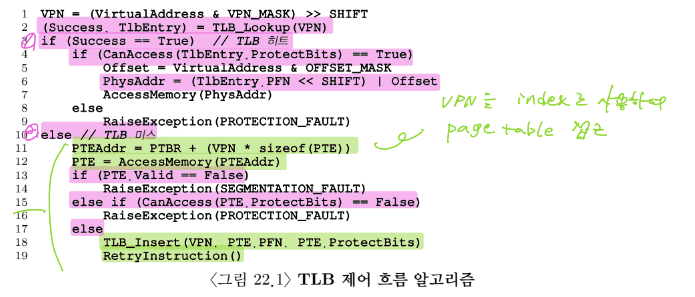

1. TLB의 기본 알고리즘

- 주소 변환부가 단순히 선형 페이지 테이블과 하드웨어로 관리되는 TLB로 구성된 경우

- 가상 주소에서 가상 페이지 번호(VPN) 추출, 해당 VPN의 TLB 존재 여부 검사

-> 만약 존재하면 TLB 히트, 존재하지 않는다면 TLB 미스

TLB 히트인 경우

- 해당 TLB 항목에서 페이지 프레임 번호(PFN) 추출

-> 해당 페이지에 대한 접근 권한 검사

-> 오프셋과 합쳐서 물리 주소(PA) 구성

-> 메모리에 접근

TLB 미스인 경우

-

하드웨어가 변환 정보를 찾기 위해 페이지 테이블에 접근

-> 프로세스가 생성한 가상 메모리 참조가 유효한지 검사

-> 해당 페이지에 대한 접근 권한 검사

-> 해당 변환 정보를 TLB로 읽어들임 -

TLB가 갱신되면 하드웨어는 명령어를 재실행

-

TLB 미스가 많이 발생할수록 메모리 접근 횟수가 많아진다

-> 메모리 접근 연산은 매우 시간이 오래 걸린다

-> TLB 미스 발생하는 경우를 최대한 피해야

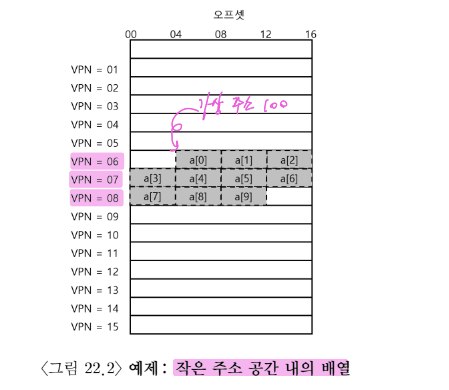

2. 예제: 배열 접근

-

가상 주소 100번지부터 10개의 4바이트 크기의 정수를 저장하는 배열이 있다

-

가상 주소 공간 8비트, 페이지 크기 16 바이트

-> 오프셋 4비트 (페이지 크기 2^4 Bytes)

-> VPN 4비트 (가상 주소 공간 내 페이지 개수 2^8 / 2^4 = 2^4)

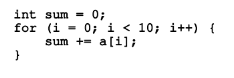

- 배열 원소의 합을 구하는 코드

정수 배열에 대한 메모리 접근

-

변수 i, sum, 명령어를 위한 메모리 접근 무시

-

TLB 완전히 초기화되어있다고 가정

-

a[0] 접근 (가상 주소 100번)

-> 하드웨어는 VPN을 추출(06)

-> 하드웨어는 TLB에서 해당 VPN 검색

-> TLB 미스

-> 해당 VPN 06에 대한 PFN을 페이지 테이블에서 찾아 TLB 갱신 -

a[1] 접근

-> a[0]와 같은 페이지에 존재

-> TLB 히트 -

a[2] 접근

-> a[0], a[1]과 같은 페이지에 존재

-> TLB 히트 -

a[3] 접근 -> TLB 미스

-

a[4], ..., a[6] 접근 -> TLB 히트

-

a[7] 접근 -> TLB 미스

-

a[8], a[9] 접근 -> TLB 히트

공간 지역성

- 배열의 항목들이 페이지 내에서 서로 인접

-> 배열이 처음으로 접근되었지만, 페이지의 첫번째 항목을 접근할 때만 TLB 미스 발생

-> 공간 지역성(spatial locality)으로 TLB 성능 개선되었음

페이지의 크기

- 페이지의 크기는 TLB의 효용성에 매우 중요한 역할

-> 페이지의 크기가 증가하면 TLB 미스 횟수가 줄어든다

시간 지역성

- 만약 예제 프로그램이 루프 종료 후에도 배열을 사용한다면, 성능은 더욱 개선될 것