- 페이징의 두번째 문제점

페이지 테이블이 크면 많은 메모리 공간을 차지

ex)

- 페이지 크기 4KB(2바이트)

- 주소공간 크기: 32 비트(2바이트)

- 가상 페이지 개수 = 주소공간 / 페이지 크기

- 2 / 2 = 2 (약 백만개)

21.1 간단한 해법 : 더 큰 페이지

페이지 크기를 증가시키면 됨

위의 예시에서 페이지 크기를 16KB로 올리면

- 페이지 크기 16KB(2 바이트)

- 주소공간 크기: 32 비트(2 바이트)

- 가상 페이지 개수: 2

부작용

- 내부단편화: 페이지 내부 낭비 공간 증가

23.2 하이브리드 접근 방법 : 페이징과 세그멘트

두개의 심장 어쩌고

페이징과 세그먼트의 장점을 합쳐서

ex) 1KB 크기 페이지를 같는 16KB 주소공간

프로세스의 전체 주소 공간을 위해 하나의 페이지 테이블을 두는 대신,

논리 세그멘트 마다 따로 페이지 테이블을 둠

코드, 힙, 스택 세그멘트에 대하 페이지 테이블을 각각 두는것

베이스 바운드 리미트 레지스터가 있다.

여기서 베이스는 새그멘트 시작 주소가 아니라 세그멘트의 페이지 테이블의 시작 주소를 갖음

바운드는 페이지 테이블의 끝을 나타냄

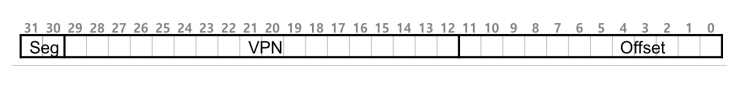

- 소속 세그멘트를 나타내는 상위 두비트(세그멘트 구분)

- TLB 미스 발생 시

- 세그멘트 비트를 사용해 어떤 베이스와 바운드 쌍을 사용할지 결정

- HW는 레지스터에 들어 있는 물리 주소를 VPN과 다음 과같은 형식으로 조작하여 페이지 테이블 항목(PTE)의 주소 얻 음

문제

- 여전히 세그멘테이션을 사용

- 하이브리드 기법은 외부 단편화 유발(페이지 크기 제한 X, 다양한 크기를 갖음)

23.3 멀티 레벨 페이지 테이블

세그멘테이션 사용X 페이지 테이블 크기 줄이는

방법

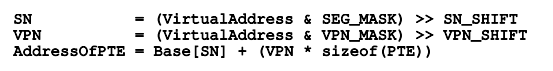

멀티 레벨 페이지 테이블 에서는 선형 페이지 테이블을 트리구조로 표현

개념

- 페이지 테이블을 페이지 크기의 단위로 나눔

- 페이지 테이블의 페이지가 유효하지 않은 항목만 있으면 해당 페이지 할당 X

- 페이지 디렉터리 자료구조 사용해 페이지 테이블 각 페이지의 할당 여부, 위치 파악

- 페이지 디렉터리: 페이지 테이블을 구성하는 각 페이지의 존재 여부와 위치정보 갖고 있음

- 선형은 가운데 공간이 낭비중

- 페이지 디렉토리 사용시 미사용 페이지는 할당 X

- 페이지 디렉토리: 페이지 디렉토리 항목(PDE)으로 구성

- PDE는 페이지 테이블의 한 페이지

- PDE는 유효 비트, PFN 으로 구성

장점

- 사용된 주소 공간의 크기에 비례해 페이지 테이블 공간이 할당

- 작은 페이지 테이블로 주소공간 표현 가능

- 페이지 테이블을 페이지 크기로 분할해 메모리 관리가 용이

- 패이지 테이블 할당/확장 시 OS가 free 페이지 풀에 있는 빈페이지 가져다 씀

단점

- 추가 비용 발생

- TLB 미스 시 주소 변환을 위해 두번의 메모리 로드 발생(페이지 디렉터리, PTE 접근 각각 한번씩), 선형은 한번만 하면 됨

- 복잡도

- 선형 테이블 보다 테이블 검색이 복잡함

23.4 역 페이지 테이블

여러가지 페이지 테이블(시스템의 프로세스당 하나씩) 대신 시스템에 단 하나의 페이지 테이블만 둠

- 페이지 테이블은 물리 페이지를 가상 주소 상의 페이지로 변환

- 역 페이지 테이블 각 항목은 해당 물리 페이지를 사용중인 프로세스 번호, 해당 가상 페이지 번호 가짐

- 탐색 속도 향상 위해 해시 테이블 사용

23.5 페이지 테이블을 디스크로 스와핑 하기

모든 페이지 테이블을 메모리에 상주시키기에는 너무 클 수 있음

- 어떤 시스템들은 페이지 테이블을 커널 가상 메모리에 존재 시킴

- 시스템 메모리가 부족할 경우 페이지 테이블들을 디스크로 스왑