Day-8

2장 전자 회로의 조합 논리

-컴퓨터는 어떤 논리로 비트를 다루는가

4. 논리 게이트

-

1960년대 중반 텍사스 인스트루먼츠라는 회사에서 5400과 7400 집적 회로(IC)라는 패밀리라는 칩을 발표 했고 이 칩들에는 논리 연산을 수행하는 회로가 미리 들어가 있으며 이런 회로를 논리 게이트(logic gate)또는 게이트라고 부름

-

게이트를 사용하면 하드웨어 설계자가 밑바닥부터 모든 회로를 설계할 필요 없이, IC를 선으로 연결해 복잡한 회로를 쉽게 만들 수 있다.(예. 배관공)

-

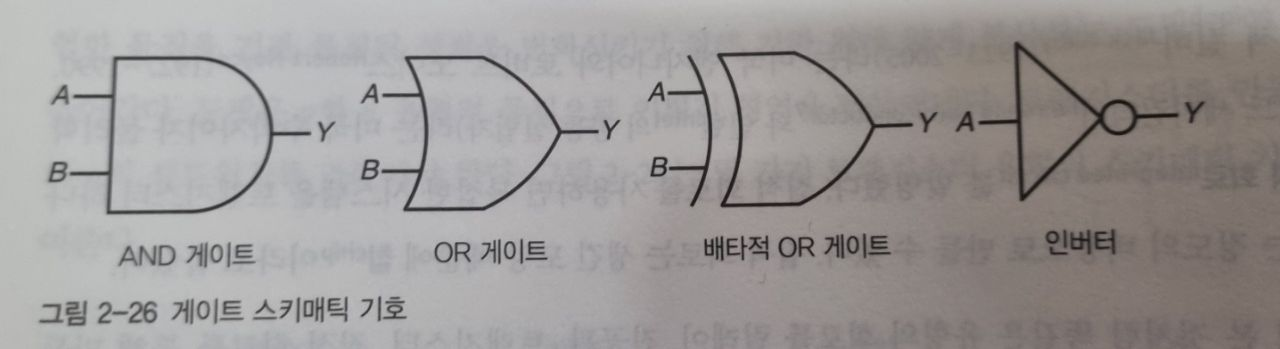

논리 설계자도 AND 게이트, OR게이트, XOR 게이트, 인버터(inverter)가 들어 있는 ‘박스’를 얻을 수 있다

-

인버터 기호에서 중요한 부분은 O부분이며, 인버터 기호는 인버터를 다른 논리 게이트와 별도로 독립적으로 사용할 때만 쓰인다.

- 삼각형(버퍼)부분은 입력을 출력으로 전달만 하기 떄문.

-

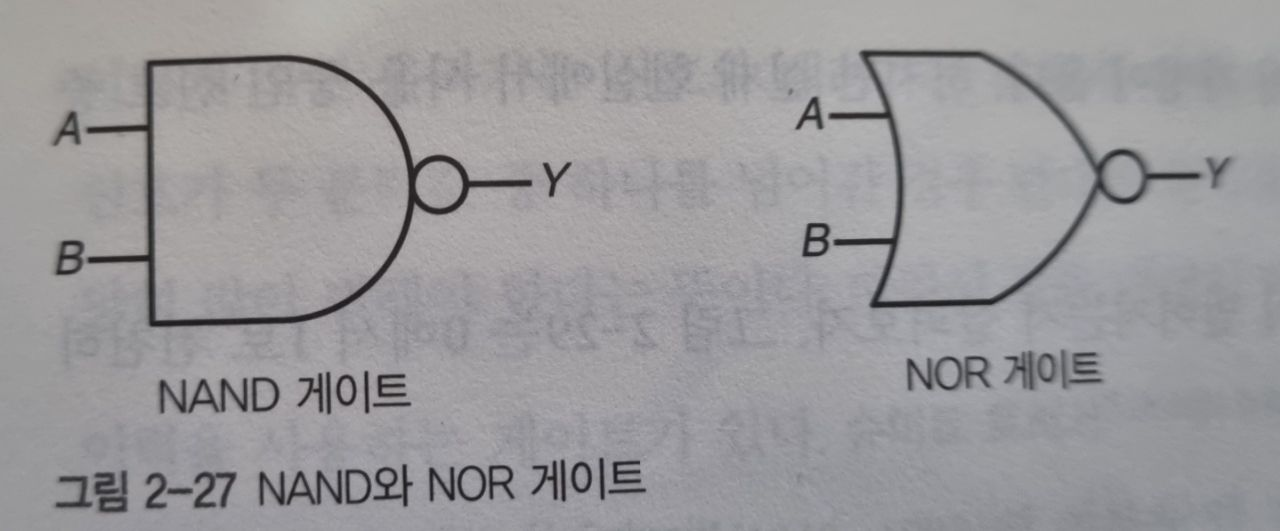

하지만 AND나 OR 게이트가 가장 효율적인 게이트는 아니다.

- NAND나 NOR 회로 출력에 트랜지스터를 덧붙여서 출력을 반전시켜야 하기 떄문.

- 가격이 더 비싸고 반응 속도도 더 느리며, 전력도 더 많이 소모됨

- NAND나 NOR에 붙은 반전이 논리 회로 설계에는 문제가 되지 않음.

- NAND와 NOR의 두 입력을 같은 입력에 연결하면 인버터를 만들 수 있다.

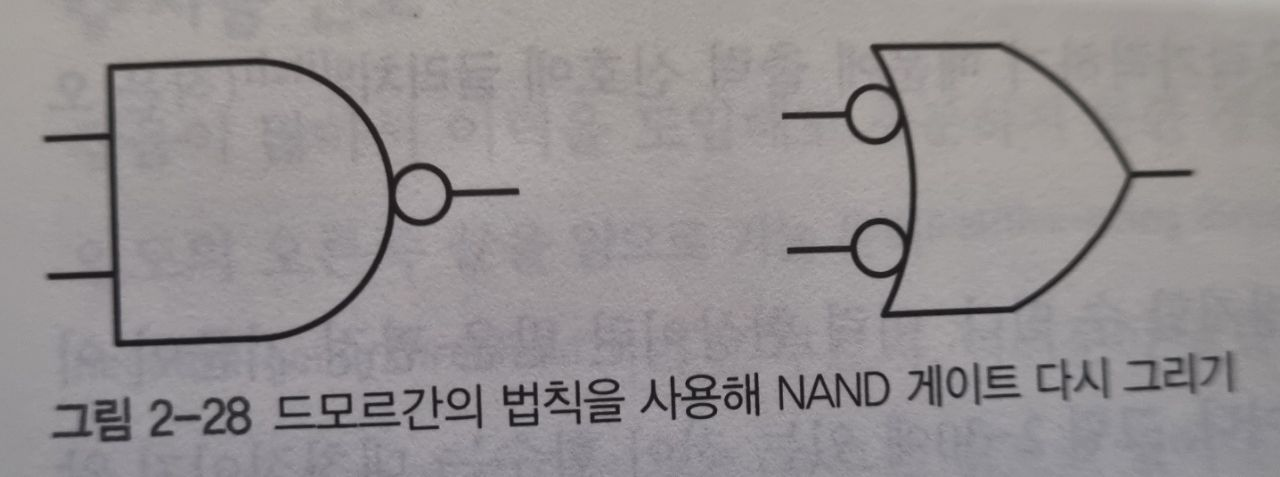

- 드모르간의 법칙에 의해 NAND는 OR의 반전 시킨 것과 같음

이력 현상을 활용한 잡음 내성 향상

- 디지털 장치를 사용하면 판정 기준애 의해 잡음 내성을 얻을 수 있다. 하지만 디지털로 전환하는 것만으로 충분하지 않는 경우가 있다.

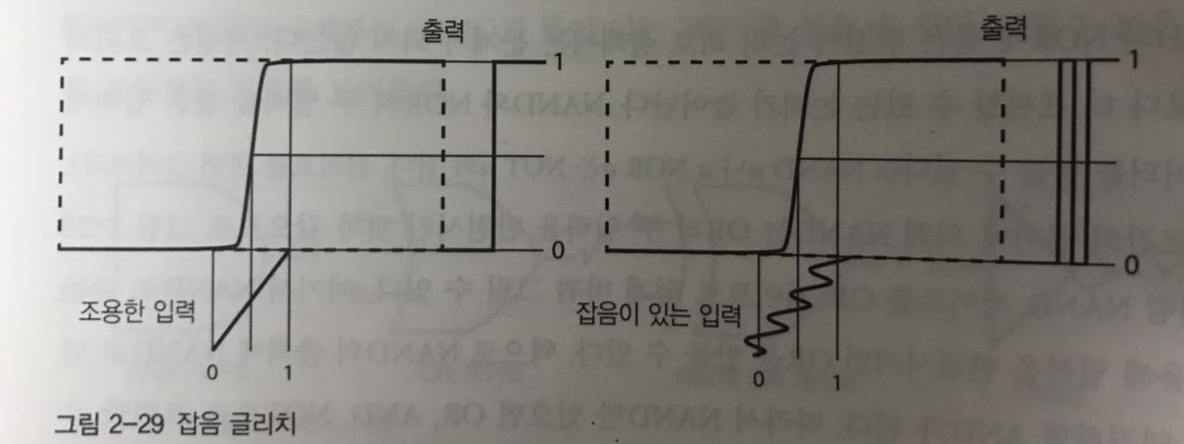

- 게이트를 연결하는 경우에는 논리 신호가 0에서 1로 순간적으로 바뀌고, 1에서 0으로 순간적으로 바뀐다는 가정이 가능하지만, 실제 현실에서는 신호 중 천천히 변하는 신호가 많음

- 그림의 왼쪽 신호는 잡음이 없지만, 오른쪽 그림은 잡음이 있다.

- 이로 인해 신호가 문턱값을 여러 번 오락가락해 출력 신호에 글리치(Glich)가 생깁니다.

- 글리치는 이력 현상으로 방치 할 수 있음

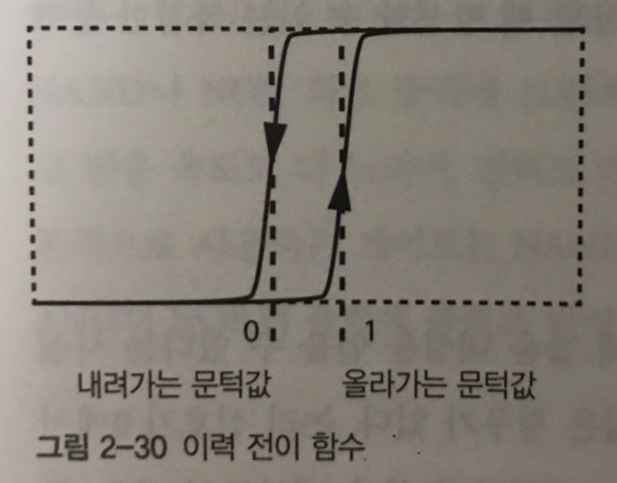

- 이력 현상(hysteresis)

- 이력 현상은 판정 기준이 이력에 따라 달라진다는 의미

- 이력 전이 함수는 아래 그림처럼 이전 출력이 0이면 오른쪽 곡선, 출력이 1이면 왼쪽 곡선을 사용

- 올라가는 신호와 내려가는 신호에 대해 다른 문턱값이 생기면, 신호가 하나의 문턱값을 넘어 반대쪽 문턱값을 지나 출력이 반전되기 위해 값이 상당히 많이 변해야 함

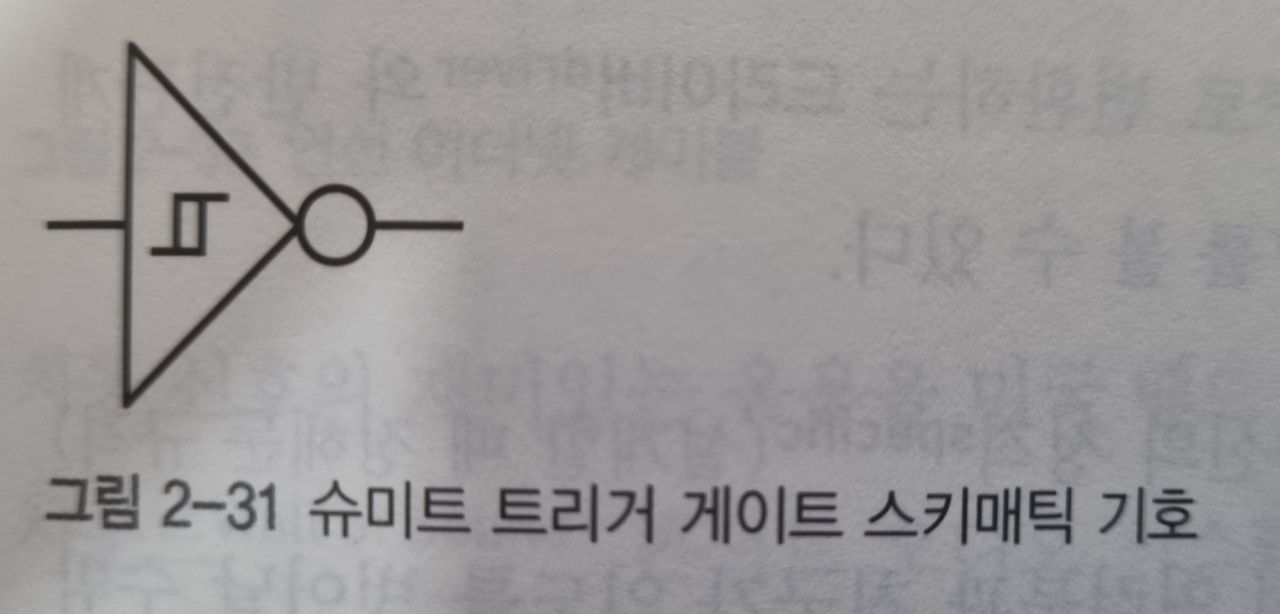

- 슈미트 트리거(Schmitt trigger)

- 위와 같은 이력을 사용하는 게이트

- 일반적인 게이트 보다 복잡히기 때문에 정말 필요한 경우에만 사용

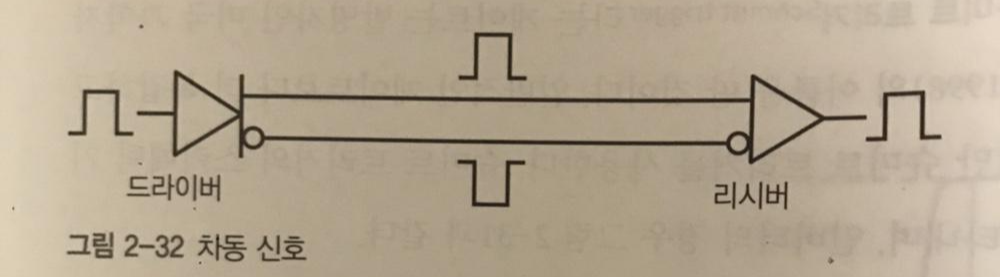

차동 신호

- 잡음이 많은 이력을 도입해도 충분하지 못한 경우에 사용하는 방식

- 서로 반대되는 극성을 가진 2개의 신호를 이용한 전송 방식이며 반전 관계

- 그림에서 입력 신호를 반전관계로 출력들로 변환하는 드라이버, 반전관계를 입력받아 단일 신호로 만들어 주는 리시버를 볼 수 있다.

- 차동 신호도 한계는 있다. 너무 많은 잡음으로 인해 자신의 정격(설계할 때 정해둔 규격) 작동 범위를 넘어가게 될 수 있다.

- 공통 모드 판별비, CMMR Common-mode Rejection Ratio

- 공동 모드 판별비는 부품 정격 중 하나로 정리 가능한 잡음의 양을 표시합니다.

- 공동 모드라고 부르는 이유는 두 신호에서 공통인 잡음을 가리키기 때문

- 차동 신호는 전화선 등 다양한 곳에서 사용함 하지만 전차가 처음 나왔을 때, 전차에서 잡음이 많이 나와 전화 신호에 간섭했기 때문에 발명가 그레이엄 벨은 연선 케이블링을 발명 했는데, 한 쌍의 선을 꼬아 전지적으로 연인이 서로 허리에 손을 두르는 것 같은 효과를 만들어냄

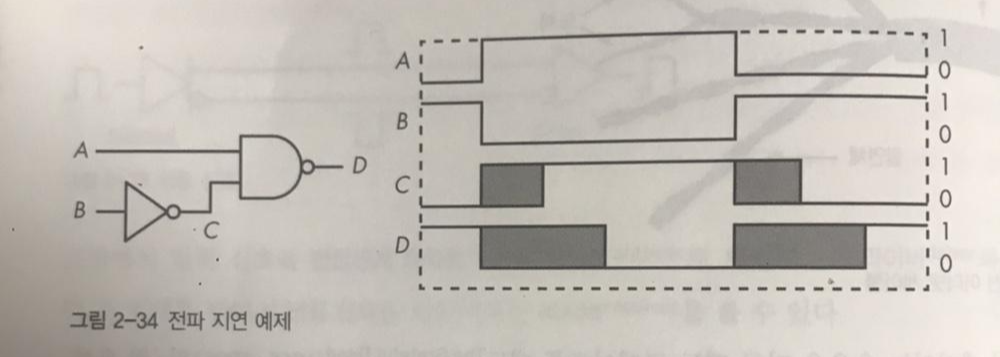

전파 지연

- 전파 지연은 입력 신호를 받고서 출력 결과를 나타낼 때까지 걸리는 시간을 의미함

- 전파 지연의 실제 지연은 정확한 값은 아니고 최대 지연과 최소 지연 사이의 어떤 값

- 전파 지연은 논리 회로의 최대 속도를 제한하는 요소 중 하나로, 정상적으로 작동하기 위해서는 최악의 경우를 가정해서 설계해야 함

- 회색 영역은 전차 지연으로 인해 출력을 신뢰할 수 없는 구간

- 출력이 회색 영역의 맨 왼쪽처럼 나온다고 보장할 수 없으며, 게이트를 연결할 수록 회색 영역의 길이가 길어짐

- 전파 지연 시간은 처리 기술에 따라 많이 달라짐

- 7400 계열 같은 개별적 부품은 10나노초(1억 분의 1초) 범위에 속함

- 마이크로프로세서 같은 현대 부품은 피코초(1초 분의 1초) 범위에 속함

- 어떤 전자 부품의 정격표(데이터시트) 지연 시간은 tPHL tPLH로 표시함

- PHL은 1에서 0, PLH는 0에서 1로 갈 때 결리는 지연 시간

출력 유형

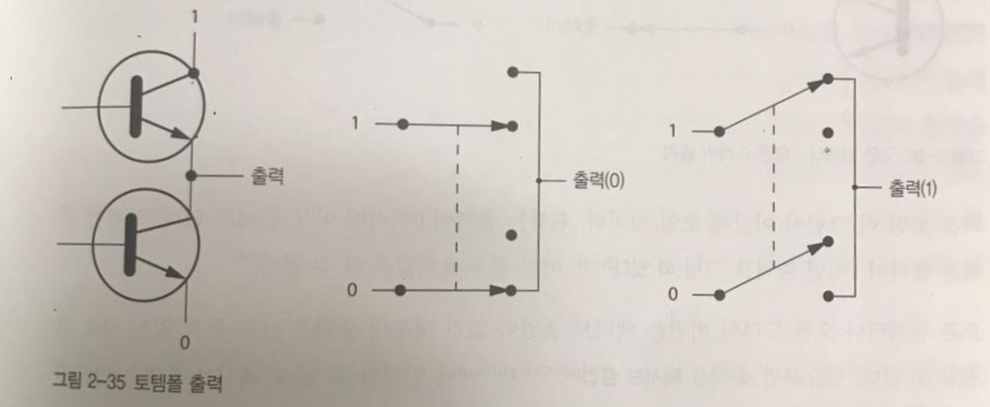

토템폴 출력

- 일반적인 게이트 출력은 토템폴(Totem pole) 이라고 부름

- 토템폴은 트랜지스터가 토템폴처럼 세로고 늘어져 있어 붙은 이름

- 왼쪽 스키매틱(회로도)의 위쪽 스위치는 출력 1을 얻기 위해 출력과 높은 논리값 1을 연결하기 때문에 액티브 풀업이라고 불림

- 토템폴 출력은 서로 연결할 수 없습니다. 전자 회로에서 입력 0은 음극,1은 양극에 연결 되기 때문

- 두 출력을 연결하면 음극과 양극이 직접 연결되는 효과가 나타나 불이 나거나 터질 수 있다

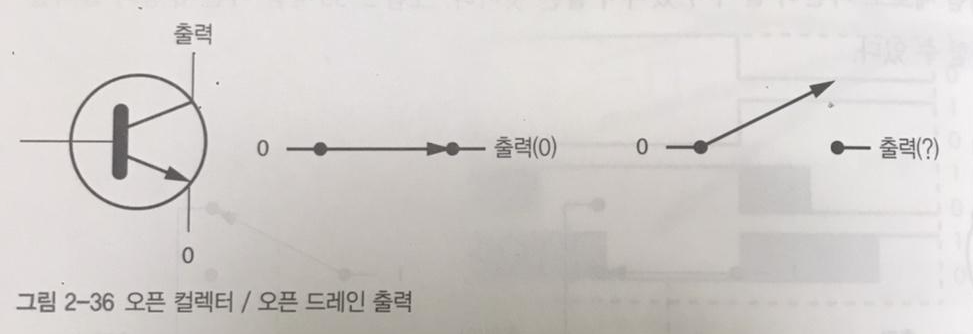

오픈 컬렉터 출력

- 오픈 컬렉터, 오픈 드레인 출력의 스키매틱(회로도), 스위치 모델은 아래 그림과 같음

- 그림을 보면 0출력은 아무 문제가 없어 보이지만, 1출력은 그냥 떠있어 출력을 패시브 풀업에 연결할 수 있으며, 필요하면 출력을 패시브 풀업에 연결 할 수 있음

- 패시브 풀업은 풀업 저향을 논리적으로 1값을 공급해주는 공급 전압에 연결한 것

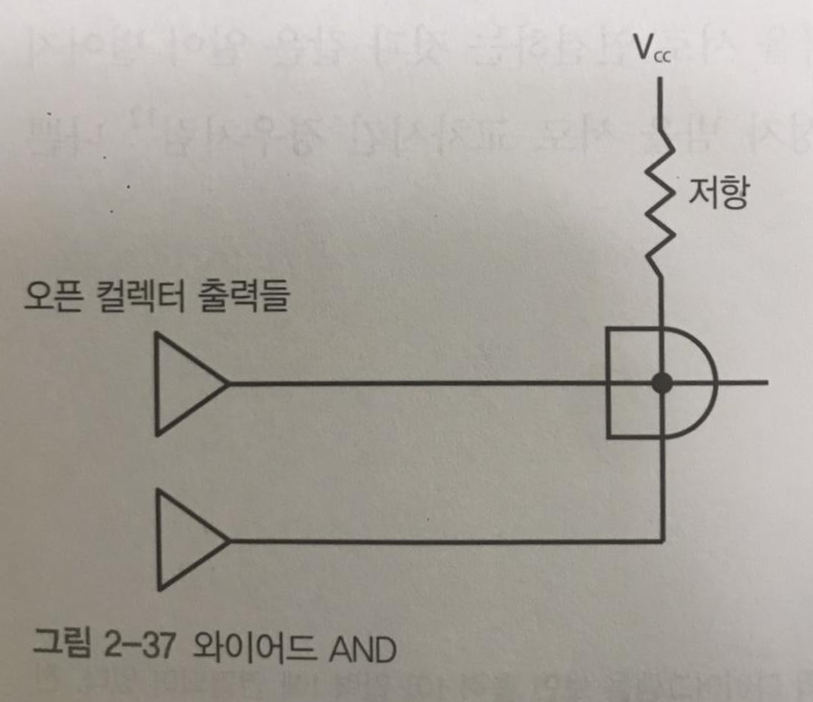

- 와이어드 AND

- 오픈 컬렉터 여러 개와 풀업을 사용하면 와이어드 AND를 만들 수 있음

- 기본적 원리는 위의 풀업 저항과 같음, 그러나 오픈 컬렉터 출력 값 중 출력이 0인 값이 있다면, 전체의 출력도 0이 되고 모두 1을 출력하면 전체 출력도 1 와이어드는 여러 입력이 있는 AND 게이트를 사용하지 않고도 AND 계산이 가능 함

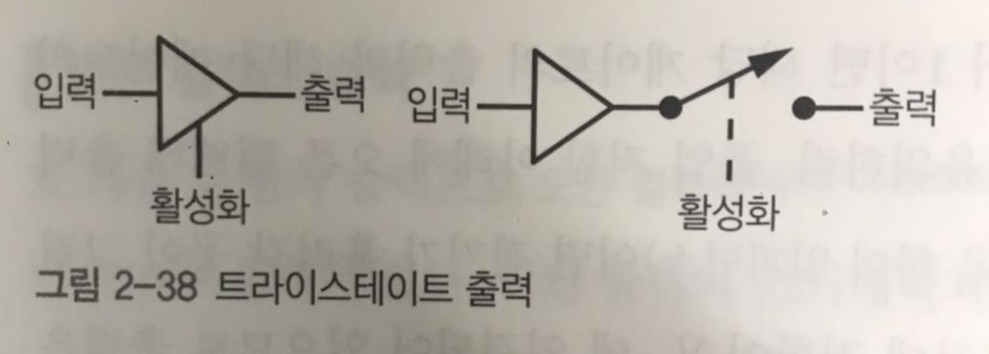

트라이스테이트 출력

- 오픈 컬렉터 회로를 사용하면 출력을 서로 연결할 수 있지만, 엑트브 풀업처럼 응답이 빠르지는 않음

- 앞의 두 가지 상태만 가진 것이 아닌 꺼진 상태를 포함해 3가지 상태를 가진 트라이스테이트 출력을 사용

- 그림처럼 키고 끄기 위한 추가 입력을 활성화라고 함

- 꺼진 상태를 hi-Z라고도 하며, Z는 임피던스라는 뜻도 있음

- 임피던스(Impedance)

- 저항을 수학적으로 복잡하게 부르는 이름