9.1 물리주소 및 가상주소 방식

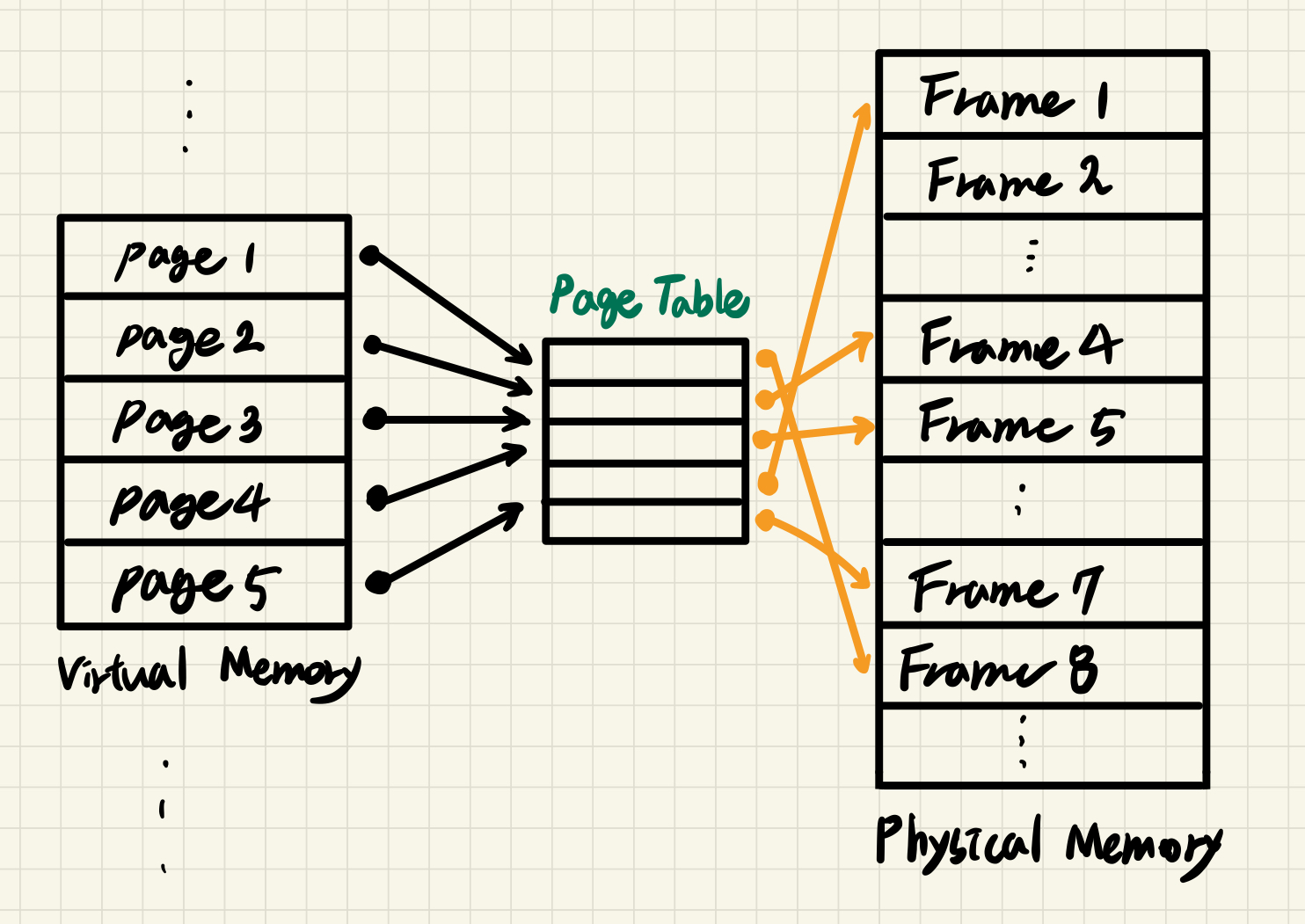

물리 주소 방식 - CPU가 각 바이트가 가지는 고유 물리주소(PA:Physical Address)에 접근하여 메모리에 접근하는 방식

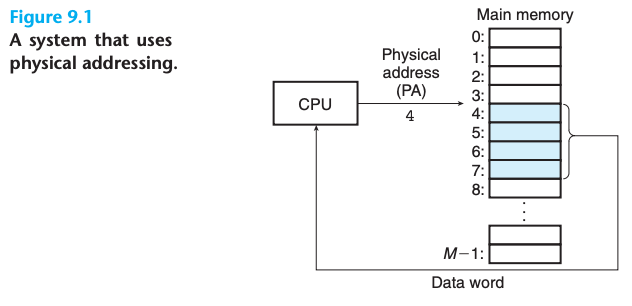

가상 주소 방식 - CPU의 가상주소지정으로 가상주소(VA)를 생성해서 메인메모리에 접근, 메모리로 보내지긴전에 적절한 물리주소로 변환해서 사용된다.

주소 번역 - 가상 주소(VA)를 물리주소(PA)로 번역하는 작업. CPU내 메모리 관리 유닛(MMU)가 메인 메모리에 저장된 참조 테이블을 통해 가상 주소를 번역한다.

9.2 주소공간

주소 공간 - 비음수 정수 주소의 정렬된 집합

{ 1, 2, 3, 4, ... , N - 1 }선형 주소 공간 - 주소공간의 정수가 연속적인 경우.

가상 주소 공간 - 가상 메모리를 갖는 시스템에서 특정 바이트 만큼 가상의 주소를 생성하는 공간.

물리 주소 공간 - 컴퓨터 시스템이 시스템 내에서 M바이트 만큼 가상 메모리와 대응되는 주소 공간.

주소 공간은 데이터 객체와 그것들의 주소를 명확하게 구분해주기 때문에 중요하다.

9.3 캐싱 도구로서의 VM

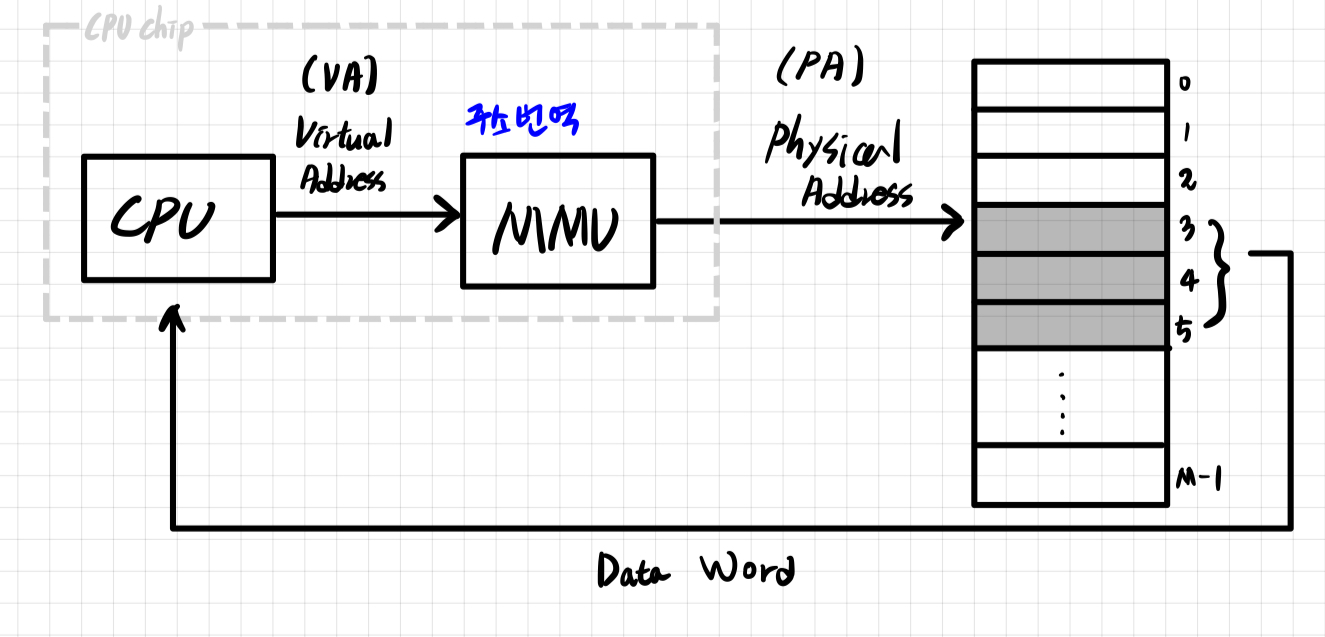

가상메모리는 디슽크에 N개의 바이트 크기의 셀 배열로 구성된다. 바이트는 특정한 가상 주소를 가지며, 배열의 인덱스로 작용한다. 메모리 계층 구조 내부에 있는 캐시는 블록 단위로 분할 되며, 디스크와 메인 메모리사이 다리 역할을 한다. 이때 VM system에서 규정된 사이즈의 블록 단위들을 가상 페이지라고 한다.

물리 피에지 또한 물리 페이지로 분리되어 사용된다. 물리 페이지의 경우 물리 프레임이라고도 불린다.

가정 페이지의 집합은 언제나 아래 3가지 상태중 하나의 상태만을 가진다.

Unallocated: 아직 시스템에 의해 할당되지 않은 상태.

Cached: 현재 물리 메모리에 캐시되어 할당된 페이지들.

Uncached: 물리 메모리에 캐시되지 않은 할당된 페이지들.9.3.1 DRAM 캐시의 구성

DRAM 캐시 - 메인 메모리로 캐싱하는 VM 시스템 캐시를 말함.

SRAM 캐시 - CPU와 메인 메모리 사이의 캐시 메모리를 말함.

메모리 계층 구조에서 DRAM캐시의 위치는 DRAM이 구성된 방식에 영향을 받는다.

DRAM의 캐시 미스가 SRAM의 캐시 미스에 비하면 비용이 매우 비싸다.

→ DRAM의 캐시 미스는 DRAM보다 10만배 느린 디스크에서 처리되지만 SRAM의 캐시 미스는 디스크보다 빠른 DRAM 기반의 메인메모리 부터 지원을 받기 때문이다.

→ 더불어, 첫 번째 바이트를 읽는 비용이 연속적인 바이트를 읽는 비용보다 10만배 비싸기 때문에 더더욱 엄청난 미스 비용이 발생한다.

큰 비용으로 인해서 가상 페이지가 커지고 있

9.3.2 페이지 테이블

페이지 테이블 - 가상 페이지를 물리 페이지와 매핑하기 위해 물리 메모리에 저장된 자료구조의 조합. 주소 번역 하드웨어가 가상 주소를 물리주소로 변환할 때 해당 페이지 테이블을 참고한다.

9.3.3 페이지 적중

- CPU가 MMU에 가상 주소를 통해 주소 번역을 요청한다.

- 주소번역 하드웨어(MMU)는 가상주소에 해당하는 페이지 테이블 엔트리를 찾기위해 가상주소를 사용한다.

- 페이지 테이블의 해당 주소를 참조했을 때 페이지 테이블 엔트리의 유효비트를 통해 캐시되어 있음을 확인한다.

- 해당 페이지 테이블 엔트리이 캐시되어 있다면 페이지 테이블에 저장되어있는 워드의 물리 메모리 주소를 통해 워드의 물리 주소를 구성한다.

9.3.4 페이지 오류 ( 모호 )

DRAM의 캐시 미스를 페이지 오류라고 한다.

- 주소번역 하드웨어(MMU)는 가상 주소를 인덱스로 사용하여 페이지 테이블 엔트리를 참조하고 이때 페이지 테이블 엔트리의 유효비트가 0인것을 확인하고, 캐시되어 있지 않음을 확인 한다. 이를 통해서 페이지 오류 예외를 발생시킨다.

- 페이지 오류 예외는 커널 내 페이지 오류 예외 핸들러를 호출해서 물리 프레임에서 교체할 희생자 페이지를 선택한다.

- 선택된 희생자 페이지가 가리키는 페이지 테이블 엔트리를 수정해서 물리 메모리에 캐시되어 있지 않음을 표시한다.

- 커널은 희생자 페이지가 위치해있던 물리 페이지에 디스크에 있는 가상 페이지를 복사한다. 그리고 커널의 예외 핸들러는 이 가상 페이지이 대응하는 페이지 테이블 엔트리를 갱신하고 리턴한다.

- 리턴후, 오류 인스트럭션을 재시작하고, MMU에게 다시 같은 요청을 보낸다.

9.3.5 페이지 할당

운영체제가 가상 메모리의 새로운 페이지를 할당하면, 테이블 페이지의 유효 비트가 0이고 주소 필드가 NULL인 엔트리를 찾아 페이지의 주소를 삽입한다.

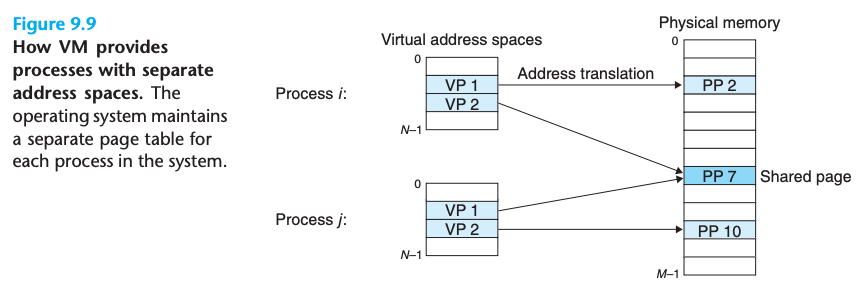

9.4 메모리 관리를 위한 도구로서의 VM

초기 시스템에서는 더 작은 가상 주소 공간을 사용했지만, 적은 공간이더라도 메모리 관리를 단순화하는 것이 가능했다. 그리고 메모리 관리 측면에서 페이징과 분리된 가상 주소 공간의 조합은 다양한 방식에서 영향을 끼쳤다.

- 링킹 단순화

- 코드와 데이터가 물리 메모리 내에 어디에 위치하던지 동일한 포멧을 사용

- 이러한 통일성으로 인해 링커의 설계와 구현이 단순해짐.

- 로딩 단순화

- 실행 파일과 공유 목적 파일을 메모리에 쉽게 로딩할 수 있음

- 목적 파일의 여러 섹션을 프로세스에서 로드하기 위해, 데이터 세그먼트를 가상페이지에 할당하고, 페이지 테이블이 이를 가리키게 하는 방식을 사용 → 메모리가 데이터를 복사할 필요없이 세그먼트를 사용할 수 있음 → 메모리 매핑

- 공유 단순화

9.5 메모리 보호를 위한 도구로서의 VM

모든 프로세스는 사적 메모리를 읽거나, 수정할 수 없어야 한다. 이런 관점에서 가상 주소 공간을 사용하면 메모리 보호가 가능해진다.

- CPU가 가상 주소를 만들때 페이지 테이블 엔트리를 참조하기 때문에 해당 엔트리에 캐싱 여부를 판단하는 비트처럼, 접근을 제어할 수 있는 허가 비트를 사용하는 방법을 사용할 수 있다.

- 허가 비트에 관계없이 접근하여 사항이 위반된다면, CPU는 보호 오류를 발생시키고

SIGSEGV시그널을 위반한 프로세스로 보내 커널 내에 예외 핸들러로 제어를 이동 시키고, 리눅스 쉘의 경우 이런 에러를Segmentation Falut라고 보고한다.