병렬 처리

: 컴퓨터 시스템의 계산 속도 향상을 목적으로 하여 동시 데이터 처리기능을 제공하는 광범위한 개념의 기술을 의미함.

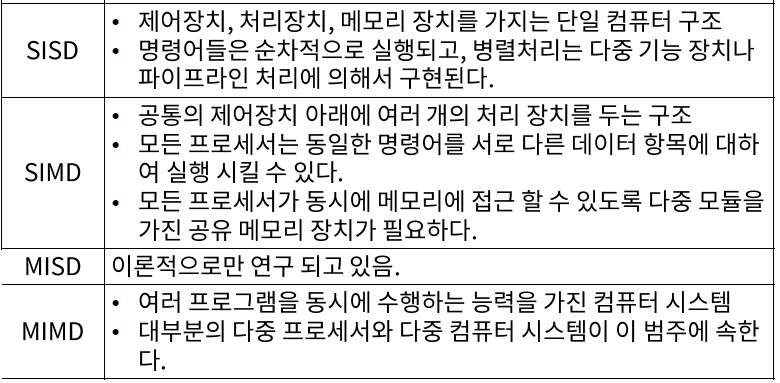

M.J Flynn의 분류 방법

: 동시에 처리되는 명령어와 데이터 항목 수에 의해 컴퓨터 시스템의 구조를 파악하려는 분류 방법 제안(명령어 흐름(instruction stream) -> 메모리로부터 읽어온 명령어의 순서, 데이터 흐름(data stream) -> 데이터에 대해 수행되는 동작)

- SISD -> 단일 명령어 흐름, 단일 데이터 흐름

- SIMD -> 단일 명령어 흐름, 다중 데이터 흐름

- MISD -> 다중 명령어 흐름, 단일 데이터 흐름

- MIMD -> 다중 명령어 흐름, 다중 데이터 흐름

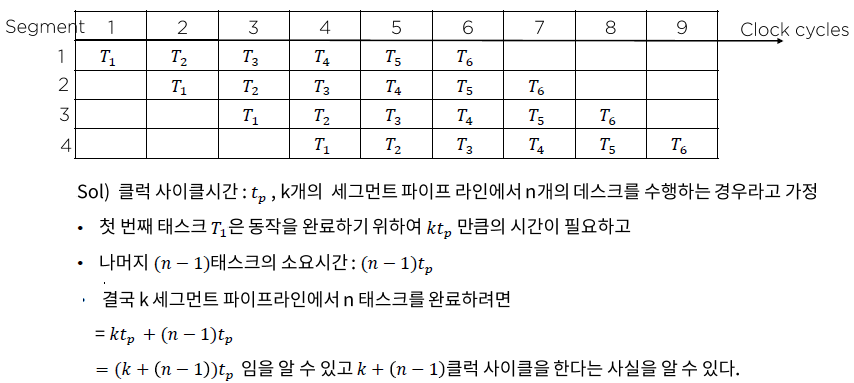

파이프 라인

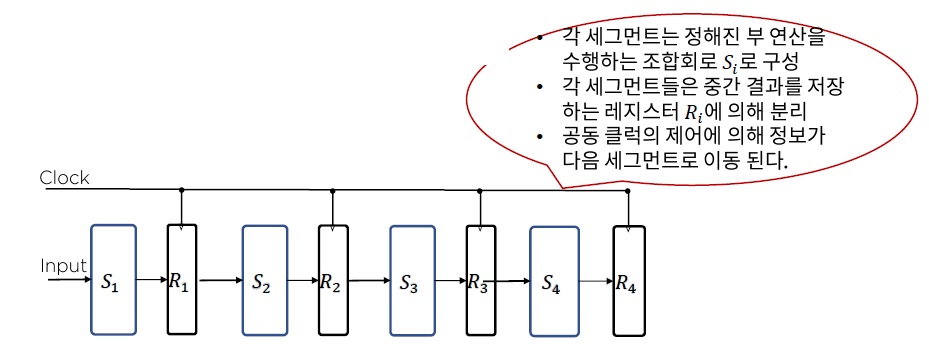

: 파이프라인의 동작은 공간, 시간표에 의해 설명 되는데, 이것은 시간에 대한 함수로서 세그먼트의 사용상황을 보여준다.

- 비 파이프라인의 경우

Pipeline의 구현

- 하나의 프로세스를 서로 다른 기능(Function)을 가진 여러 개의 서브프로세스(Subprocess)로 나누어 각 프로세스가 동시에 서로 다른 데이터를 취급하도록 하는 기법

- 각 세그먼트(segment)에서 수행된 연산 결과는 다음 세그먼트로 연속적으로 넘어가게 되어 데이터가 마지막 세그먼트를 통과하게 되면 최종적인 연산 결과를 얻게 된다 - 하나의 프로세스를 다양한 연산으로 중복시킬 수 있는 근간은 각 세그먼트마다의 레지스터이다.

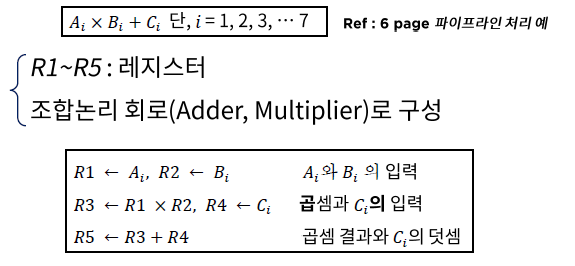

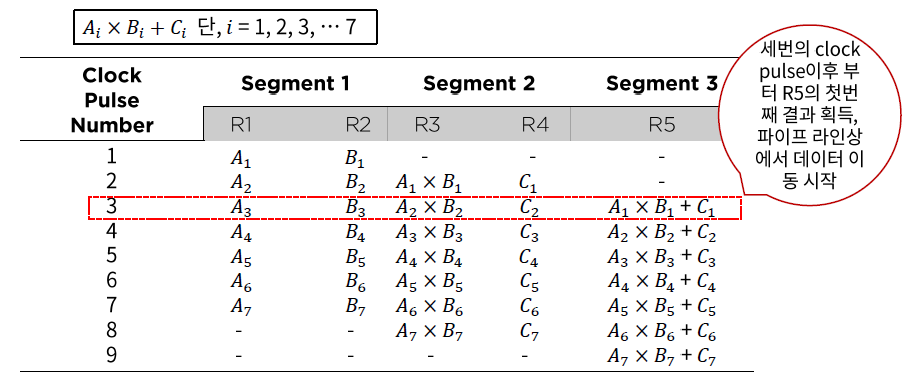

간단한 파이프 라인 구현 예제)

-

곱셈과 덧셈이 섞여 있는 다항식 연산

-

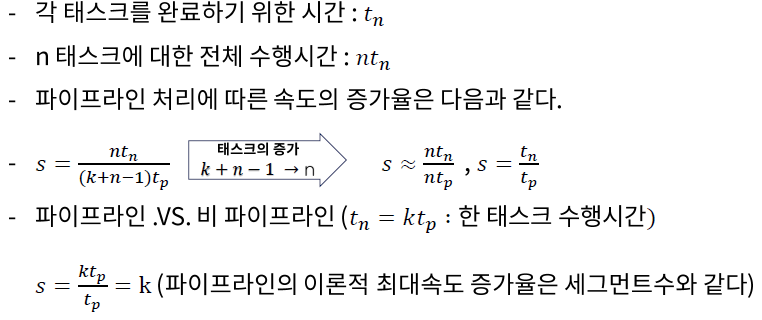

파이프 라인의 일반적 고찰

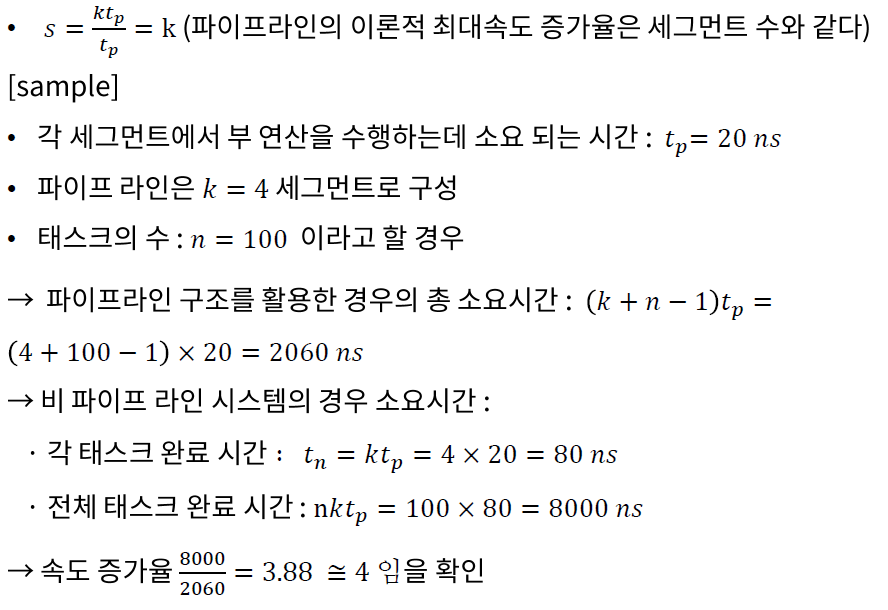

- 동일한 복잡도의 부연산들로 나뉘어지는 어떠한 연산 동작도 파이프라인 프로세서에 의해 구현될 수 있다. (세그먼트마다 처리시간이 다를 경우 효과적이지 못함)

- 파이프라인 기술은 매번 다른 데이터 집합을 동일한 태스크에 적용시켜 여러번 반복하는 응용에 효과적이다.

-

예시)

- 하지만 현실에서는 각 세그먼트 소요시간이 20ns으로 일정하지 않다. 작업 중간에 문제 등이 발생할 수 있기 때문에 어려울 수도 있다.

현실적 파이프라인 구조

파이프라인 구조 vs 병렬적인 다중 기능 장치

- 실제 파이프라인 구조가 이론적인 최대 속도를 구현하지 못하는 이유

- 각 세그먼트 들이 부연산을 수행하는 시간이 서로 다르다.

- 또한 각 레지스터를 제어하는 클럭 사이클은 최대 전파시간을 갖는 세그먼트의 지연시간과 싱클르 맞추어야 한다.

- 다음 그림과 같이 병렬적인 다중 기능 장치(=파이프라인 처리 속도)를 고려할 수 있다.

- 각 P회로는 전체 파이프라인 회로에서와 동일하게 태스크를 수행한다.

- 그러나 이 구조는 순차적 처릭 ㅏ아니라 모든 회로가 동시에 데이터를 입력 받아 4 태스크를 한꺼번에 수행한다 - SIMD구조 일 뿐, 파이프라인이 더 효율적.

(파이프라인 구조 > 순차적 처리 구조)

산술 파이프 라인

파이프라인 구조가 적용되는 컴퓨터 설계

- 산술(arithmetic) 파이프 라인: 산술 연산들을 부연산으로 나누어 파이프라인의 세그먼트에서 수행

- 고속 컴퓨터에서 부동 소수점 연산, 고정 소수점 수의 곱셈, 과학계산용으로 활용

- 파이프라인 승산기(배열 승산기 - 부분 곱 사이의 캐리(carry) 전파시간의 최소화를 위한 가산기 보유)

- 명렁어(instruction) 파이프 라인: 명령어 사이클의 fetch, 디 코드, 실행 단계를 중첩 시킴으로 명령어 흐름에 동작

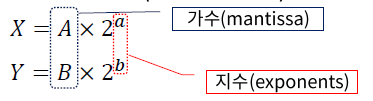

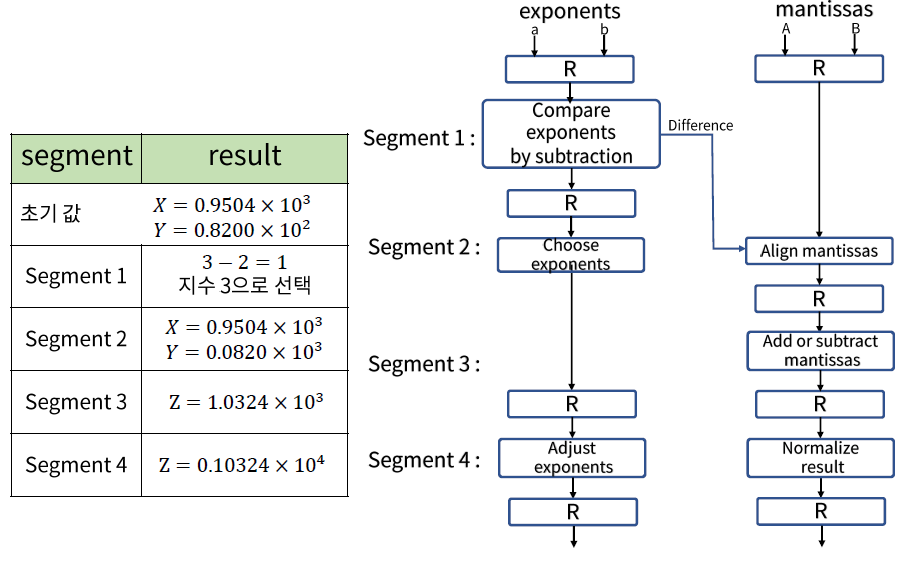

부동 소수점 덧겜과 뺄셈을 위한 파이프 라인

- 입력: 두개의 정규화(normalized)된 부동 소수점 이진수

- 각 세그먼트에서 수행되는 부 연산

- 지수의 비교

- 가수의 정렬

- 가수의 덧세미안 뺼셈

- 결과의 정규화

산술 파이프 라인의 효율성

명령어 파이프 라인

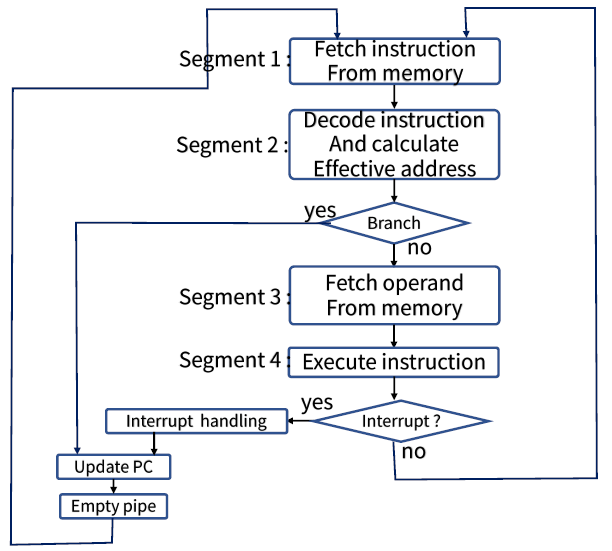

명령어 실행과 파이프라인 구조

- 명령어 파이프라인은 이전 명령어가 다른 세그먼트에서 실행되고 있는 동안 메모리에 연속적으로 저장되어 있는 다음 명령어를 읽어 옴으로서 fetc와 실행이 중첩되어 동시에 수행되는 구조.

- 분기가 발생할 경우 (가장 큰 취약점) - 현재의 파이프라인은 모두 비워져야하고, 분기명령 이후에 메모리에서 읽어온 명령어는 모두 무시 되어야 한다.

보다 효율적 명령어 실행을 위한 파이프라인 구조

- 명령어 fetch장치와 명령어 실행 장치로서 두 세그먼트 파이프라인을 구성하는 컴퓨터를 고려

- 명령어 fetch장치 -> FIFO(First-In_First-Out)에 의한 Que로 구성되어 queuing기법에 의한 메모리 참조에 의해 평균 메모리 접근 시간을 효과적으로 줄여준다.

- 명령어 파이프라인 수행되는데 있어 발생하는 애로 사항

- 세그먼트의 수행 시간이 서로 다름(실행되지 않는 세그먼트도 있을 수 있음, ex) 레지스터 모드 명령으 ㅣ경우 -유효주소 계산 불필요

- 두 개 이상의 세그먼트에 의해 동일한 주소 공간이 참조되는 경우

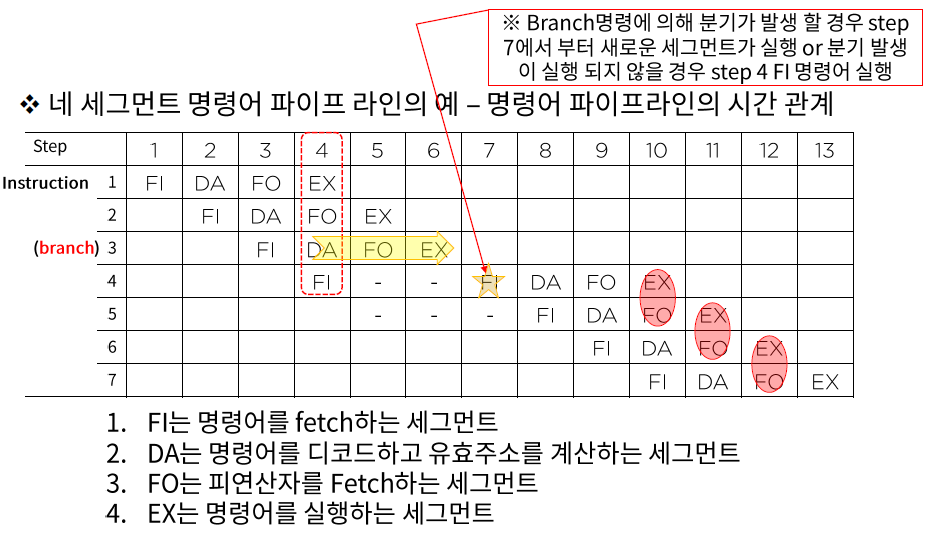

네 세그먼트 명령어

파이프라인 분기 예측

명령어 파이프라인이 정삭적인 동작에서 벗어나게 되는 요인:

- 자원 충돌(Resource Conflict): 두 세그먼트가 동시에 메모리를 접근하려고 하는 데에서 기인한다 -> 명령어 메모리와 데이터 메모리를 분리함으로써 대부분 해결한다.

- 데이터 의존성(Data Dependency): 충동은 어떤 명령어가 이전 명령어의 결과에 의존하여 수행되는데, 그 값이 아직 준비되지 않은 경우에 발생한다.

- 분기 곤란(Branch Difficulty): 분기 명령어같이 PC의 값을 변경 시키려는 명령어에 의해 발생한다.

데이터 의존성

- 데이터나 주소의 충돌은 명령어 파이프라인의 성능을 저하 시키는 요인

- 데이터 의존성: 아직 준비되지 않은 데이터를 기다리는 경우

(ex FO에 의해 피 연산자를 fetch하려고 하는 경우 아직 EX 세그먼트에 의해 데이터가 만들어지지 않는 경우) - 주소 의존성: 마이크로 연산 시 레지스터 간접모드를 사용하는 명령어는 이전 명령어가 주소 값을 메모리로 부터 로드 하는 명령어라면 곧바로 피연산자를 fetch하지 못하고 기다리게 된다.

- 데이터 의존성: 아직 준비되지 않은 데이터를 기다리는 경우

데이터 의존성 해결 방법

- 하드웨어 인터락(hardware interlock): 어떤 명령어의 피연산자가 파이프라인에서 앞서간 명령어의 목적지와 일치하는지를 검사하는 회로 -> 이러한 상황이 감지되면 피연산자가 준비되지 않은 명령어는 충돌을 피할 수 있을 만큼 충분한 클럭 사이클을 두어 지연시킨다.

- 오퍼랜드 포워딩9operand forwarding): 충돌을 감지하는 경우 특별한 통로를 통해 직접 파이프라인 세그먼트에 전달하는 경우.

분기 명령어의 처리

- 조건 분기 또는 무조건 분기 등은 처리 여하에 따라 파이프라인의 정상적인 프로그램 순서를 바꾸어 버리기 때문에 파이프라인 시스템을 채택하고 있는 컴퓨터의 성능을 저하시키는 주 요인으로 간주되고 있다.

- 순차적으로 처리될 명령어를 분기의 목표가 되는 명령어와 함께 저장하는 방법

- 분기 목표 버퍼(branch target buffer, BTB)의 사용: fetch 세그먼트 속에 있는 associative memoryL 이전 실행된 분기 명령어와 분기 목표 명령어를 저장하여 활용 (loop buffer - 일종의 레지스터)

- 분기 예측(branch prediction)

- 실제 다양한 프로그램의 실행 결과를 분석한 결과 참조의 시간적 지역성과 유사하게 일부 명령어들은 반복 수행되며 반복 실행시에는 규칙성을 갖는다.

- 이러한 예측 기법을 이용하여 분기 및 적재 명령어가 참조하는 오퍼랜드도 반복 참조 시 규칙성을 갖고 있으며 이를 이용할 경우 명령어 fetch과정에서 신속하게 오러팬드의 제공 및 fetch가 수월해질 수 있다, 다만 예측실패시 지불해야할 패널티(시간 지연)가 있을 수 있다.

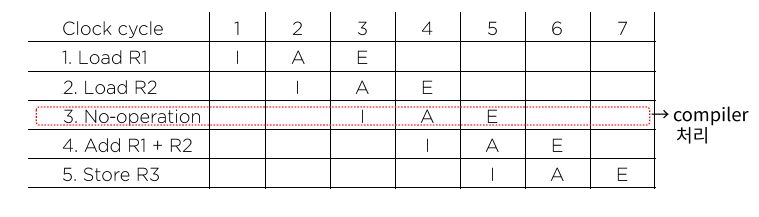

RISC Processor

- 설계목표

- 실행 명령어 수는 증가 하더라도 작업처리 시간의 감소가 가능.

- 명령어당 실행 클록 수 (CPI)와 클록 주기를 파이프라인 구조를 이용하여 감소시킬 수 있다.

- 구조적 특징

- 명령어의 1사이클 실행을 위한 파이프라인 구조, 메모리 참조를 위한 온칩 캐쉬(CPU내 메모리 구현, 명령어 캐쉬, 자료 캐쉬로 구성)

- 간단한 명령 코드와 주소 지정 모드 및 하드와이어 적 제어 장치

- 신속한 오퍼랜드 참조/문잭 전환을 위한 레지스터 집합9중첩된 레지스터 윈도우)

- 실수 연산의 별도 처리를 위한 코프로세서(Co-Processor)

- RISC 파이프 라인

- 명령어 사이클은 세개의 부연산으로 나뉘어 다음고 ㅏ같은 세 세그먼트로 구성

I: 명령어의 fetch

A: ALU의 동작

E: 명령어의 실행

- 명령어 사이클은 세개의 부연산으로 나뉘어 다음고 ㅏ같은 세 세그먼트로 구성