18. 파이프라인 CPU 성능 분석

파이프라인 분기 예측

명령 파이프라인 오작동 요인

-

자원 충돌(resource conflict) : 두 세그먼트가 동시에 메모리를 접근하려고 하는 때 발생

--> 명령어 메모리/데이터 메모리를 분리함으로 대부분 해결 -

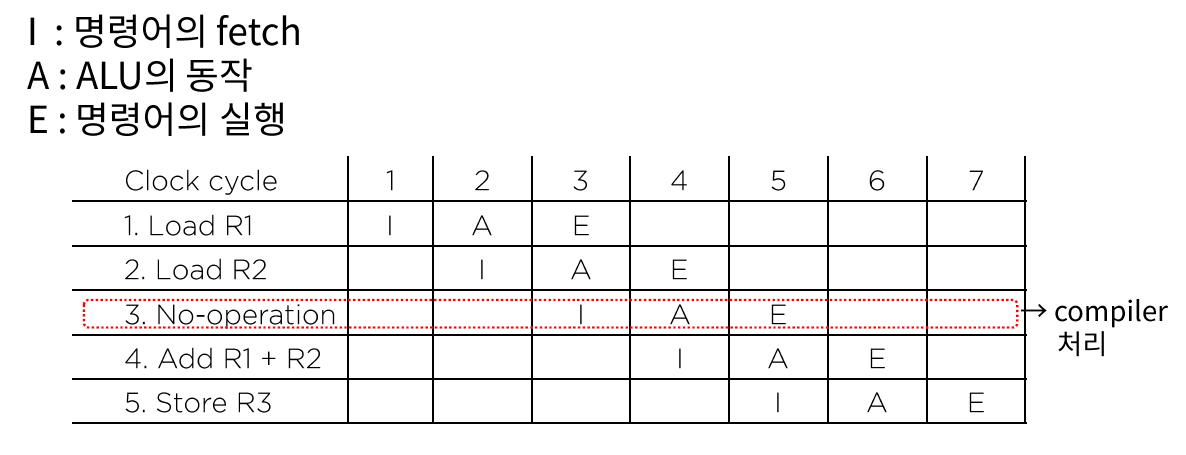

데이터 의존성(data dependency) : 충돌은 어떤 명령어가 이전 명령어의 결과에 의존하여 수앻되는데 그 값이 아직 준비되지 않은 경우에 발생

-

분기 곤란(branch difficulty) : 분기 명령어 같이 PC의 값을 변경 시키려는 병령에 의해 발생

데이터 의존성

데이터/주소의 충돌은 명령어 파이프라인의 성능을 저하시키는 요인이다.

-

데이터 의존성 : 아직 준비되지 않은 데이터를 기다리는 경우

(FO에 의해 피연산자를 fetch하려는 경우, EX 세그먼트에 의해 데이터가 만들어지지 않은 경우) -

주소 의존성 : 마이크로 연산 시 레지스터 간접모드를 사용하는 명령어는 이전 명령어가 주소값을 메모리로 부터 로드하는 명령어라면 곧바로 피연산자를 fetch하지 못하고 기다림

데이터 의존성 해결 방법

해결 방법에는 다음과 같은 방법이 있다.

-

hardware interlock : 어떤 명령어의 피 연산자가 파이프라인에 앞서간 명령어의 목적지와 일치하는지 검사하는 회로

-

operand forwarding : 충돌을 감지하는 경우 특별한 통로를 통해 직접 파이프라인 세그먼트에 전달하는 경우

분기 명령어 처리

분기 예측

실제 다양한 프로그램의 실행결과를 분석한 결과 참조의 시간적 지역성과 유사하게 일부 명령어들은 반복 수행되며 반복 실행시에는 규칙성을 갖는다.

이 때 분기 및 적재 명령어가 참조하는 오퍼랜드도 규칙성을 가지며 이를 이용할 경우 명령어 fetch 과정에서 신속하게 오퍼랜드의 제공 및 fetch 가 수월해진다.

예측 실패 시 페널티(시간 지연) 존재

RISC Processor

RISC 프로세서

설계 목표

실행 명령어 수는 증가하더라도 작업 처리 시간의 감소가 가능하다. 명령어당 실행 클락 수(CPI)와 클록 주기를 파이프라인 구조를 이용하여 감소시킬 수 있다.

구조적 특징

명령어의 1 사이클 실행을 위한 파이프라인 구조, 메모리 참조를 위한 온칩 캐시로 구성되어 있다. 신속한 오퍼랜드 참조/문맥 전환을 위한 레지스터의 집합이며 실수 연산을 위한 Co-processor이다.

RISC 파이프라인

명령어 사이클은 세 개의 부연산으로 나뉘어 다음과 같은 세 세그먼트로 구성된다.

파이프라인 CPU 성능 분석

이론적으로는 명령어 세그먼트의 횟수가 많아질수록 파이프라인의 이론적 최대속도가 증가할 것으로 분석되었으나 실제 상황은 그렇지 않다. 이론을 따라가기 위해선 전제조건이 필요하다.

- 모든 명령어는 동일한 처리과정으로 처리 되어야 함

- 파이프라인을 구성하는 각 단계의 처리 시간이 일정해야 함

- 모든 명령어는 작성된 순서에 따라 순차적으로 실행되어야 함

- 사용 명령어들 사이에는 상호 의존성이 없어야 함

- 명령어들 처리 시 공유 자원의 충돌이 없어야 함