1. 메모리와 캐시메모리

1.1. 램의 특징과 종류

- 메모리는 크게 RAM과 ROM으로 구성되어 있으나 RAM에 대해서만 다룬다.

- 휘발성 저장 장치로 전원을 끄면 데이터가 사라진다.

- CPU가 보조기억장치에 접근하는 것보다 주기억장치에 접근하는 것이 빠르다

- 저장할 데이터는 보조기억장치, 실행할 데이터는 메모리(RAM)

- 저장된 보조기억 장치의 데이터 일부를 가져와 메모리에 올려두어 실행한다

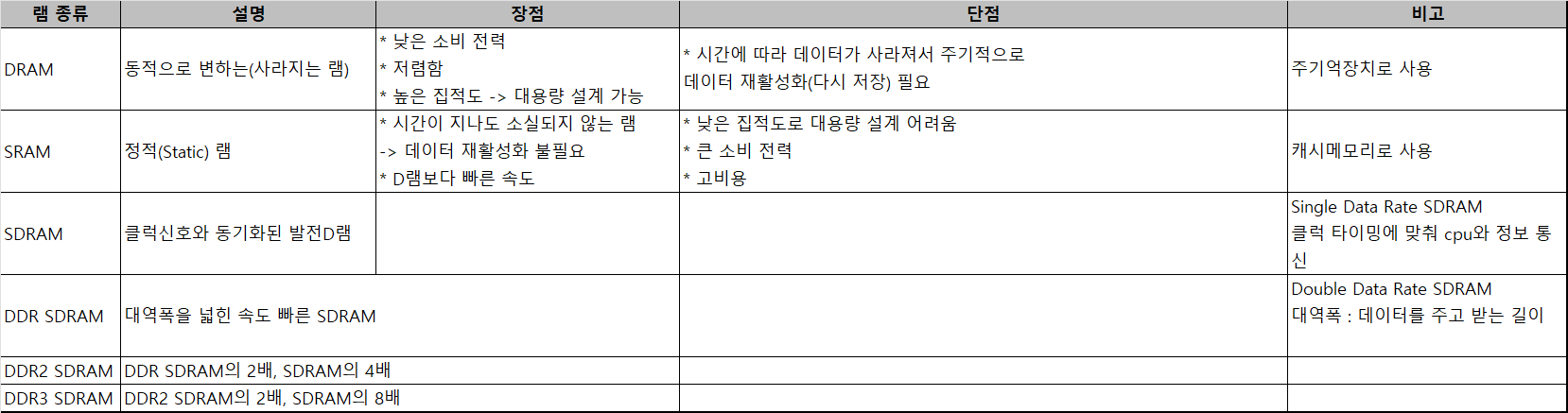

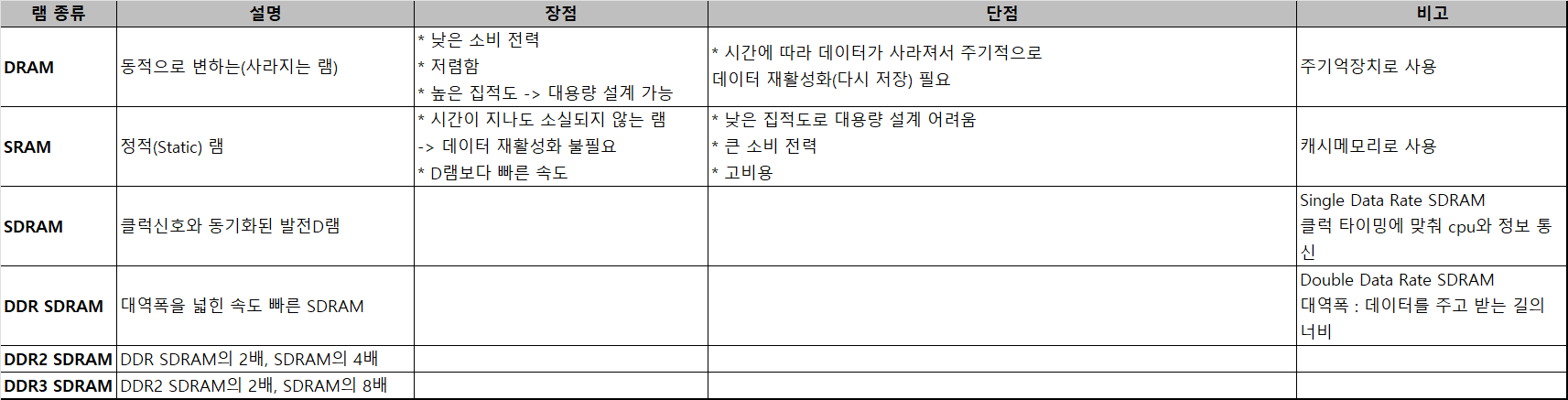

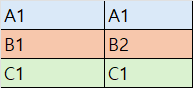

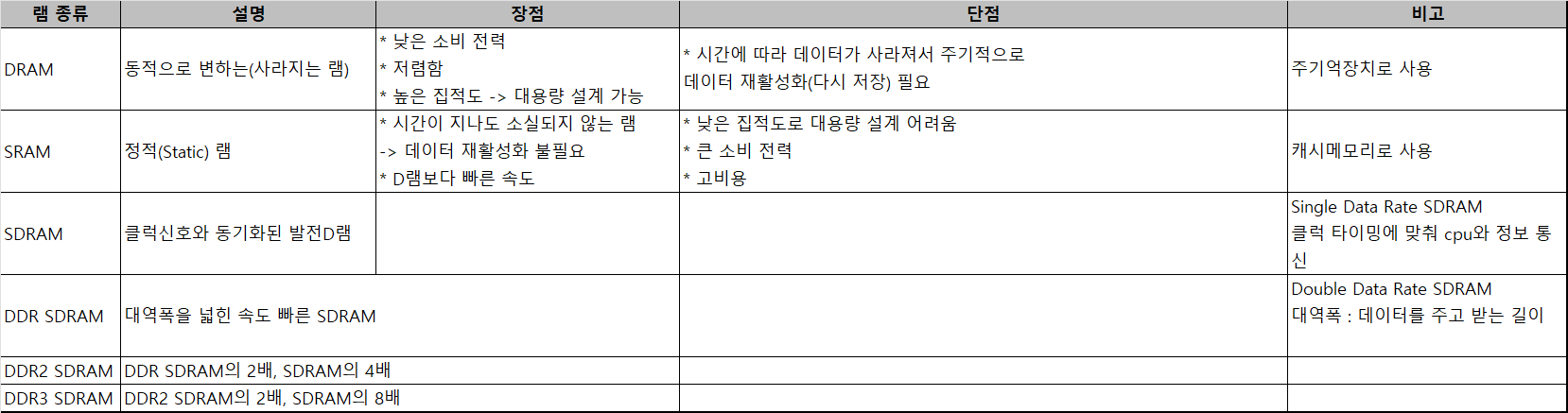

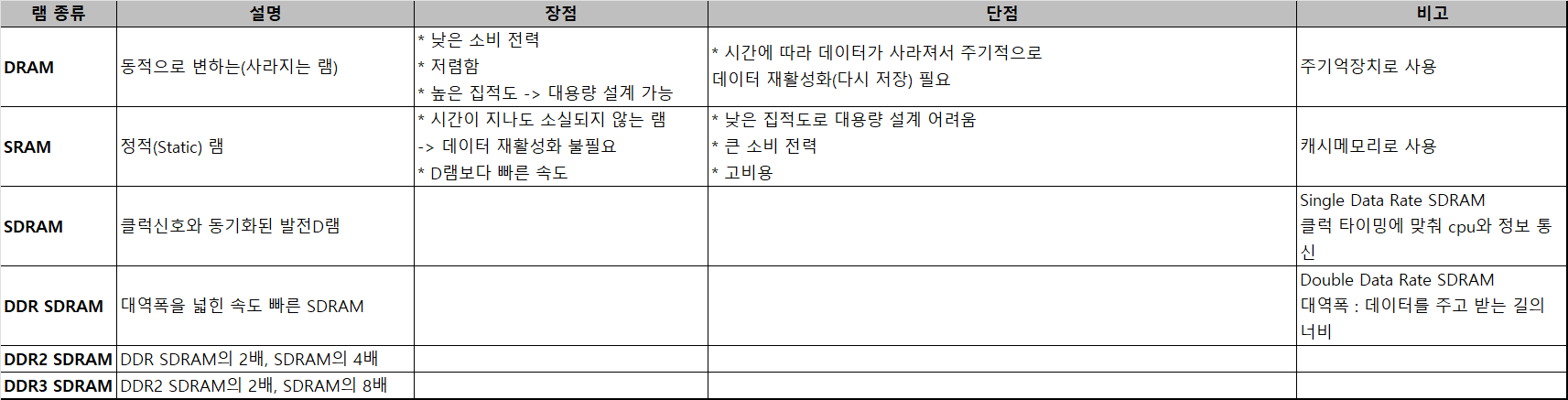

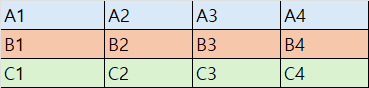

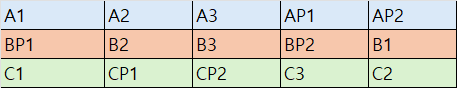

1.1.1. 메모리의 종류 요약

1.2. 메모리의 주소 공간

1.2.1 물리주소

- 메모리의 하드웨어 - 정보가 저장된 하드웨어 상의 주소

1.2.2 논리주소

- CPU & 실행 중인 프로그램에게 배정된 주소(방 번호로 비유)

- 프로그램의 시작점(베이스 레지스터)에서 떨어진 거리

1.2.3 메모리 관리 장치 - Memory Management Unit(MMU)

- 논리주소와 물리주소를 변환하는 장치

- 베이스 레지스터를 가지고 있음

- CPU의 논리주소 + MMU의 베이스 레지스터 = 메모리 물리주소

1.2.3.1. 베이스 레지스터

- 프로그램의 가장 장은 물리 주소

- 프로그램의 첫 물리 주소를 저장하는 셈

- 일종의 프로그램이 차지하는 메모리 주소의 시작점

1.2.3.2. 메모리 보호 기법

- CPU 명령이 명령과 무관한 프로그램에 영향을 주지 않도록 하는 조치

- 한계 레지스터 : 프로그램이 차지할 수 있는 메모리의 최대 번지 수

- 한계 레지스터 범위 = 베이스 레지스터 + 한계 레지스터

- CPU가 범위를 넘어서는 논리주소로 접근하려 하면 인터럽트(트랩)을 발생시켜 실행을 중단 시킨다.

1.3. 캐시 메모리

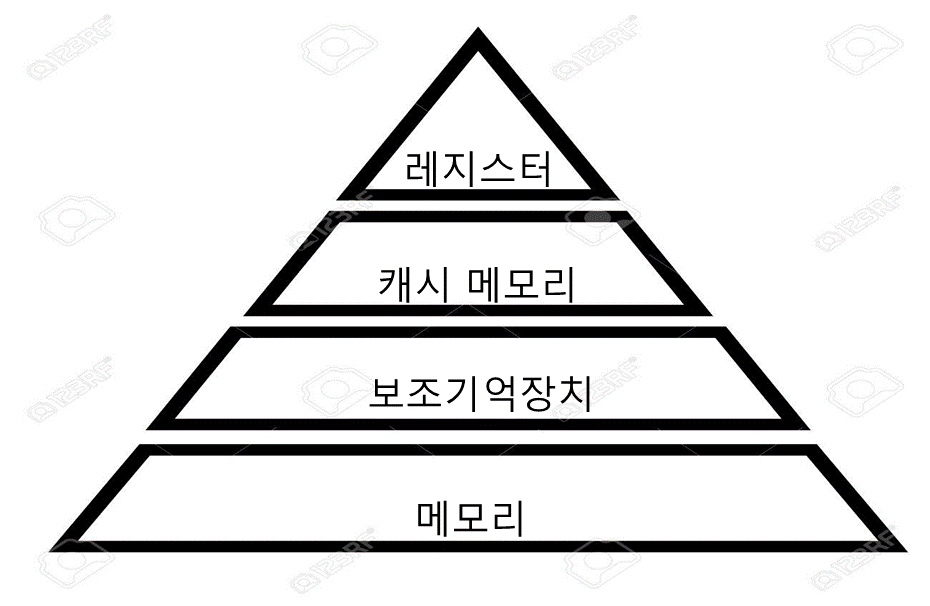

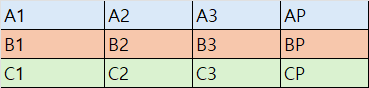

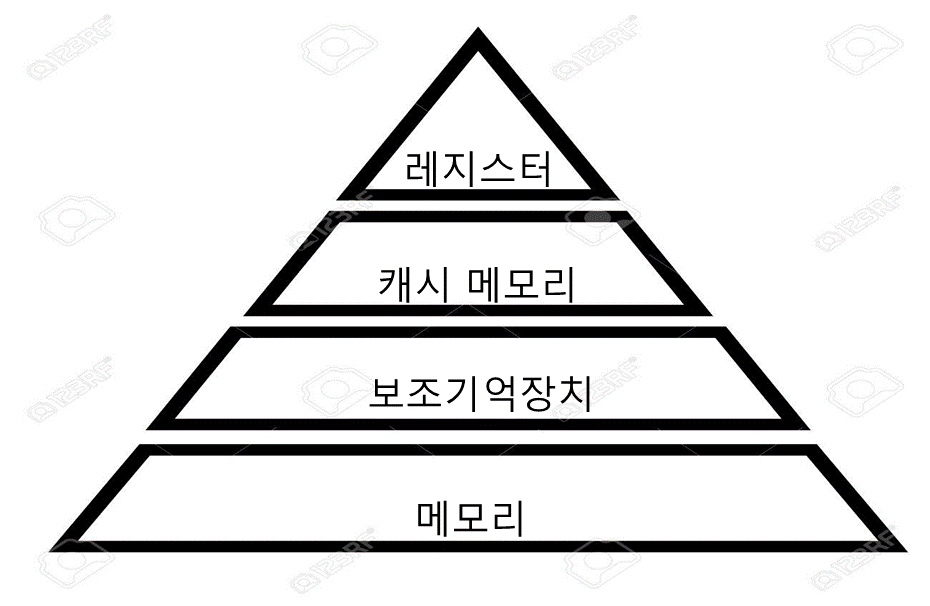

1.3.1 저장 장치 계층 구조

- CPU와 가까울수록 용량이 작고, 응답이 빠르며, 비싸다

- 레지스터 > 캐시 메모리 > 메모리 > 보조기억장치 순서

1.3.2 캐시메모리

- CPU와 메모리 사이에 사용이 빈번한 데이터를 담아두는 저장 장치(SRAM 사용)

1.3.2.1. 캐시 메모리 종류

- L1

- CPU(코어)에 가장 가까운 캐시 메모리

- CPU(코어) 내부에 존재

- 분리형 캐시

- L1D : 데이터 전용 L1

- L1I : 명령어 전용 L1

- L2

- L3

1.3.2.3. 캐시히트

- 캐시 히트 : CPU가 자주 사용할 것 같은 데이터를 캐시에 담아두었을 때, 실제로 자주 사용한 경우

- 캐시 적중률 : 캐시 히트 수 / (캐시 히트 수 + 캐시 미스 수)

1.3.2.2. 참조 지역성 원리

- 시간 지역성 : CPU는 최근 접근했던 메모리 공간에 다시 접근하려 하는 경향

- 공간 지역성 : CPU는 접근한 메모리 공간 근처를 접근하려는 경향 - 프로그램 내 비슷한 데이터들이 모여 저장

확인문제

p185-3

- DRAM

- SRAM

- 주로 캐시 메모리로 활용

- DRAM에 비해 낮은 집적도

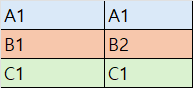

p205-1

- 저장 장치 계층 구조

2. 보조기억장치

2.1. 다양한 보조기억장치

2.1.1. 하드디스크

2.1.1.1. 구성

- 플래터 : 데이터가 실질적으로 저장되는 곳

- 트랙 : 플래터를 구성하는 하나의 원형 공간

- 섹터 : 트랙을 조각 낸 부분

- 스핀들 : 플래터를 회전시키는 구성 요소

- RPM : 스핀들이 플래터를 돌리는 분당 회전 수

- 헤드 : 플래터를 대상으로 데이터를 읽고 쓰는 구성 요소

- 단일 헤드 : 플래터 한 면당 헤드가 하나씩

- 다중 헤드 : 헤드가 트랙 별로 달려있는 경우

- 디스크 암 : 원하는 위치로 헤드를 이동시키는 구성 요소

- 실린더 : 여러 겹의 플래터 상에서 트랙이 위치한 곳을 모아 놓은 논리적 단위

- 탐색 시간 : 데이터가 저장된 트랙까지 헤드를 이동시킨 시간

- 회전 지연 : 헤드가 있는 곳으로 플래터를 회전 시킨 시간

- 전송 시간 : 하드 디스크와 컴퓨터 간에 데이터를 전송하는 시간

2.1.2. 플래시 메모리

2.1.2.1. NAND 플래시 메모리

- 셀 : 플래시 메모리에서 데이터를 저장하는 가장 작은 단위

- Single Level Cell(SLC) : 한 셀에 1비트 저장, 2개 정보 표현 가능

- Multi Level Cell(MLC) : 한 셀에 2비트 저장, 4개 정보 표현 가능

- Triple Level Cell(TLC) : 한 셀에 3비트 저장, 8개 정보 표현 가능

- SLC > MLC > TLC 순서로 수명, 속도, 가격이 높음

- 페이지 : 셀의 집합

- 읽기/쓰기의 단위

- FREE : 새 데이터를 받을 수 있는 상태

- VALID : 유효 데이터를 저장한 상태

- INVALID : 쓰레기 값을 저장한 상태

- 가비지 컬렉션 : 쓰레기 값을 정리하기 위해 페이지를 복제 후 원본 페이지를 삭제

- 블록 : 페이지의 집합

- 플레인 : 블록의 집합

- 다이 : 플레인의 집합

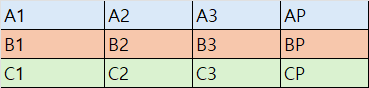

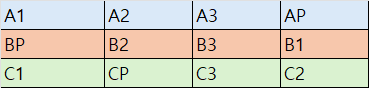

2.2. RAID

2.2.1. RAID의 종류

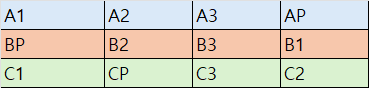

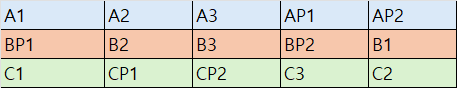

- RAID0 : 여러 개의 보조기억장치에 데이터를 나누어 저장

- 여러 저장 장치에 나누어 저장하였기에 동시에 읽기/쓰기 가능

- 하드디스크 중 하나의 데이터에 문제가 생기면 복구 불가능

- RAID1 : 복사본 생성

- 데이터 복구 가능

- 데이터 저장 비용 상승

- RAID4 : 오류 검출 및 복구 정보 저장 장치(패리티 비트)

- 비교적 적은 디스크를 활용하여 복구 가능

- 패리티를 저장하는 공간에서 병목현상 발생

- RAID5 : RAID4의 개선 방법

- 패리티 비트를 번갈아가며 저장

- RAID6 : RAID5의 개선 방법

- 두개의 패리티 비트를 생성하여 안정성 상승

- 대신 저장 속도 감소

3. 입출력장치

3.1. 장치 컨트롤러 & 장치 드라이버

3.1.1. 장치 컨트롤러

- 전송률 : 데이터를 빨리 교환할 수 있는 지를 나타내는 지표

- CPU의 전송속도와 입출력장치의 전송속도차이를 완화해주는 장치 컨트롤러가 필요

- 입출력 제어기 / 입출력 모듈 이라고도 불림

데이터 버퍼링

- 버퍼 : 전송률이 높은 장치와 낮은 장치 사이에 주고받는 데이터를 보관하는 임시 저장 공간

- 버퍼링 : CPU와 입출력 장치의 전송률을 비슷하게 맞추는 방법

장치 컨트롤러 내부 구조

- 데이터 레지스터 : CPU와 입출력장치 사이에 주고받을 데이터가 담기는 레지스터, RAM으로 대신하기도 함

- 상태/제어 레지스터 : 입출력장치의 입출력 작업 준비/완료/오류 등의 상태 정보 저장, 입출력장치가 수행할 내용에 대한 정보/명령 저장

3.1.2. 장치 드라이버

- 장치 컨트롤러의 동작을 감지 및 제어하는 프로그램

3.2. 입출력 방법

3.2.1. 프로그램 입출력

- 프로그램 속 명령어로 입출력장치를 제어하는 방법

- CPU가 프로그램 속 명령어를 실행하는 과정에서 입출력 명령어를 만나면 CPU는 입출력장치에 연결된 장치 컨트롤러와 상호작용하며 입출력 작업을 수행

3.2.1.1. 작업 수행 순서

- 작업 내용 : 메모리에 저장된 정보를 하드 디스크에 백업(= 하드 디스크에 새로운 정보를 쓰다)

- CPU가 하드 디스크 컨트롤러의 제어 레지스터에 쓰기 명령 전달

- 하드 디스크 컨트롤러는 하드 디스크 상태 확인, 준비 상태라면 하드 디스크 컨트롤러는 상태 레지스터에 준비완료 전달

3-1. CPU는 상태 레지스터를 주기적으로 읽어 하드 디스크 상태 확인 - 폴링(POLLING)

3-2. 준비 상태가 확인되면 메모리 정보를 데이터 레지스터에 작성

3-3. 백업 작업이 끝날 때까지 3-1 ~ 3-2 작업을 반복 후, 작업 종료

- 요약 : 명령 -> 상태 확인 -> 데이터 작성 -> 작업 종료

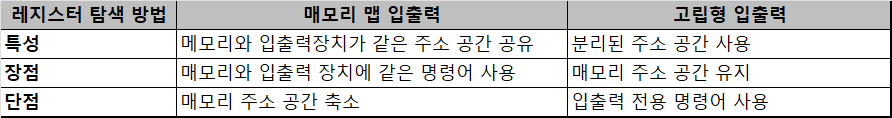

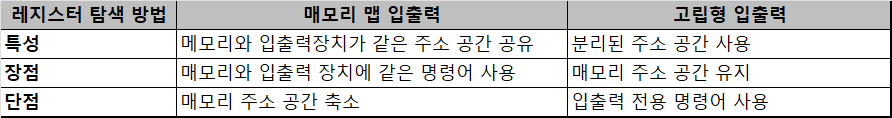

3.2.1.2. CPU가 장치 컨트롤러 속 레지스터를 찾는 방법

- 매모리 맵 입출력

- 매모리에 접근하기 위한 주소 공간과 입출력장치에 접근하기 위한 주소 공간을 하나의 주소 공간으로 간주하는 방법

- 고립형 입출력

- 매모리를 위한 주소 공간과 입출력자잋를 위한 주소 공간을 분리하는 방법

3.2.2. 인터럽트 기반 입출력

- 인터럽트 : CPU가 입출력장체 처리할내용을 명령하면 입출력장치가 명령어를 수행하는 동안 CPU는 다른 일을 할 수 있다.

인터럽트 기반 입출력

- 입출력장치가 CPU에게 인터럽트 요청 신호를 보내면 CPU는 하던 일을 잠시 멈추고 해당 인터럽트를 처리하는 프로그램인 인터럽트 서비스 루틴을 실행 후 다시 하던 일로 복귀

- CPU 부담 : 인터럽트 기반 입출력 < 프로그램 입출력(폴링 방식)

동시 인터럽트 발생

- 우선순위에 따라 처리

- Non-Maskable Interupt(NMI) : 플래그 레지스터 속의 인터럽트 비트가 활성화여부에 상관없이 무시할 수 없는 인터럽트

- 프로그래머블 인터럽트 컨트롤러(PIC) : 우선순위를 반영한 인터럽트 처리 장치

- PIC가 장치 컨트롤러에서 인터럽트 요청 신호 수신

- 인터럽트 우선순위 판단, CPU에 전달

- CPU의 PIC 신호 수신

- PIC -> 데이터 버스 -> CPU 로 인터럽트 백터 전송

- CPU는 인터럽트 백터를 통해 인터럽트 요청 주체 확인 및 인터럽트 서비스 루틴 실행

- PIC를 두 개 이상의 계층으로 구성하면 더 많은 하드웨어 인터럽트를 관리 가능

3.2.3. DMA 입출력

- 프로그램 기반 입출력과 인터럽트 기반 입출력의 공통점

- 입출력장치와 메모리 간의 데이터 이동은 cpu가 주도하고, 이동하는 데이터도 cpu를 거친다.

- CPU의 작업량에 부담이된다.

3.2.3.1. Direct Memory Access(DMA)

- 입출력장치와 메모리가 CPU를 거치지 않고 상호작용할 수 있는 입출력 방식

- DMA 입출력을 위한 시스템 버스에 연결된 DMA 컨트롤러 필요

3.2.3.2. DMA 순서

- cpu는 DMA 컨트롤러에 입출력장치에 주소, 수행할 연산(읽기/쓰기), 읽거나 쓸 메모리의 주소 등의 정보로 입출력 작업 명령

- DMA 컨트롤러는 CPU 대신 장치 컨트롤러와 상화작용하여 입출력 작업 수행

- 입출력 작업 종료 후 DMA 컨트롤러가 CPU에 인터럽트를 걸어 작업 종료를 알림

3.2.3.3. 입출력 버스

- DMA 단점 : CPU 작업량을 줄여주지만 시스템 버스를 사용한다. 시스템 버스는 공용이며 동시 작업이 불가능하기에 DMA가 사용하는 동안엔 CPU가 작업을 할 수 없다.

- 입출력 버스를 따로 만들어서 이러한 단점을 보완

- Peripheral Component Interconnect(PCI 버스)

- PCI Express(PCIe) 버스