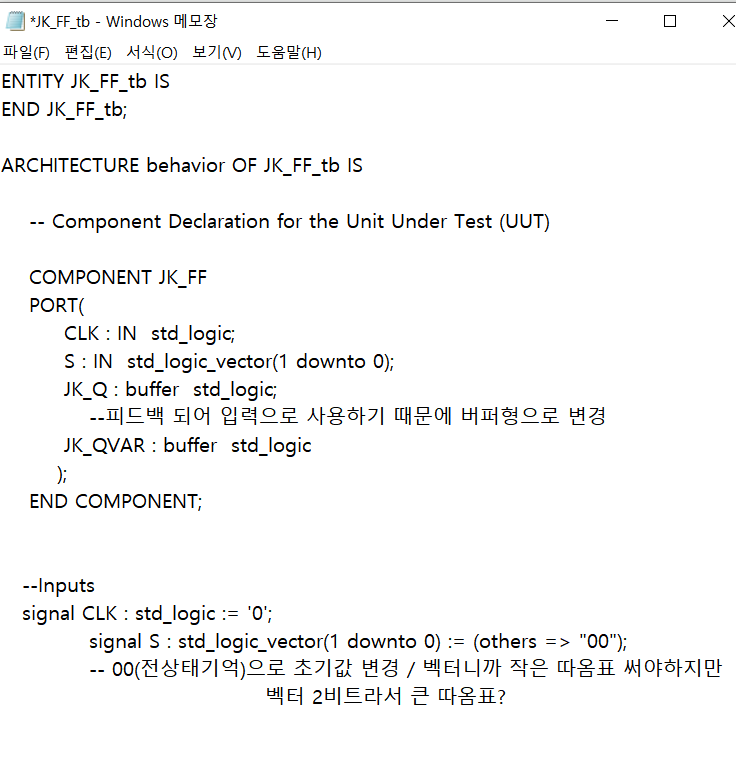

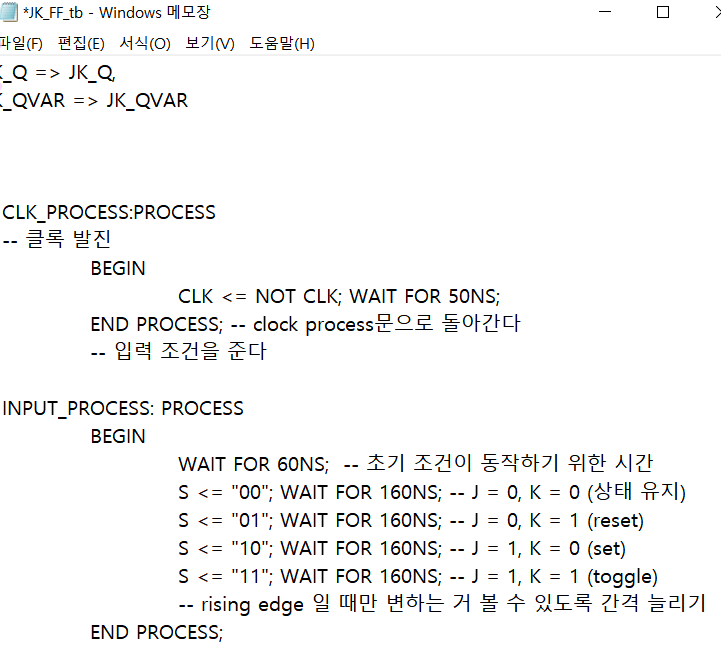

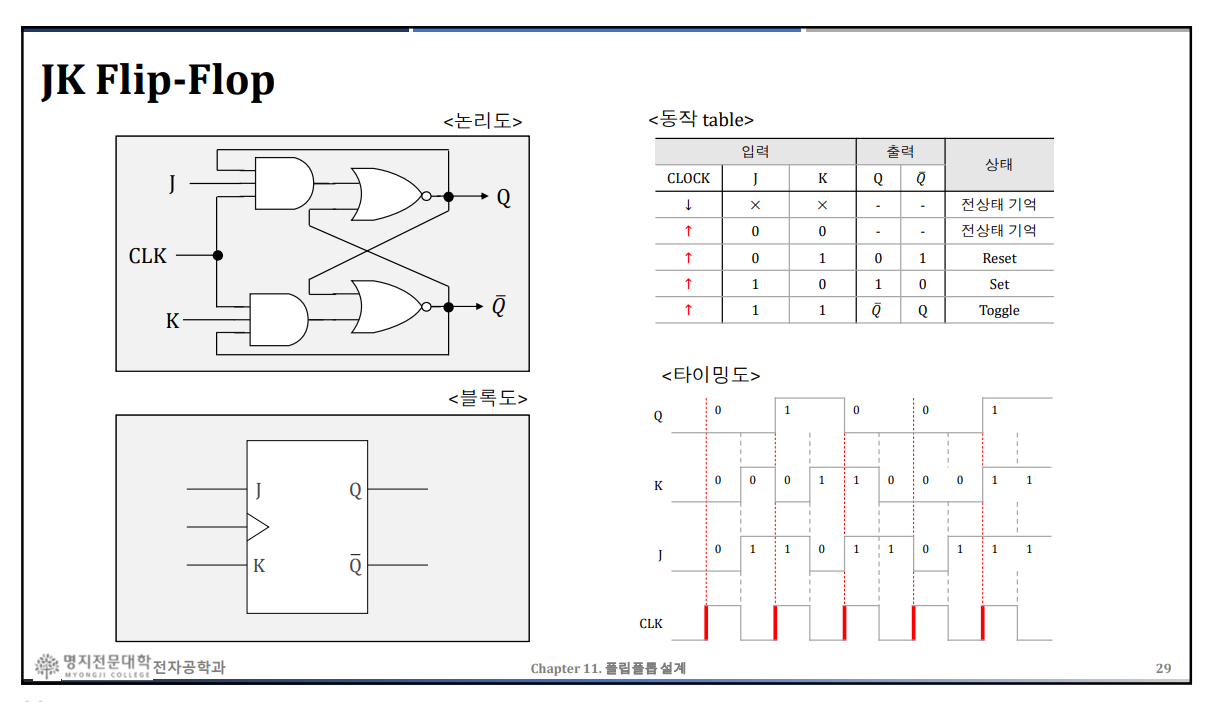

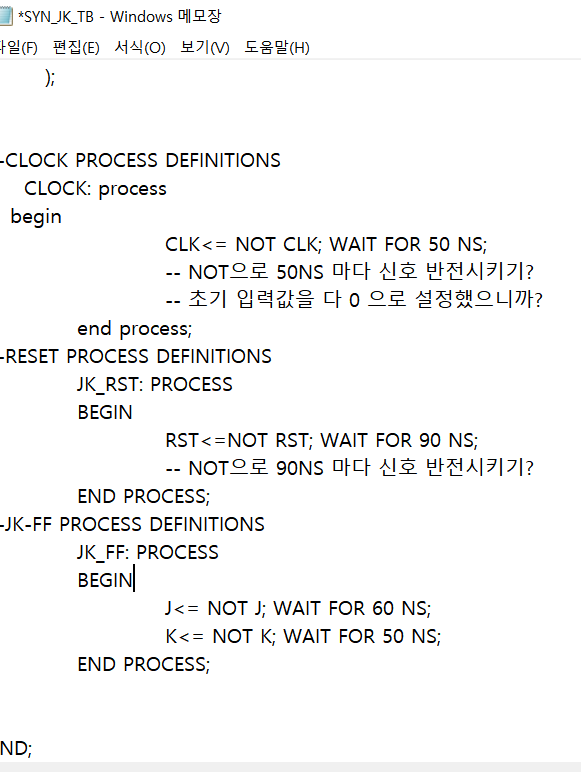

JK_FF_TB

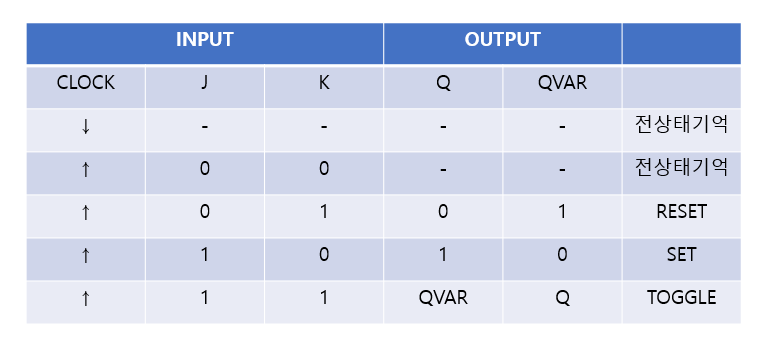

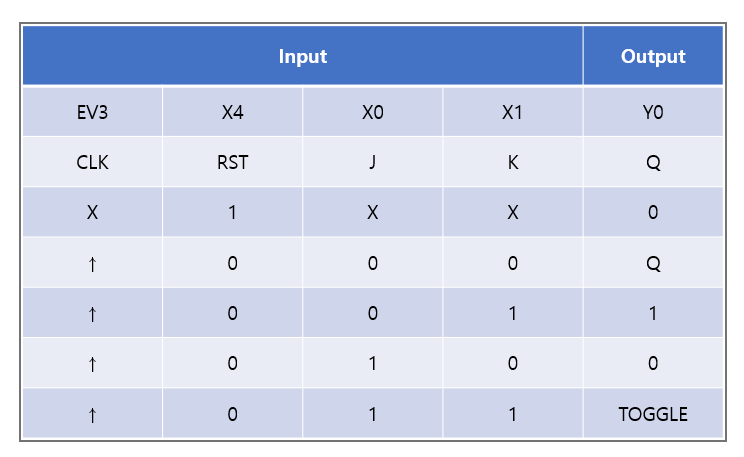

JK가 01일 때 CLK ON -> 01

JK가 10일 때 CLK ON -> 10

JK가 11일 때 CLK ON -> 10 TOGGLE

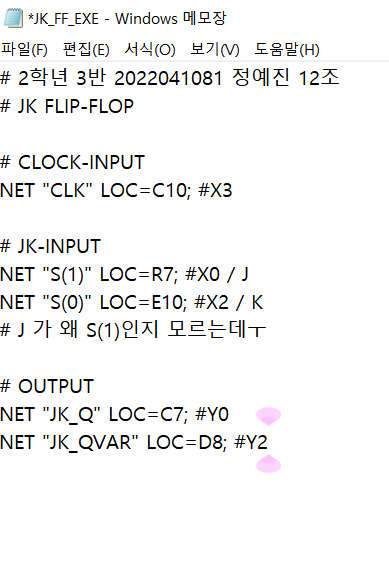

JK_FF_EXE

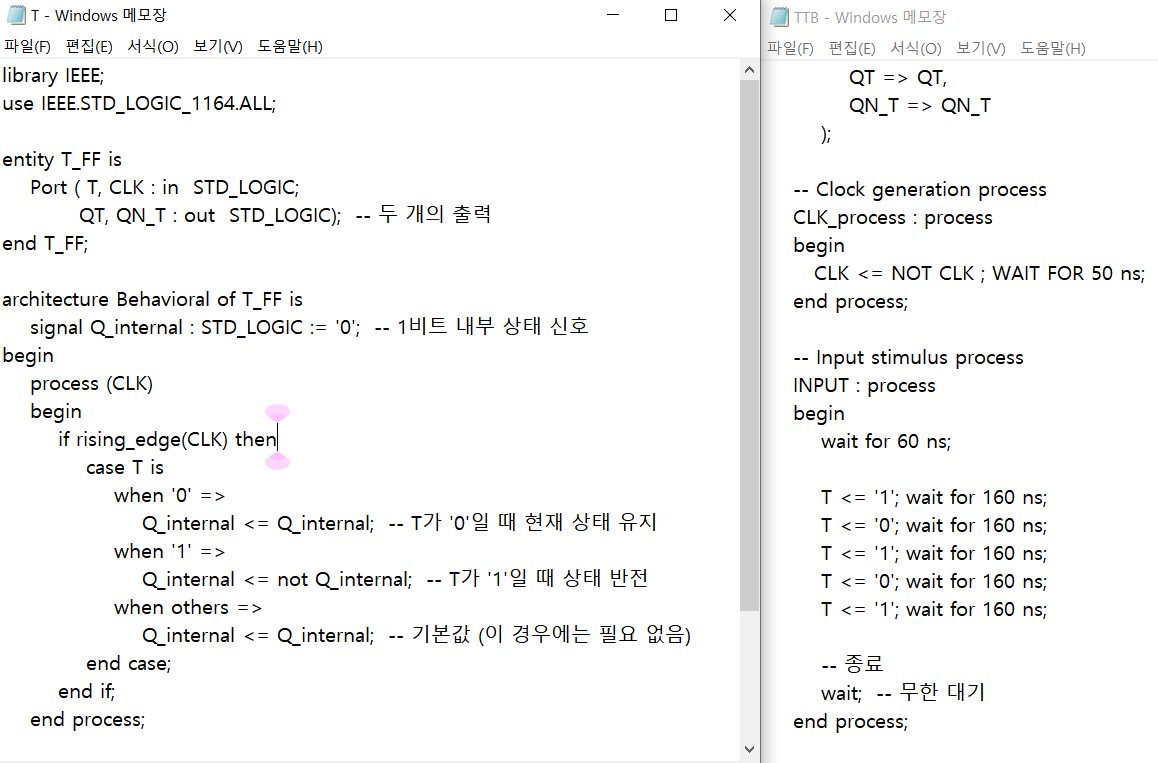

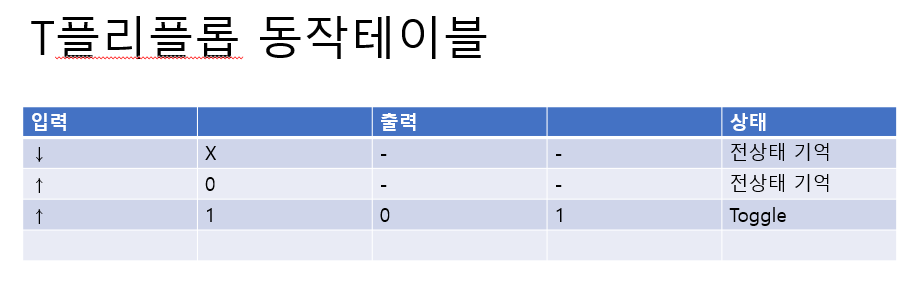

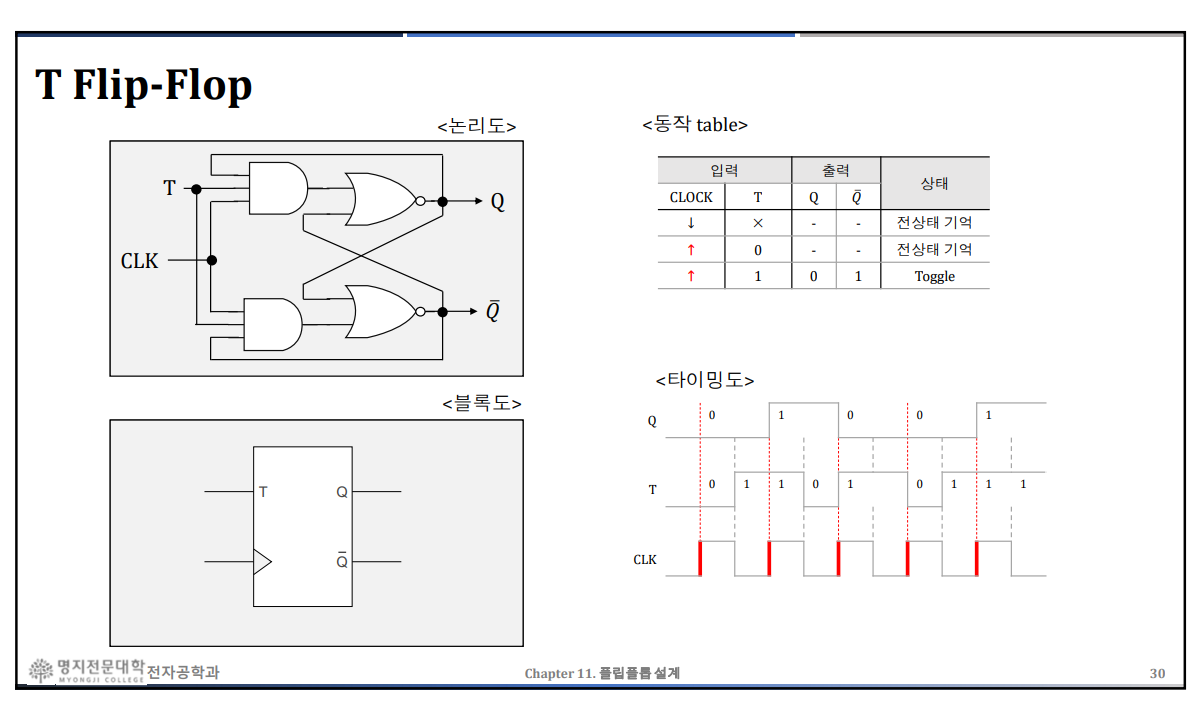

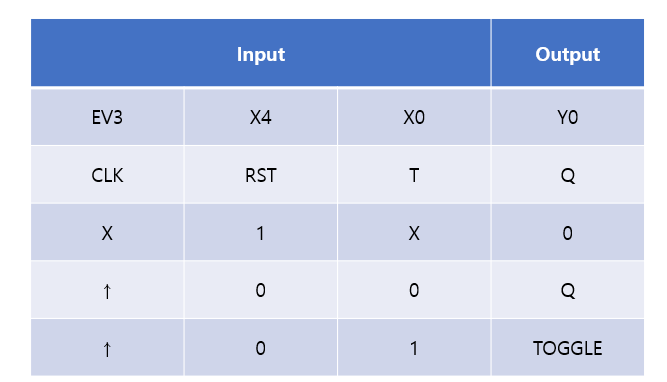

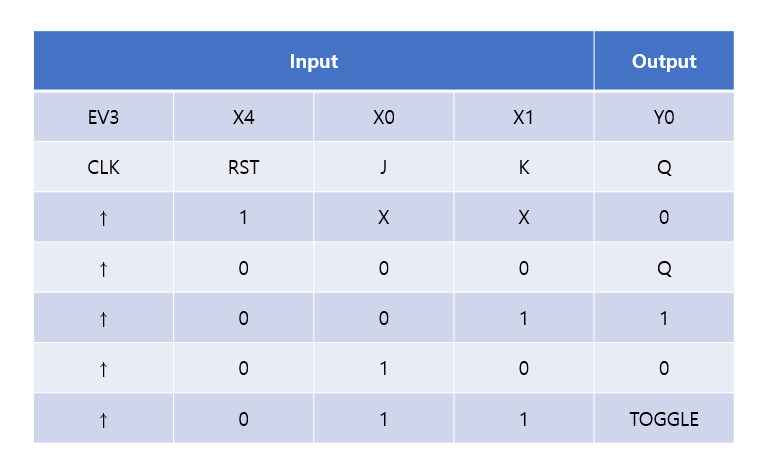

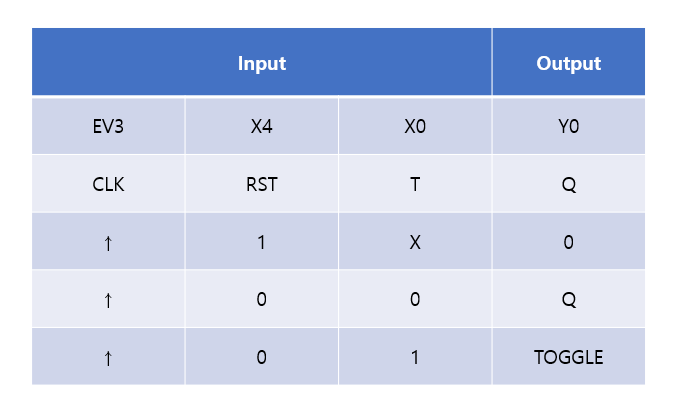

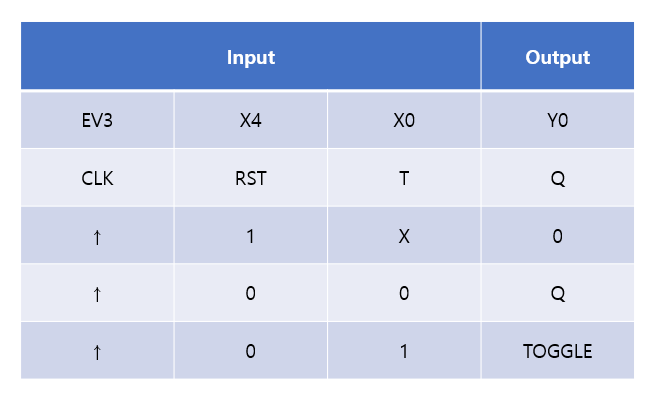

T_FF

T가 0 일 때 CLK ON -> 01 전상태기억

T가 1 일 때 CLK ON -> 10 TOGGLE

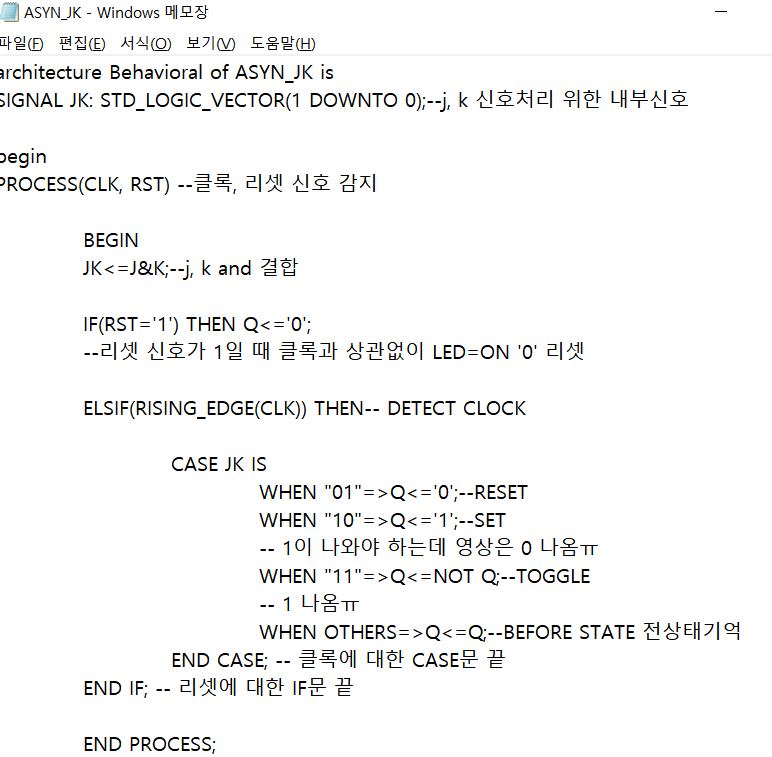

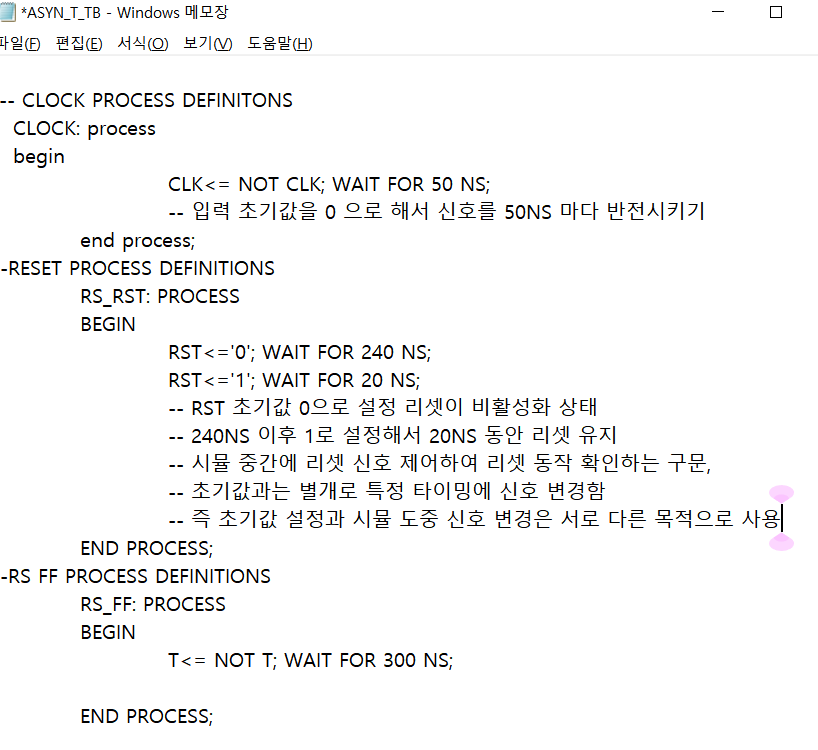

ASYN_JK

jk 결합을 프로세스 안에서 하는 거랑 밖에서 하는 거랑 다른가

리셋 누르면 0 나옴

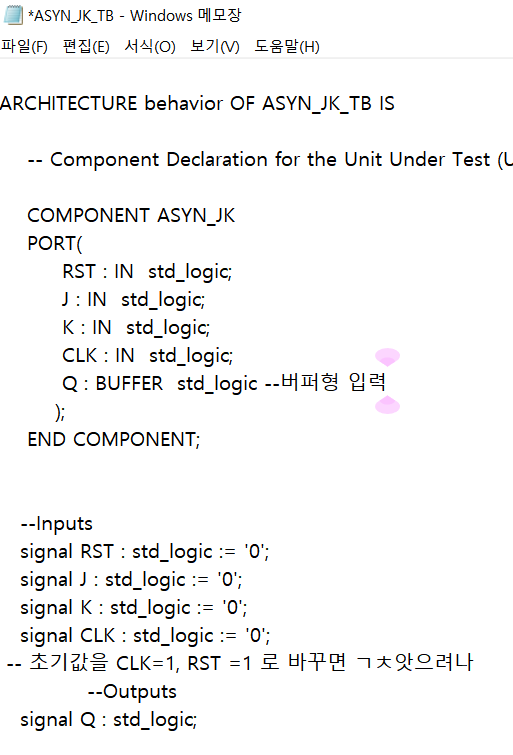

ASYN_JK_TB

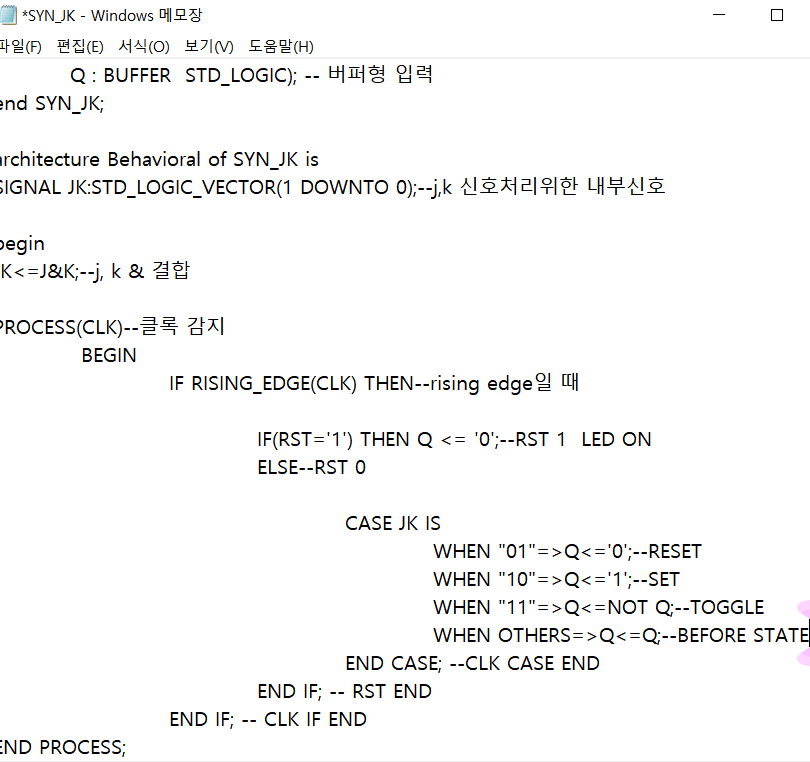

SYN_JK

JK가 00일 때 CLK ON -> 0

JK가 01일 때 CLK ON -> 1

JK가 10일 때 CLK ON -> 0 --이거 1 나와야 하는디?

JK가 11일 때 CLK ON -> 0 TOGGLE

RST 누르면 0이 됨.. 맞나

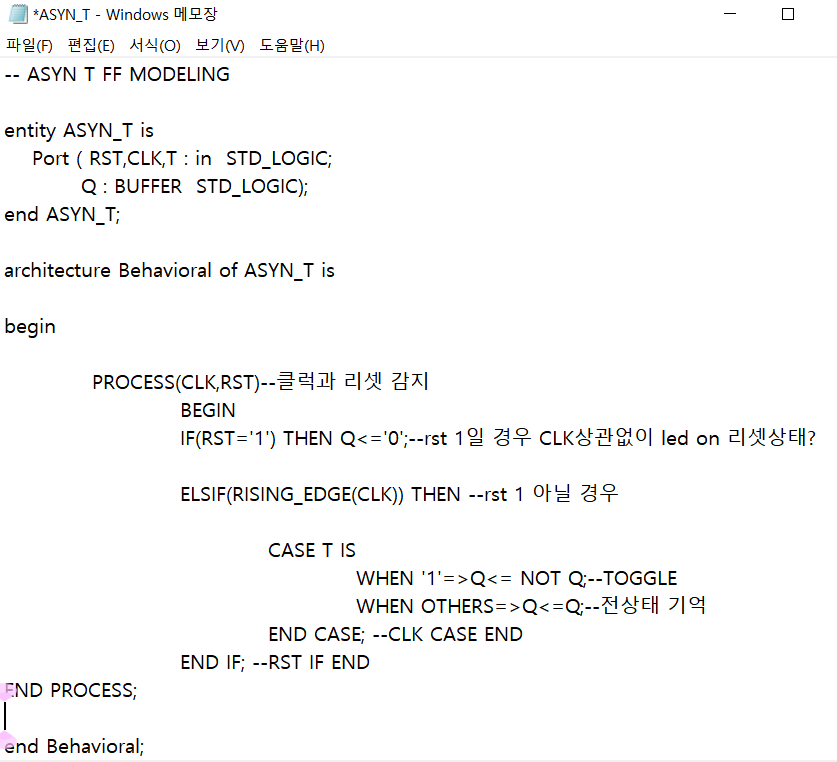

ASYN_T

rst 1일 경우 CLK상관없이 0으로 led on 리셋상태

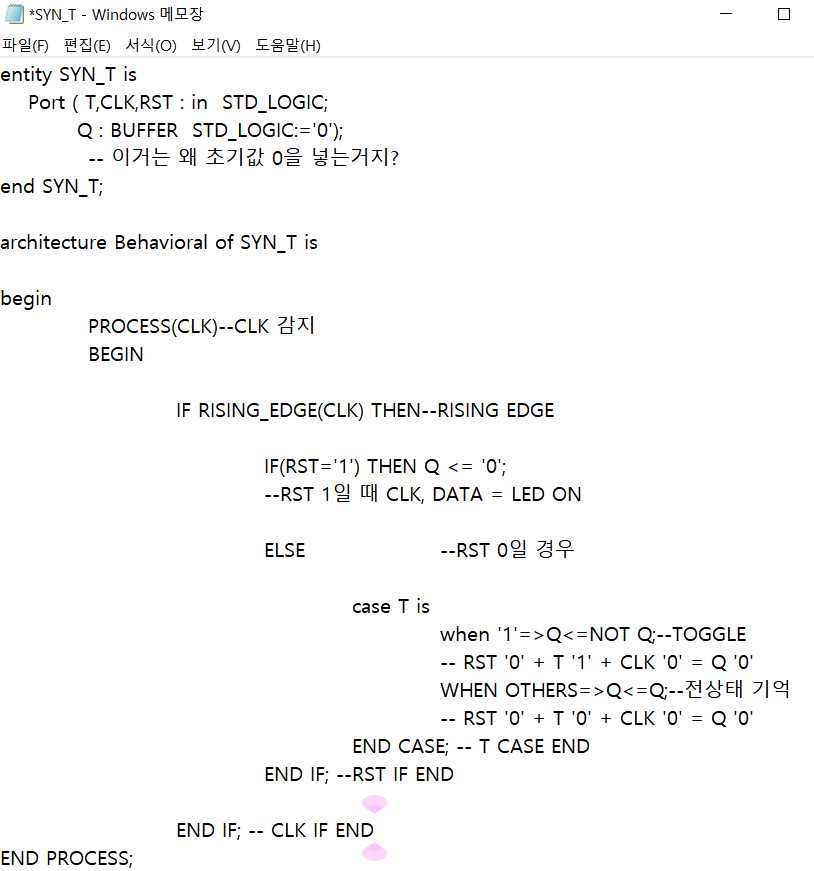

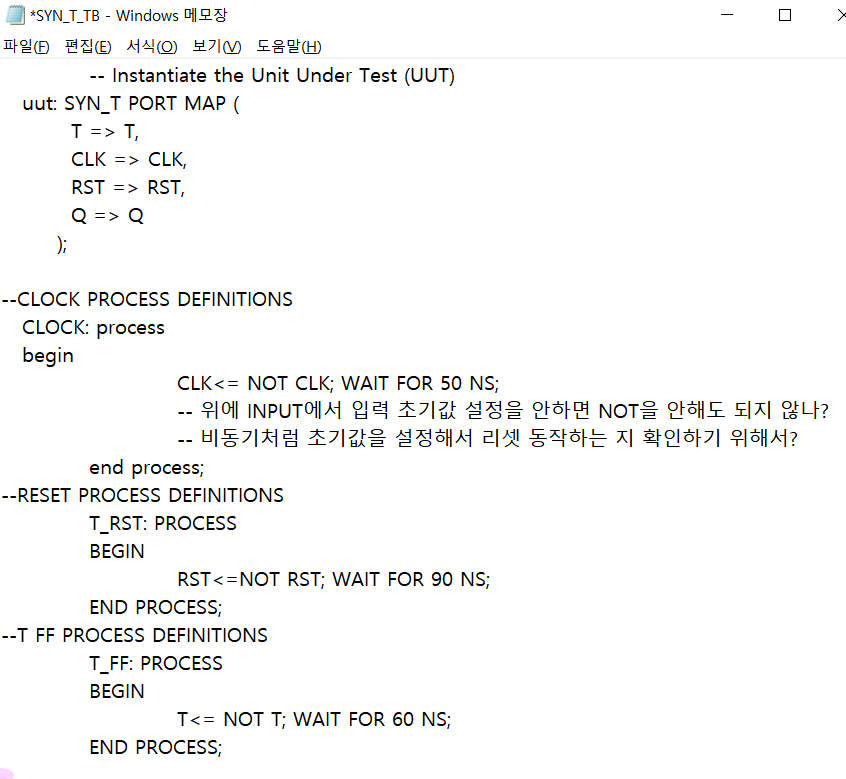

SYN_T

--RST 1일 때 CLK, DATA = LED ON

-- RST '0' + T '1' + CLK '0' = Q '0'

-- RST '0' + T '0' + CLK '0' = Q '0'

버퍼에 0 넣는 이유는 출력 Q가 시뮬레이션 시작 시에 명확한 초기 상태(0)에서 시작하도록

플립플롭이 원래 0에서 시작하는.. 그런거였어?