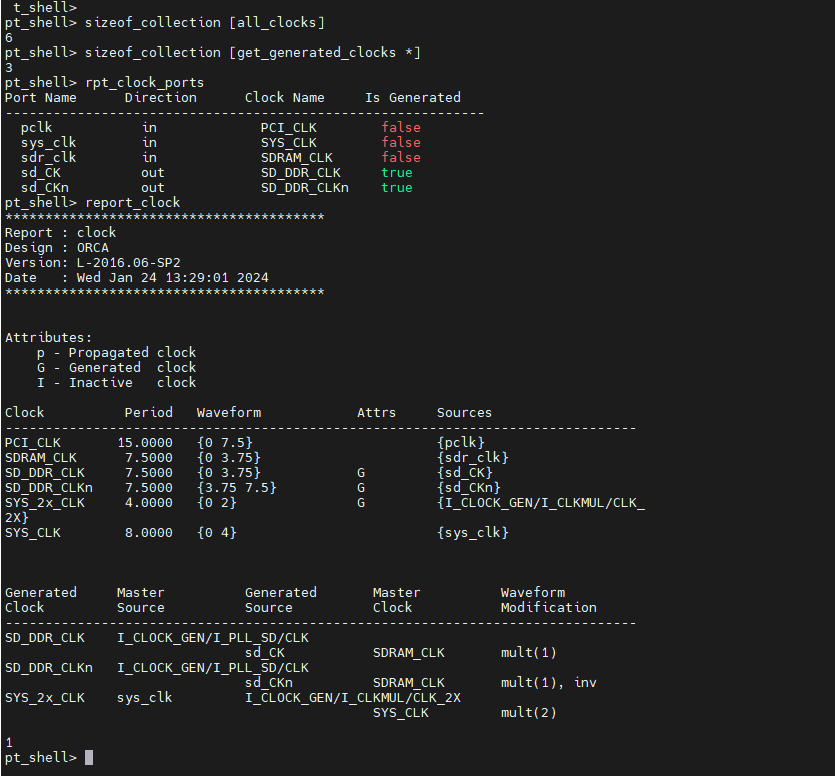

sizeof_collection [all_clocks]

sizeof_collection [get_generated_clocks *]

input의 master clock

rpt_clock_ports

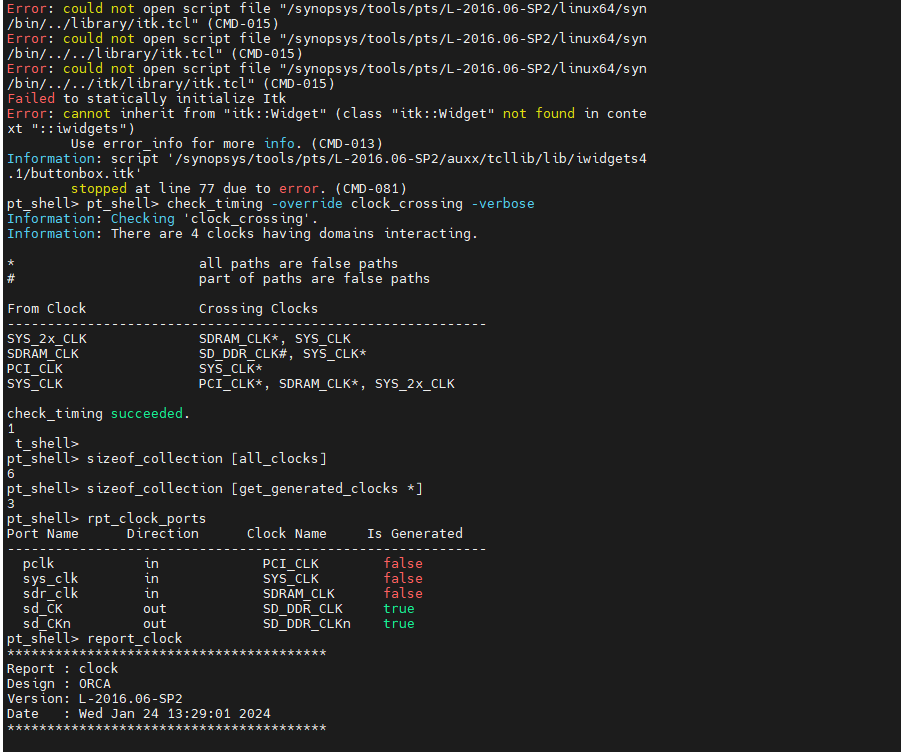

pt_shell> check_timing -over clock_crossing -verbose

Information: Checking 'clock_crossing'.

Information: There are 4 clocks having domains interacting.

all paths are false paths

#part of paths are false paths

From Clock Crossing Clocks

-----------------------------------------------------------.

SYS_2x_CLK SDRAM_CLK, SYS_CLK

SDRAM_CLK SD_DDR_CLK#, SYS_CLK

PCI_CLK SYS_CLK

SYS_CLK PCI_CLK, SDRAM_CLK, SYS_2x_CLK

check_timing succeeded.

pt_shell> report_timing -path short -to [all_outputs]

코드 사용할경우

Report : timing

-path_type short

-delay_type max

-max_paths 1

-sort_by slack

Design : ORCA

Version: L-2016.06-SP2

Date : Wed Jan 24 13:41:07 2024

Startpoint: sdr_clk (clock source 'SDRAM_CLK')

Endpoint: sd_DQ[6] (output port clocked by SD_DDR_CLK)

Path Group: SD_DDR_CLK

Path Type: max

Min Clock Paths Derating Factor : 0.9000

Point Incr Path

---------------------------------------------------------------.

clock SDRAM_CLK (fall edge) 3.7500 3.7500

clock source latency 0.0000 3.7500

sdr_clk (in) 0.0000 3.7500 f

...

sd_DQ6 4.4006 8.1506 f

data arrival time 8.1506

clock SD_DDR_CLK (rise edge) 7.5000 7.5000

clock reconvergence pessimism 0.0000 7.5000

output external delay -0.7500 6.7500

data required time 6.7500

---------------------------------------------------------------.

data required time 6.7500

data arrival time -8.1506

---------------------------------------------------------------.

slack (VIOLATED) -1.4006

1

pt_shell>