I/O HardWare

I/O 장치의 종류

- Storage (저장장치) : SSD, HDD, DVD-ROM

- Transmission (전송장치) : 네트워크 카드, 모뎀

- Human-Interface (사용자 인터페이스 장치) : 모니터, 키보드, 마우스

I/O 장치와 컴퓨터 시스템 사이의 통신

- Port : 장치를 위한 연결 점 (각 I/O 장치가 연결되어 있음)

- Bus : 여러 장치들이 공용하는 와이어 집합

(구현 방법 : daisy chain, shared direct access)daisy chain : port와 연결된 I/O chain

shared direct access : common bus가 여러개의 I/O 장치들에 연결됨 - Controller : Port, Bus, I/O 장치들을 운영함

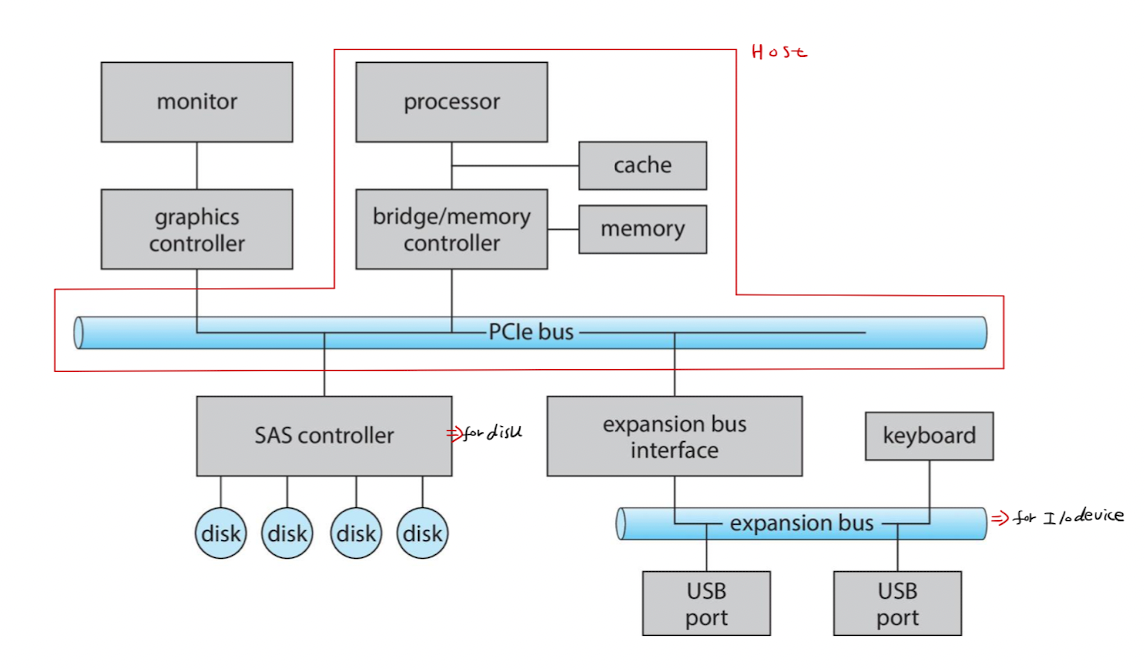

Typical Bus Structure

- PCIe bus : 프로세서 - 메모리 부시스템과 고속 장치의 연결

- Expansion bus : 저속 장치의 연결 (키보드. 병렬 포트, 직렬 포트)

- SCSI bus : 고속 디스크들의 연결

Controller 와 컴퓨터 프로세서의 통신

-

컴퓨터 프로세서는 Controller의 register에 비트 패턴을 쓰거나 읽음으로 입출력을 실행합니다.

-

Memory Mapped I/O

- Controller의 register들이 프로세서의 주소 공간으로 대응되는 방식입니다.

- register들이 프로세서의 메모리 주소 공간과 일대일 대응하여, 메모리 주소에 데이터를 읽고 쓰는 것으로 장치 제어기의 레지스터에 직접 데이터를 읽고 쓰는 역할을 수행합니다.

-

register 구성

- Status register : 장치의 상태

- Control register : 장치 모드의 변경

- Data-In register : 입력용 자료 레지스터

- Data-Out register : 출력용 자료 레지스터

Polling (폴링)

정의

- Host(CPU)와 I/O 장치 간의 통신을 위한 프로토콜 입니다.

Busy Bit

- Controller는 Status register의 Busy Bit를 통해 상태를 지정합니다.

- 1 : 명령어를 수행하는 중

- 0 : 명령어 수행을 완료 후, 다음 명령어를 기다리는 상태

Command-ready Bit

- Host는 Command register의 Command-ready Bit를 통해 상태를 지정합니다.

- 1 : Controller에게 명령어를 전달한 상태

- 0 : Controller가 명령어 수행을 완료한 상태

작동 방식

- Host는 Controller의 Busy Bit가 0이 될때까지 반복적으로 판독합니다.

- Host는 Command register의 Write Bit를 설정 후, Data-Out register에 작성합니다.

- Host는 Command-ready Bit를 설정 합니다.

- Controller가 Command-ready Bit가 설정되었음을 알아차리고, Busy Bit를 설정합니다.

- Controller는 Command register를 판독하여 명령이 write임을 파악 후, Data-Out Register를 판독하여 2)번에서 작성된 바이트를 가져와서 장치에 출력합니다.

- Controller는 명령어 수행이 완료되었다는 의미로, Command-ready Bit를 클리어 합니다.

그 후, 입출력 성공을 알리기 위해서는 Status register의 error Bit 와 Busy Bit를 클리어 합니다.

Busy Waiting 발생

- 1번 과정에서 장치로부터 입출력 완료를 대기하는 과정에서 발생

- 입출력 장치가 느리다면, 비효율성을 초래합니다.

- Controller가 CPU에게 통보하는 Interrupts방식이 더 효과적입니다.

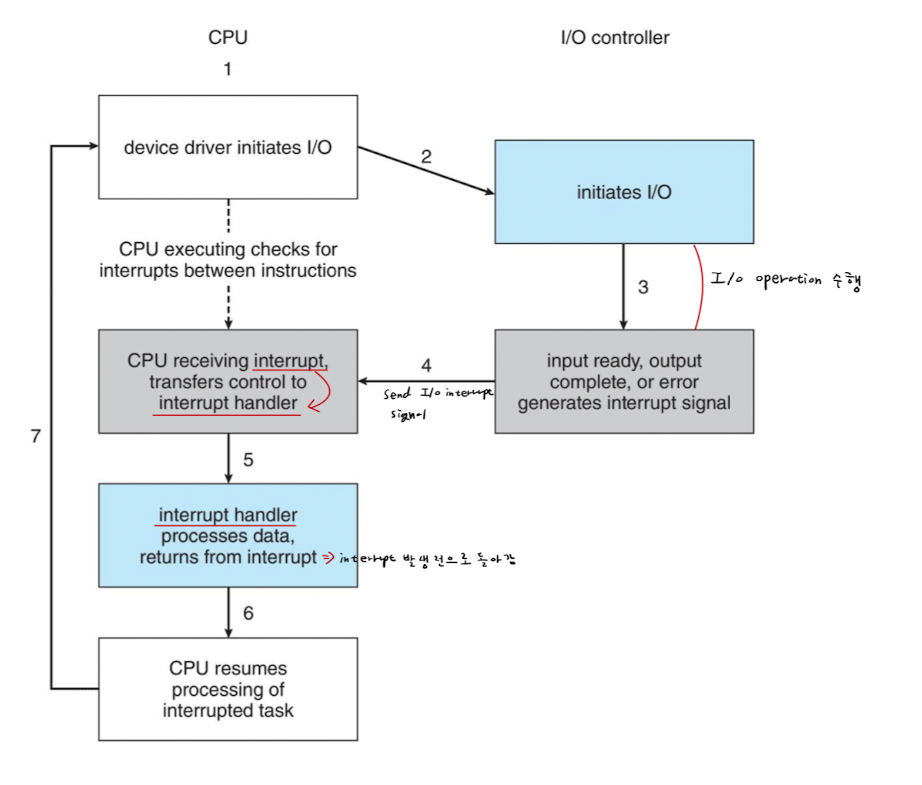

Interrupts (인터럽트)

정의

- CPU는 각 명령어 실행 이후에 Interrupt request line을 확인하여 Controller에 의해 전송된 인터럽트가 있는지 검사합니다.

- CPU가 인터럽트 신호를 감지하면, 현재 상태를 저장 후 Interrupt handler routine으로 이동합니다.

- Interrupt Handler는 인터럽트를 분석하고 해당 처리를 수행한 후, return from interrupt 명령을 수행하여 인터럽트 전의 상태로 복귀합니다.

종류

- Maskable interrupt : 일반적인 인터럽트 - 무시되거나 연기될 수 있습니다.

- NonMaskagle interrupt : 매우 중요한 인터럽트 - 즉시 처리되어야 합니다.

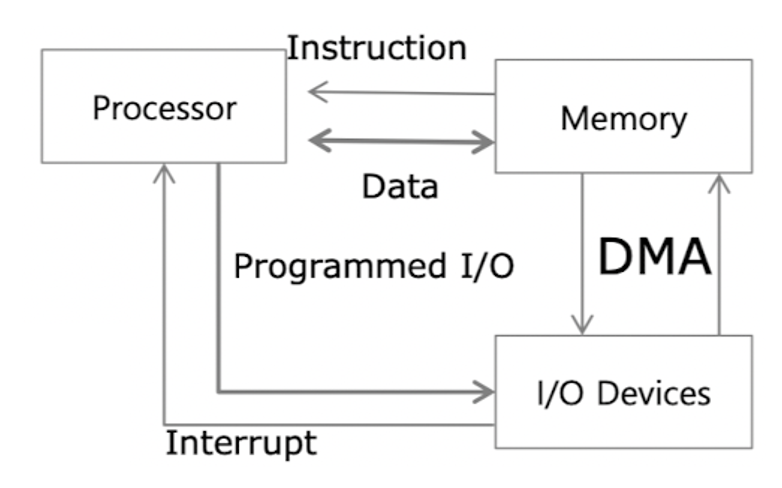

Direct Memory Access (직접 메모리 접근, DMA)

정의

- 용량이 큰 데이터의 이동을 위하여 programmed I/O 방식을 회피하는 것

Programmed I/O (one byte at a time) : 상태 비트를 감시하고 한번에 1바이트씩 controller register에 옮기는 것

작동 방식

- DMA 전송을 초기화 하기 위해서, Host(CPU)는 DMA command block (명령어 블럭)을 메모리에 작성합니다.

DMA command block : 아래 항목들을 포함하고 있습니다.

- Source and Destination addresses

- Read or Write mode

- Count of bytes : 전송 바이트 수의 카운터 - CPU는 DMA command block의 주소를 DMA controller에 기록 후, 다른 작업을 계속합니다.

- DMA Controller는 직접 메모리 버스를 운영하여 한 워드씩 전송합니다.

Direct Virtual Memory Access (직접 가상 메모리 접근, DVMA)

- Memory Space가 Virtual Address Space를 인지하고 있기 때문에, 더 효율적 입니다.

- CPU의 interrupt와 Main Memory 사용 없이 두개의 메모리 대응장치 사이에서의 전송 가능

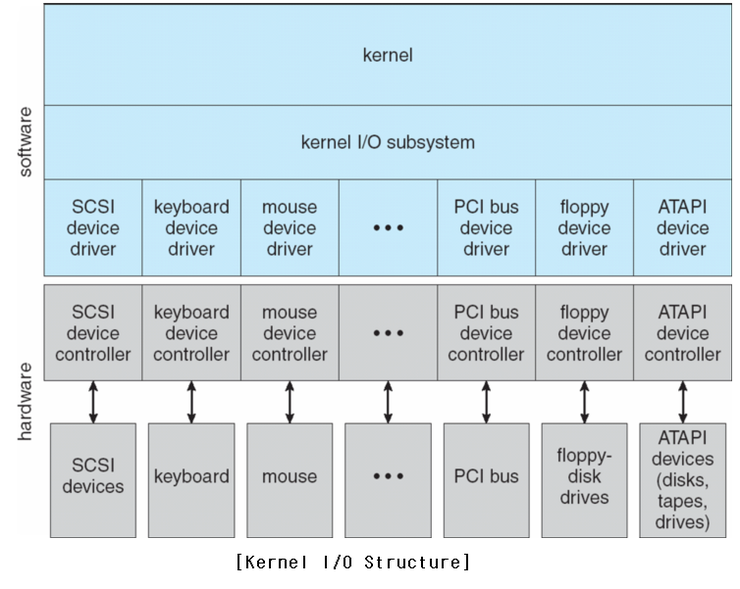

Application I/O Interface

I/O 장치들이 일관된 방법으로 다루어 질 수 있도록, 운영체제가 인터페이스를 구성하는 기술을 설명합니다.

인터페이스 : 공통적인 특징을 가진 I/O 장치들의 표준 함

-

Device Driver라 불리는 커널 내의 모듈들은 각 I/O 장치들을 위한 구체적인 소스 코드들을 제공하여 바로 위에서 정의한 "인터페이스"의 표준 함수들을 내부적으로 수행합니다.

-

Device Driver 계층의 목적

- 여러 I/O 하드웨어들의 차이점을 숨기고, 이들을 간단한 표준 인터페이스들로 보이도록 포장하는 것 입니다.

- 이렇게 포장된 것 들은 상위의 kernel I/O subsystem에 제공됩니다.

- 이렇게 되면, I/O subsystem은 하드웨어와 독립적으로 되어서 운영체제 개발자의 작업을 간단하게 해줍니다.

-

한가지 문제점은 운영체제마다 장치 드라이버 인터페이스에 대한 규격이 다르다는 것 입니다.

- 따라서 새로운 장치를 위한 드라이버가 함께 제공되어야 합니다.

Kernel I/O Subsystem

커널은 입출력과 관련된 많은 서비스를 제공합니다.

Scheduling

- 입출력 요청에 대한 실행 순서를 결정합니다.

- 운영체제 개발자들은 waiting queue를 이용하여 구현하고 있습니다.

Buffering

- I/O 장치와 응용프로그램 사이에 자료가 전송되는 동안에, 그 자료를 임시로 저장하는 메모리 영역입니다.

- 필요한 이유

- 자료의 생산자와 소비자 사이에 속도가 다른 것에 대처하기 위함이다.

이중버퍼링(double buffering)을 이용하여 자료의 생산자와 소비자간의 속도 차이를 흡수 할 수 있다. - 서로 다른 장치들 사이에 사용되는 자료 전송 크기가 다른 것을 극복하기 위한 것이다.

특히 컴퓨터 네트워킹에서 많이 발생하며 송신자의 큰 패킷을 작은 패킷으로 나누어 전송하며 수신자는 나누어진 패킷을 버퍼에서 결합한다. - 응용프로그램의 copy semantic를 지원하기 위함이다.

이는 디스크에 쓰기를 할 때 호출할 시점의 버퍼에 있는 내용만 디스크에 쓴다는 것을 보장한다.

- 자료의 생산자와 소비자 사이에 속도가 다른 것에 대처하기 위함이다.

Caching

- 캐시는 자주 사용될 자료의 복사본을 저장하는 빠른 메모리 영역이다.

- 캐시된 복사본을 사용하는 것이 원래 자료를 사용하는 것보다 더 효율적이다.

- 캐싱과 버퍼링은 두 가지 서로 다른 기능이지만 메모리의 한 영역이 두 가지 목적 모두를 위해 사용될 수도 있다.

버퍼들은 읽기/쓰기가 빈번하거나 또는 프로세스들 간에 공유되어야 하는 파일들을 위한 캐시로도 사용될 수 있다.

Spooling

- 교차해서 동작될 수 없는 프린터 같은 장치를 위해, 출력 자료를 보관하는 버퍼 입니다.

- 많은 응용프로그램들이 출력 자료를 만들어 내면 각 출력들이 다른 프로그램의 출력과 섞이지 않도록 운영체제는 모든 출력을 가로챔으로써 이 문제를 해결한다.

Error Handling

- 보호되는(protected) 메모리를 사용하는 운영체제는 많은 종류의 하드웨어 및 응용 프로그램 오류에 대처할 수 있으며 그러한 오류가 일어나도 시스템 전체의 마비로까지 확대되지 않는다.

I/O Protection

- 사용자 프로세스는 고의든 아니든 불법적인 입/출력 명령을 시도함으로써 정상적인 동작을 방해 할 수 있다.

- 사용자가 불법적인 입/출력을 못하게 하기 위해 모든 입/출력 명령은 특권 명령(privileged instruction)으로 정의한다.

따라서 사용자는 입/출력 명령을 직접 실행할 수 없다. 대신 운영체제가 입/출력을 실행하도록 시스템 호출을 실행 한다.

Kernel Data Structure

- 커널은 입/출력 구성 요소에 대한 상태 정보를 유지해야 한다.

커널은 네트워크 연결, 문자 장치 통신 그리고 다른 입/출력 활동을 관리하기 위해 여러 비슷한 구조를 사용한다.