Setup Time & Hold Time

Setup time은 Flip Flop이 정상적으로 데이터를 캡처하기 위해 clock edge 이전에 input data value가 유지되어야 하는 시간이고,

Hold time은 Flip Flop이 정상적으로 데이터를 캡처하기 위해 clock edge 이후로 input data value가 유지되어야 하는 시간이다.

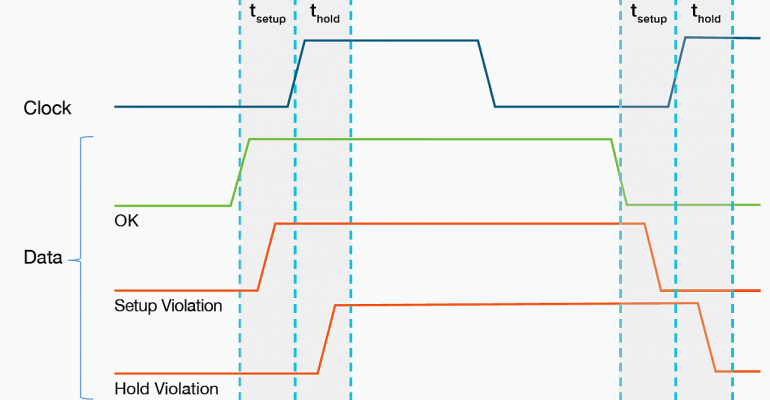

위 파형을 기준으로 Data가 FF의 input이고, posedge 방식의 FF라고 가정하자.

그러면 위 파형에서 clock이 0->1 이 되는 순간 Data를 캡처하여 output으로 내보내게 된다.

이때 "Setup Violation" 케이스와 같이 clock edge를 기준으로 setup time 도중에 값이 변경되었으므로 정상적인 동작을 보장하지 못하게 되고, (사실 도중에 값이 변경되었다기 보다는 이전의 combi logic이 크거나, routing path가 길거나 하는 등의 이유로 input data가 늦게 도착했다고 보는것이 맞긴 하다.)

"Hold Violation" 케이스의 경우, hold time 도중에 값이 변경되었으므로 마찬가지로 정상적인 동작을 보장하지 못하게 된다.

Setup Time Violation 해결방안

그래서 Setup time violation이 발생하면 어떻게 해결할까?

먼저 가장 쉬운 방법이 있다. 그냥 주파수를 낮추면 된다.

하지만 쉬운만큼 성능에 치명적인데, 같은 디자인에서는 clock 주파수와 성능(속도)이 비례하기 때문에 주파수를 낮추면 성능도 당연히 하락하게 된다. 그래서 이런 해결방식은 뒤에 나오는 해결방안의 적용이 불가능한 상황이나, IP 라이센싱을 받아 SoC에 integration 할 때, 내부 RTL 수정이 불가할 때만 사용하는 방식이다.

두번째는 문제가 되는 Path에 FF를 추가하는 것이다. setup time violation 의 경우 보통 combi logic depth가 깊어 거기서 발생하는 delay로 인해 setup time 이전에 FF 입력이 도착하지 않기 때문에 발생한다. (STA 엔지니어 입장에서는 다를 수 있지만..)

따라서 critical path에 해당하는 FF 사이의 combi logic을 잘 쪼개어 사이에 FF를 넣어주면 된다. 현업에서는 pipeline이나 register slice를 추가한다고 말한다.

그런데 디자인을 고려하지 않고 무작정 넣어버리게 되면 당연히 이상한 동작을 보일 것이다. 따라서 해당 FF의 output에 dependency가 있는 다른 FF들도 FF를 추가해야 할 것이다.

Hold Time Violation 해결방안

Hold Time Viloation은 Setup과 반대로 FF 사이의 delay가 너무 짧아서 값이 hold time 중간에 스위칭 되어버리는 상황에 발생한다.

따라서 buffer를 추가하는 등 combi logic을 중간에 넣어주면 된다.

Hold 와 Setup time violation 중 치명적인 걸 뽑자면 hold일 것이다. setup은 violation이 있는 채로 칩이 나와도 최악의 경우 실제 clock 주파수를 낮춰서 인가하면 동작이 가능은 하지만 hold는 그렇지 않다.

하지만 Hold time violation 의 경우 STA 후에 hold violation path에 buffer를 넣어주면 되기 때문에 RTL design 엔지니어 입장에서는 크게 고려대상이 아닌 것 같다. (사실 내가 PI업무를 해본적이 없어서 잘 모르겠다)

Appendix

최대동작주파수 구하기

Tsetup + Tc2q + Tcomb ≤ Tclk + Tskew

Freq = 1 / Tclk

Tsetup: setup time

Tc2q: clock to q(FF의 ouput)

Tcomb: combination logic delay

Tskew: clock skew

STA (Static Timing Analysis)란?

RTL design 단계에서는 칩 동작을 Noise, 온도 등의 이슈들을 고려하지 않고 이상적으로 보고 설계한다.

따라서 해당 이슈들을 고려하여 violation을 체크하여 타이밍을 검증하는 단계가 필요한데, 그게 STA이다.

보통 PrimeTime을 사용한다.