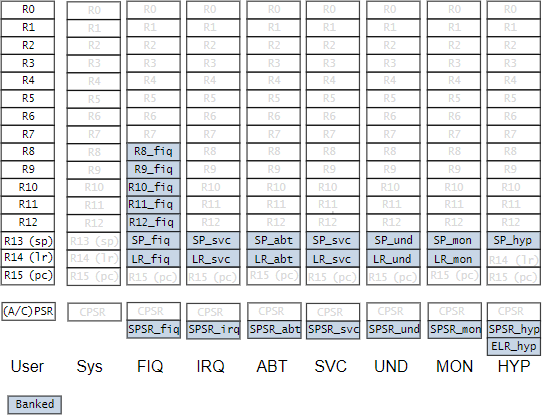

ARMv7 Registers

1. General Purpose Register

- R13: Stack pointer

- R14: Link Register

- R15: Program Counter

- CPSR: Current Program Status Register

- SPSR: Saved Program Status Register

Banked Register: 특정 execution mode에서만 접근 가능한 레지스터. "Reg_<mode>"로 표기

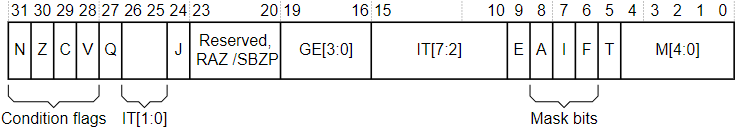

2. CPSR & SPSR

2.1. CPSR

- N[31]: 연산 결과가 음수

- Z[30]: 연산 결과가 0

- C[29]: carry 발생

- V[28]: overflow 발생

- A[8]: asynchronous abort 비활성화

- I[7]: IRQ 비활성화

- F[6]: FIQ 비활성화

- M[4:0]: execution mode

2.2. SPSR

- 익셉션 발생 전 시점의 CPSR을 저장

- 익셉션 발생 과정에서 CPSR이 SPSR로 복사

- 익셉션 처리 후 복귀 시 SPSR을 CPSR로 로딩

Example: SVC (0x13) → IRQ (0x12)

- SPSR_irq.M = 0x13

- CPSR.M = 0x12

- IRQ exception handler에서 SPSR_irq.M, R14_irq를 스택에 백업

- exception 처리 후, CPSR.M = 0x13, PC = R14_irq

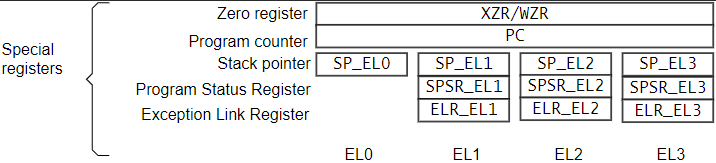

ARMv8 Registers

1. General Purpose Register

- x0~x30: 64bit GPR

- w0~w30: 32bit GPR

2. Special Register

- SP_ELx: 각 exception level에서 실행 중인 프로세스의 스택 최상단 주소를 가리키는 스택 포인터

- ELR_ELx: EL x로 exception이 발생할 때 복귀 주소 저장

- PC: Program Counter

- XZR/WZR: Zero Register

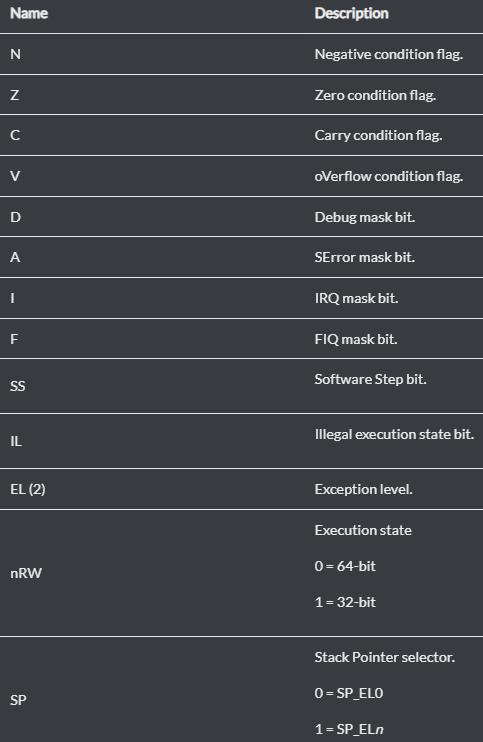

3. PSTATE & SPSR_ELx

3.1. PSTATE (Processor State)

-

N[31]: 연산 결과가 음수

-

Z[30]: 연산 결과가 0

-

C[29]: carry 발생

-

V[28]: overflow 발생

-

D[9]: debug exception 비활성화

-

A[8]: asynchronous abort 비활성화

-

I[7]: IRQ 비활성화

-

F[6]: FIQ 비활성화

-

M[3:0]: exception level

Mode Bit를 읽을 떄에는 CurrentEL system register을 통해 값을 읽는다.

-

SS[21]: exception 발생 후 debuggger에서 siggle step 활성화

-

IL[20]: 이 bit 설정 시 이후 실행되는 명령은 illegal execution으로 판단하여 exception 발생

3.2. SPSR_ELx

- EL x로 exception 발생 시 PSTATE가 SPSR_ELx로 백업

- EL x로 exception 발생 전의 PSTATE를 SPSR_ELx가 저장

- 복귀 시 PSTATE에 SPSR_ELx를 로딩 및 ELR_ELx로 분기

Example: EL1 IRQ

- ELR_EL1 = PC, SPSR_EL1 = PSTATE, IRQ exception handler로 분기

- handler에서 SPSR_EL1, ELR_EL1 백업, interrupt service routine 호출

- ISR 처리 후 handler로 복귀

- IRQ 발생 전으로 복귀하기 위해 PSTATE = SPSR_EL1, PC = ELR_EL1

4. System Register

- 시스템 세부 속성 설정을 위한 레지스터

- MSR, MRS instruction을 이용하여 접근

- 시스템 레지스터에 접근하기 위한 최소 exception level 존재

시스템 레지스터 중 하나인 TTB0_EL1의 접근을 위한 최소 exception level은 EL1이다. 즉 EL0에서 접근 불가하고, EL1, EL2, EL3에서 접근 가능하다. 만약 최소 exception level을 만족하지 못하고 접근하면 synchronouse exception이 발생한다.

- SCTLR_ELx: System Control Register. MMU, cache, alignment 검사 등 architecture 주요 기능 제어

- ACTLR_ELx: Auxiliary Control Register. processor 관련 주요 기능 제어

- SCR_EL3: Secure Configuration Register. secure state, EL3 exception으로 트랩되는 세부 동작 설정

- HCR_EL2: Hypervisor Configuration Register. 가상화 시스템 주요 동작 방식, EL2 exception으로 트랩되는 세부 동작 설정

- MIDR_EL1: Main ID Register. 소프트웨어 실행 시 processor 관련 정보 얻어옴 (revision, version)

- MPIDR_EL1: Multiprocessor Affinity Register. core, cluster ID를 multicore system에서 식별

- SCTLR_ELx: Cache type Register. cache 관련 정보 식별

4.1. System Register Access Instruction

- MRS: GPR ← system register

- MSR: system register ← GPR

MRS, MSR이 아닌 MOV로 접근 시 memory abort type인 Synchronous Exception 발생