다중 단계 페이징 시스템

32비트 시스템에서 4KB 페이지를 위한 페이징 시스템은

- 하위 12비트는 오프셋

- 상위 20비트는 페이징 번호

2^20(1,048,576)개의 페이지 정보가 필요하다.

이를 해결하기 위해 페이징 정보를 단계별로 나누어 생성해 필요없는 페이지를 생성하지 않도록해 공간을 최소화할 수 있다.

- 페이지 번호를 나타내는 bit로 구분해 단계를 나눔

MMU와 TLB

MMU(Memory Management Unit)는 물리 주소 확인을 위해서 메모리를 수시로 확인해야 한다.

메모리에 접근하는데 시간이 오래 걸리기 때문에 메모리를 수시로 확인을 하는 작업은 성능 상 문제를 일으킬 수 있다.

이를 해결 하기 위해서 TLB라는 장치가 등장하게 된다.

- TLB(Translation Lookaside Buffer): 페이지 정보 캐시

- 페이지 정보를 임시 저장

- CPU가 Virtual address 정보를 요청하면 TLB에서 페이지 정보를 확인

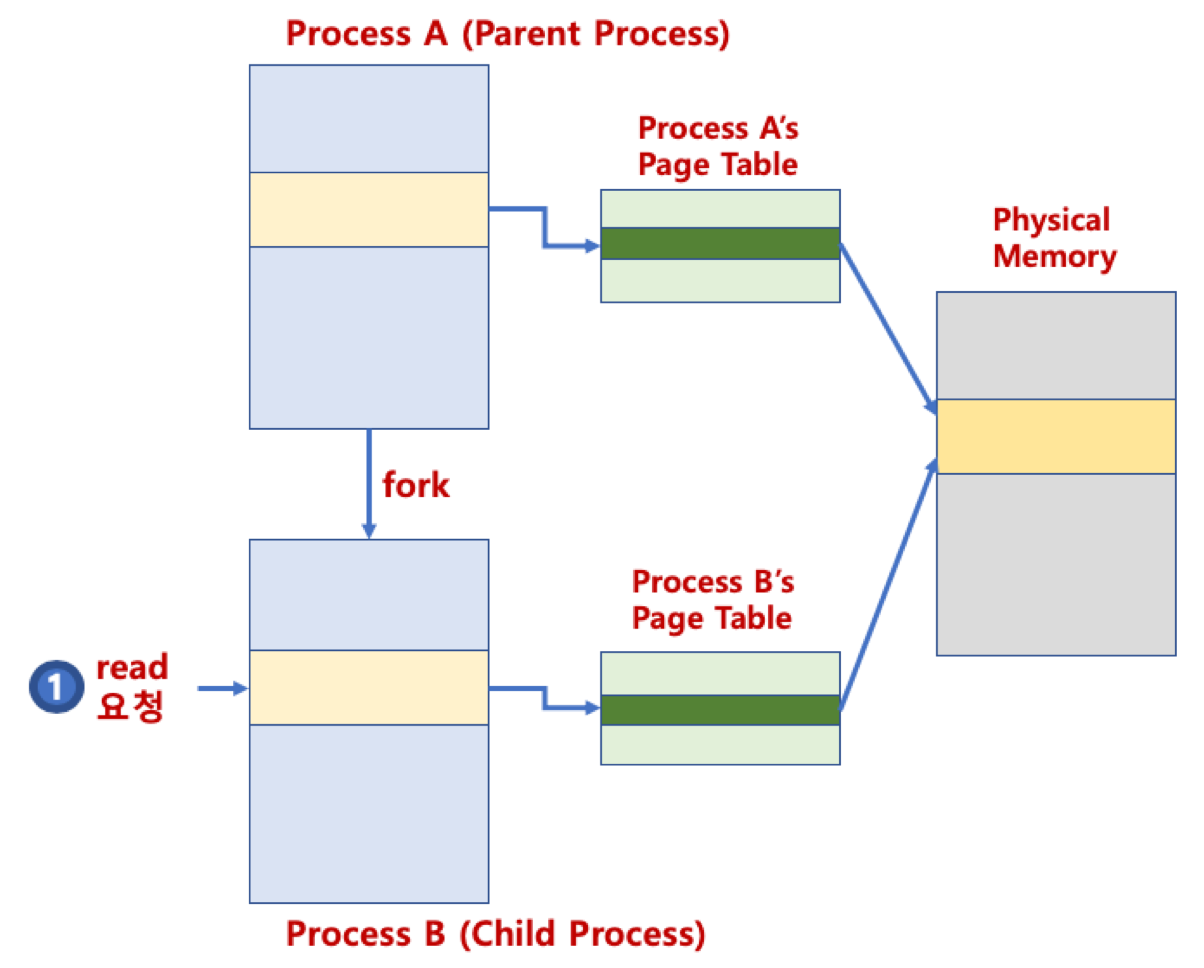

페이징 시스템과 공유 메모리

공간 절약과 메모리 할당 시간을 절약하기 위해 프로세스간 동일한 물리 주소를 가리킬 수 있다.

프로세스 A의 공간과 프로세스 B의 공간이 공유된다고 가정해본다면

물리 메모리에는 A의 공간과 B의 공간을 각각 할당하는게 아니라 하나의 공간을 할당해주고 각 프로세스의 페이지 테이블은 할당된 공통된 공간의 주소를 참조한다.

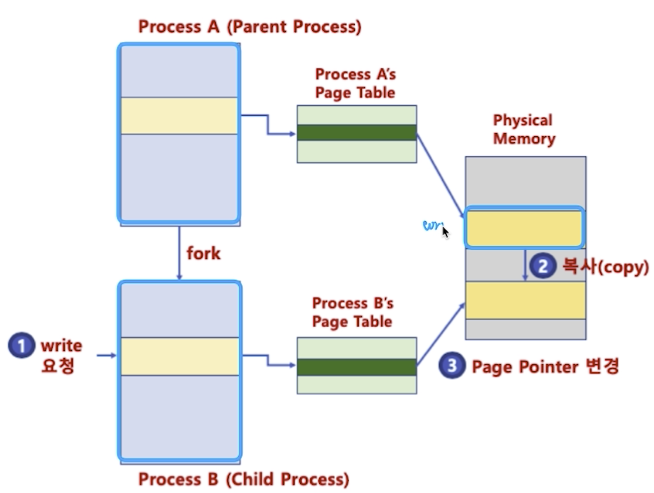

물리 주소 데이터 변경 시

물리 메모리 주소에 데이터 수정을 요청할 때, 물리 메모리 주소를 복사 할 수 있다.

- 프로세스 생성 시간을 단축시킬 수 있음

- 커널, 공유메모리와 같이 공유하는 데이터는 물리 메모리에서 공간을 공유 가능

- 페이지 테이블의 페이지 물리 메모리 주소만 올바르게 참조할 수 있도록

- 페이지 테이블의 페이지 물리 메모리 주소만 올바르게 참조할 수 있도록