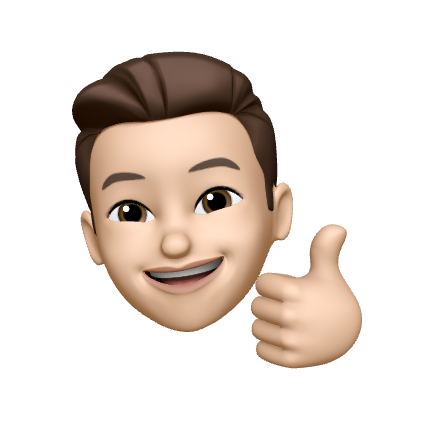

📕 시스템의 기본 요소

Processor

- 중앙처리장치(CPU)로 각종 명령을 해석하고 수행하는 역할을 한다.

Main Memory

- 메인 메모리에 실행할 프로그램을 올리고 실행한다.

- 한 번에 한 명령어씩 실행 가능하다.

- 휘발성으로 컴퓨터가 꺼지면 데이터가 날아간다.

I/O modules

secondary memory devices

- 데이터들을 저장하며 비휘발성이다.

- 프로그램을 실행하면 메인 메모리에 프로그램을 올린다.

- 시스템 내부가 아닌 외부장치로 인식한다.

communications equipment

- 네트워크와 관련된 장치들

terminals

- 사용자가 컴퓨터 시스템과 interaction 하기 위한 디바이스(e.g 마우스, 키보드, 프린터)

System bus

- 프로세서, 메인 메모리, 그리고 I/O 모듈들이 통신할 수 있게 연결해준다.

📘 CPU의 요소

PC

- Program Counter

- 다음에 실행할 명령의 주소를 저장한다.

IR

- Instruction Register

- 현재 처리할 명령어를 저장한다.

MAR

- Memory Address Register

- 데이터나 명령들을 주고 받을 위치를 지정해준다.

MBR

- Memory Buffer Register

- 데이터, 명령들을 주고 받는 중간 저장 장소 역할을 한다.

MAR, MBR을 사용하는 이유

CPU에서는 한 번에 하나의 명령어씩 가져와서 수행하는데 메인 메모리에서 바로 가져와서 사용할 수 없다. (연결되어 있지 않으므로)

또한 CPU에는 연산의 결과를 저장하거나 데이터를 불러올 때 저장할 범용레지스터가 많이 있는데, 마찬가지로 메인 메모리에서 바로 사용할 수 없다.

CPU와 레지스터들을 모두 연결하려면 경우가 너무 많기 때문에 설계하기 복잡해지고 어려워진다.

따라서 CPU에는 메모리에 대한 최소한의 연결 정보만을 저장하기 위해 MAR, MBR을 사용한다.

PSW

- Program Status Word

Condition codes

- 연산의 결과를 확인하여 양수, 음수, 0, overflow인지를 나타낸다.

- PSW내에서 2bit를 사용한다.

Interrupt enable/disable

- interrupt가 걸렸는지, 걸리지 않았는지 나타낸다.

- PSW내에서 1bit를 사용한다.

Supervisor/user mode

- Supervisor instruction인지 user instruction인지 확인하여 권한을 줄 때 사용한다.

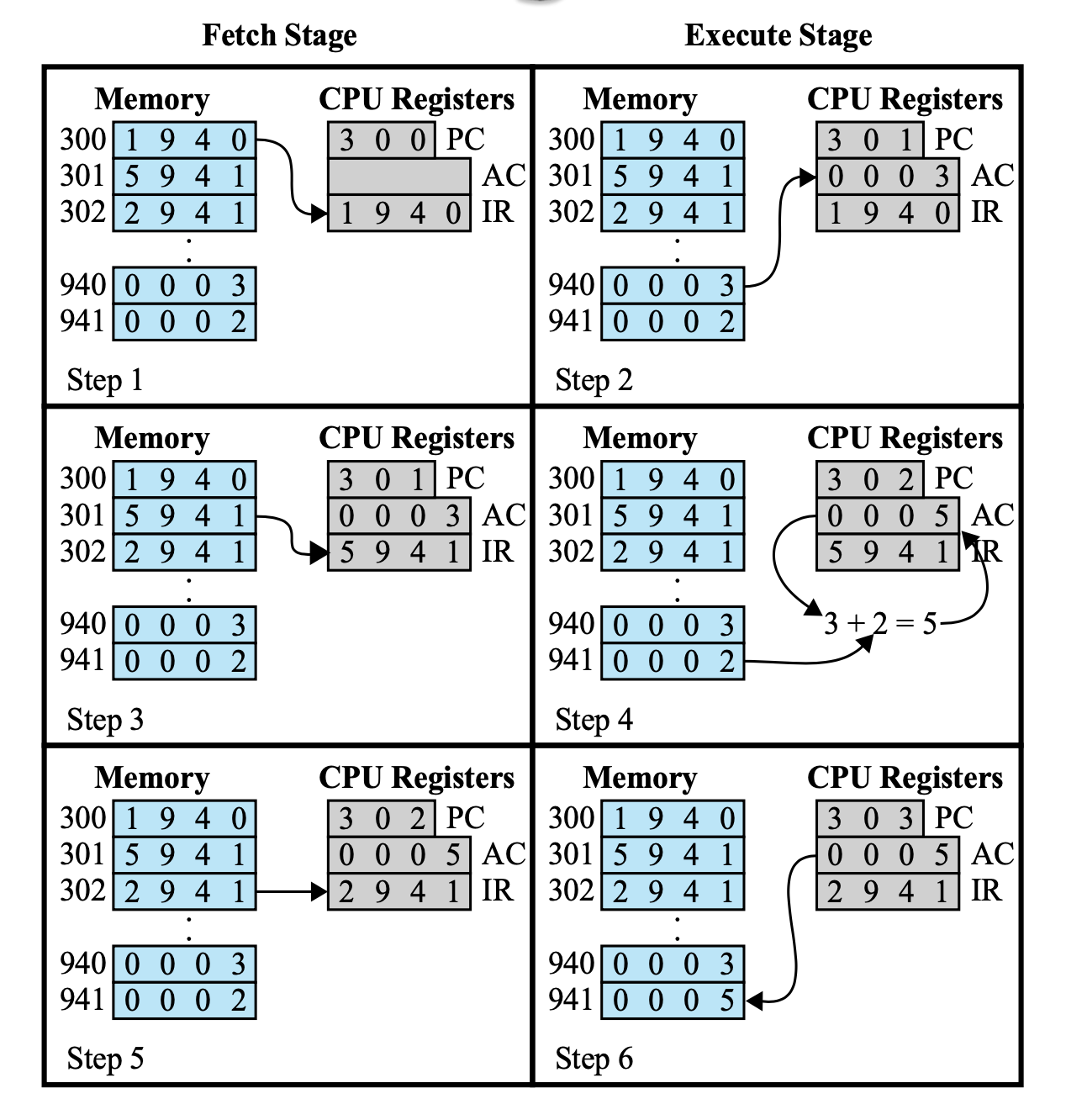

📗 명령 실행

명령 실행은 두 단계로 이루어진다.

Fetch Stage

CPU가 메인 메모리로부터 명령어를 가져오는 단계

Execute Stage

명령어를 분석하고 실행하는 단계

명령 실행 예시

명령 실행의 예시를 통해 과정을 알아보자

Fetch Stage#1 (Step1)

- PC → MAR, MAR에 넘기자마자 PC에는 다음에 실행할 명령어를 저장한다.

- MAR에 있는 번지의 명령을 MBR로 가져온다.

- MBR → IR

Execute Stage#1 (Step2)

-

명령 분석

IR에 있는 명령을 분석한다.

IR 내의 첫 번째 4비트는 메모리에 저장된 값이 AC(Accumulator Register)에 적재될 것을 나타내고, 나머지 12비트는 그 주소를 명시한다.

-

IR의 주소 부분이 MAR로 이동한다.

-

메모리에서 MAR 부분을 읽어 MBR에 저장한다.

-

MBR → AC

Fetch Stage#2 (Step3)

- PC → MAR, PC ← PC + 1

- MAR → MBR

- MBR → IR

Execute Stage#2 (Step4)

-

명령 분석

앞의 4비트는 덧셈을 나타내고 나머지 12비트는 덧셈할 값의 주소를 명시한다.

-

IR의 주소 → MAR

-

Memory[MAR] → MBR

-

AC ← AC + MBR

Fetch Stage #3 (Step5)

- PC → MAR, PC ← PC + 1

- MAR → MBR

- MBR → IR

Execute Stage#3 (Step6)

-

명령 분석

앞의 4비트는 저장을 나타내고 나머지 12비트는 저장할 주소를 명시

-

IR의 주소 → MAR, AC → MBR(메모리와 AC가 연결되어 있지 않기 때문에)

-

Memory[MAR] ← MBR

📚 참고 및 이미지 출처