I. Abstract

본 논문은 결합형 바랙터 부하 전송선(VLTL, Varactor-Loaded Transmission Line) 위상천이기와 주파수 배수기(frequency multiplier)가 통합된 CMOS 송신 칩을 활용한 Ka-대역 빔 조향(beam-steering) 송신기를 제안한다.

단일 VLTL을 따라 배치된 단결합(short-coupled) 라인 커플러들은 다중 위상 출력을 제공하면서, 전송선 전체에서의 임피던스 불일치 및 전력 불균형 문제를 최소화한다.

VLTL은 전송선 길이에 따라 누적되는 위상 변화 특성을 지니므로, 각 채널마다 개별 위상천이기를 사용하는 기존 구조에서 요구되던 넓은 위상 제어 범위의 부담을 줄일 수 있다.

또한, 8배 주파수 배수기(×8 multiplier)를 통해 기준 주파수(reference frequency)에서 필요한 위상 변화량을 줄임으로써, 바랙터의 조정 범위가 감소하고, 결과적으로 전송선의 특성 임피던스 변화가 최소화되어 임피던스 정합(impedance matching)이 유지된다.

이를 바탕으로 약 4 GHz의 낮은 기준 주파수에서 동작하는 단일 VLTL 위상천이기를 사용해, 32 GHz 위상 배열(phased-array) 송신기를 구현하였다.

제작된 1×4 위상 배열 송신기는 단일 제어 전압(single control voltage)만으로 E-평면에서 ±20°의 연속 빔 조향 범위를 달성하였다.

모든 조향 각도에서 사이드로브 레벨(sidelobe level)은 -10 dB 이하,

유효 등방성 복사 전력(EIRP)은 31.6 GHz에서 38.1 dBm,

3 dB 대역폭은 2.4 GHz로 측정되었다.

주요 용어: 위상 배열(phased-array), VLTL, 빔 스티어링, 커플러, 위상천이기, 송신기, 빔포밍, 부하 전송선, 유효 등방성 복사 전력(EIRP)

주요 용어 이론 정리

1. 위상 배열 (Phased-Array)

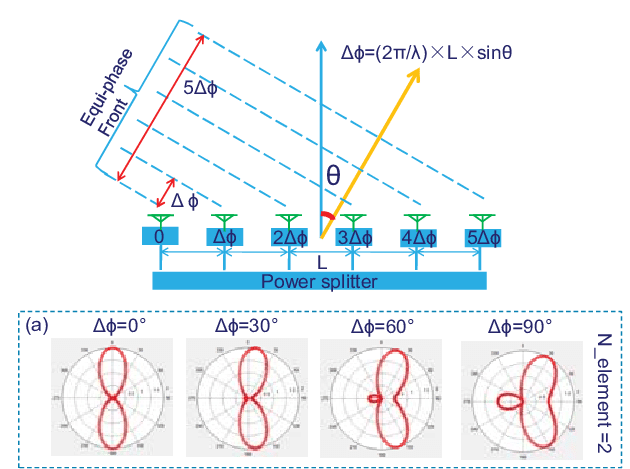

여러 개의 안테나를 일렬 또는 평면 배열로 배치하고,

각 안테나에 서로 다른 위상(phase)을 주입하여

한쪽 방향으로 신호가 보강 간섭(constructive interference) 되도록 만든 시스템.

• : 인접 안테나 간 위상차

• : 파장

• d: 안테나 간 거리

예시:

d =

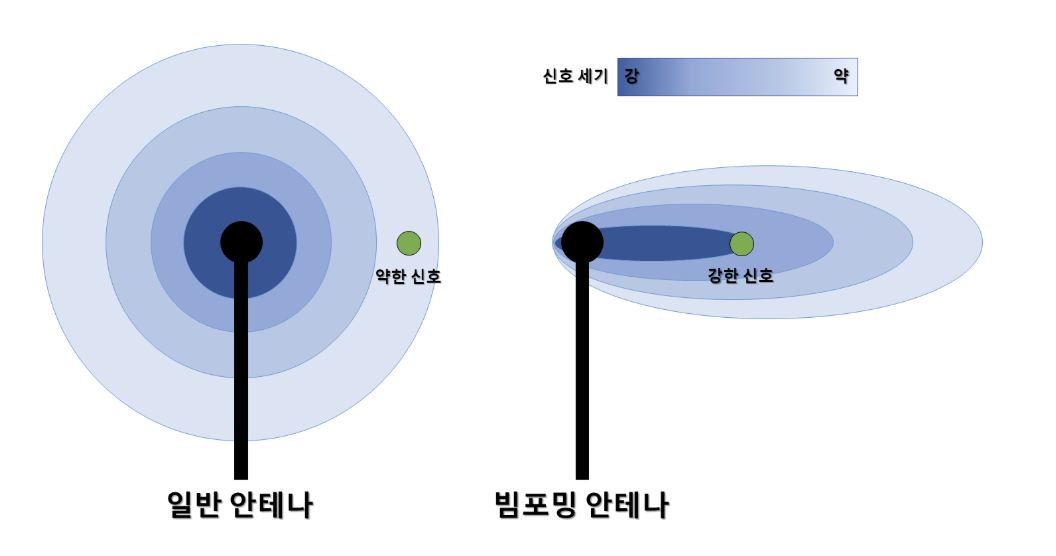

2. 빔포밍 (Beamforming)

신호의 위상과 세기(Amplitude)를 조절하여

원하는 방향의 신호는 강화하고,

불필요한 방향의 신호는 억제하는 기술입니다.

• : 빔포밍 결과 신호

• : 번째 안테나의 입력

• : 세기 , 위상 을 갖는 복소 가중치

→ 의 위상을 바꾸면 빔의 방향이 전자적으로 이동합니다.

3. 빔 스티어링 (Beam Steering)

위상 배열의 핵심 기능으로,

각 안테나에 주는 위상차를 바꿔 빔 방향을 전자적으로 이동시키는 동작입니다.

4. 위상천이기 (Phase Shifter)

RF 신호의 위상만 변경하는 회로입니다.

보통 아래 세 가지 방식으로 구현합니다.

• 바랙터 다이오드 (정전용량 가변)

• PIN 다이오드 (스위칭)

• FET 기반 가변 소자 (아날로그 제어)

*자세한 공부 내용

([위상천이기 기본](http://www.ktword.co.kr/test/view/view.php?no=3123)5. VLTL (Varactor-Loaded Transmission Line)

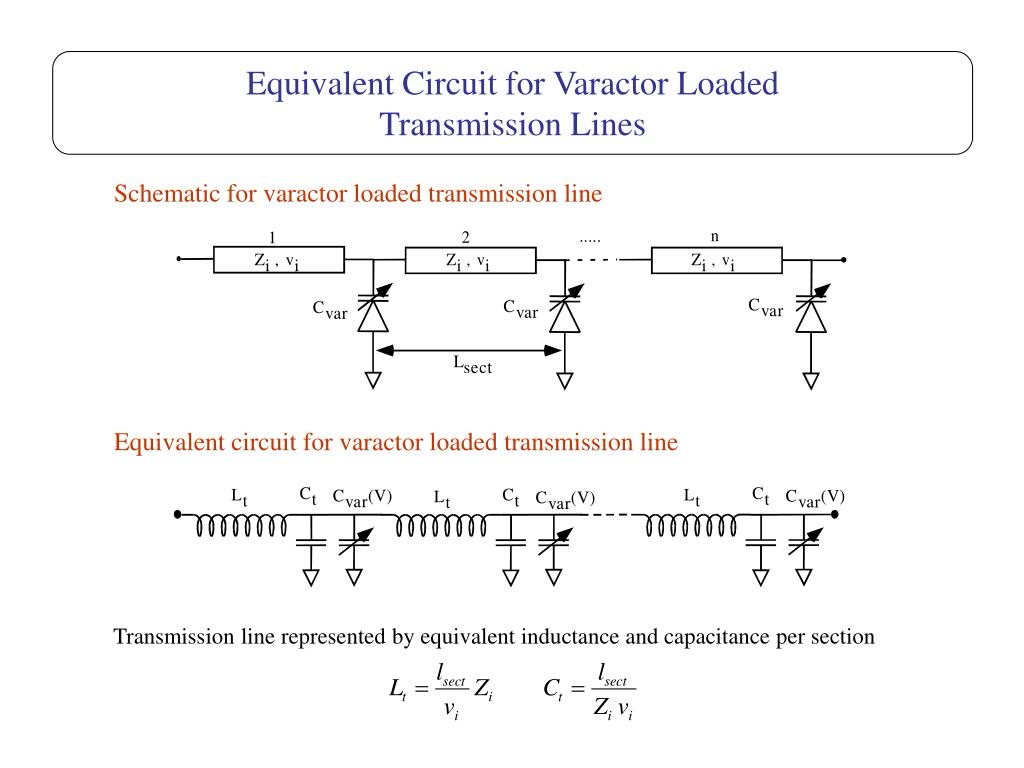

전송선(Transmission line)에 바랙터 다이오드를 주기적으로 연결해

전압에 따라 유효 위상 지연량을 조절하는 구조입니다.

• : 유효 위상 상수

• : 기준 위상 상수

• : 제어 전압에 따른 정전용량 변화

• : 구조 상수

즉, 전압을 바꾸면 선로의 위상이 변하고 빔이 이동합니다.

6. 커플러 (Directional Coupler)

입력 신호의 일부를 원하는 포트로 결합(couple)해 주는 4포트 회로입니다.

전력 분배·측정·다중 위상 생성에 사용됩니다.

• : 결합 계수 (예: 3 dB 커플러 → 절반 전력 분배)

7. 부하 전송선 (Loaded Transmission Line)

전송선에 L, C 소자를 주기적으로 부착해

임피던스와 위상 속도를 제어하는 구조입니다.

• : 부하 후 등가 인덕턴스/정전용량

• : 위상 상수 (이 값이 바뀌면 위상이 변함)

8. EIRP (Effective Isotropic Radiated Power)

송신기의 출력 전력과 안테나 이득을 합친 실질 방사 세기입니다.

즉, “이 송신기가 등방성 안테나라면 몇 dBm을 내야 같은 세기가 될까?”를 뜻합니다.

예시:

II. ELECTRICALLY STEERABLE KA-BAND PHASED ARRAY TRANSMITTER

설계과정

1) 시스템 개요: “저주파 위상 제어 + ×8 배수기 + VLTL”

4 GHz 기준 입력 → VLTL(바랙터 부하 전송선) 위상천이기에서 4개의 누적 위상 출력을 ‘결합’ 방식으로 추출 → 각 채널이 CMOS 송신칩(내부에 ×8 주파수 배수기 + Ka-대역 PA 탑재)을 구동 → 최종 32 GHz 방사. 이로써 낮은 기준 주파수에서 위상 제어를 하고, 배수기가 최종 Ka-대역을 만들어냅니다.

왜 배수기(×8)? 위상 배열에서 목표 조향각 를 만들려면 인접 안테나 간 위상차 가 필요합니다

(식 (1)). 이 위상차를 기준 주파수(4 GHz)에서 만들어두면, 배수비 m 만큼 필요 제어량이 로 줄어듭니다(식 (2)). 즉, 바랙터 정전용량 변화폭을 줄이고, 선로 불연속과 정합 악화를 완화합니다.

(식 (1)) — 인접 요소 간 필요 위상차

(식 (2)) — 기준 주파수에서 필요한 VLTL의 위상 변화량

2) 핵심 부품: “결합형 VLTL 위상천이기”의 설계 논리

2-1. 단위 구간(unit section)과 결합(coupling)

하나의 VLTL로부터 여러 위상을 뽑아야 하기에, 약결합(short-coupled) 라인 커플러로 각 구간에서 위상을 “샘플링”합니다.

기준 주파수에서 주기 180°의 부하(바랙터)를 주면 균등 전력 분배가 체계적으로 담보되어 입력 정합/분배 문제를 줄일 수 있습니다. 그래서 VLTL의 단위 구간 길이를 기준 주파수에서 λ/2로 잡고, 이 단위 구간은 두 개의 T-section(각 90° 등가 전기길이)을 캐스케이드로 구현합니다.

2-2. 바랙터 옵셋 C_0 와 물리 길이 보정

바랙터는 를 중심으로 로 가변됩니다. 보어사이트(정면) 지향 시 로 인해 T-section의 물리 길이는 로 줄여야 등가 전기길이 90°가 맞춰집니다(식 (4)). 이후 ABCD 매트릭스 비교로 를 구합니다(식 (5)–(10)).

2-3. 수치 선택(설계 치)과 의미

상용 바랙터 MACOM MAVR-000120(≈140–920 fF)을 사용. 반복 계산 후 =280 fF로 채택. 이때 단위 T-section 감소각

목표 조향각 ±20°, 요소 간격 조건에서, 기준 주파수에서 단위 구간의 총 위상은 169°–191°가 되어야 함(식 (3) 해석). 이를 달성하려면 단위 T-section 유효 위상 변화 \Delta\theta_e=5.5°, 해당에 필요한 정전용량 변화

이때 계산된 선로 임피던스 , → 반사손실 17 dB 이상 확보. 해석과 EM 시뮬이 잘 맞음(169°/191° 포인트 재현).

3) 프로토타입 VLTL 측정: “필요 위상·정합·주파수 의존성”

위상 조절 범위(Fig. 4(a)): V_c=2\to12 V에서 단위 섹션 평균 위상 변화 37.7°, 조향에 필요한 169°–191° 차이를 V_c≈3.4\to12 V에서 달성. 바랙터 추정치는 ≈175–430 fF, 해석치와 근접. 칩 로딩 무시 가정이 타당함을 시사.

S-파라미터(Fig. 4(b)): 입력 반사손실 11.5–22.3 dB, 삽입손실 19.4–22.5 dB(4 포트 전체 경로 기준). 채널 간 삽입 손실 불일치는 유한한 반사손실/선로 감쇠에서 기인 → 커플러 결합비 최적화로 개선 여지. 본 모듈에서는 칩 내 인버터 버퍼의 충분한 이득이 ×8 배수기 입력 레일-투-레일 스윙을 보장해, 채널 간 구동 편차를 보정.

주파수 의존성(Fig. 4(c)): 기준 4 GHz 주변에서 주파수가 올라갈수록 위상 제어 범위 증가. 예) 3.75 GHz→평균 33.8°, 4.25 GHz→44.5°. (기준선로의 위상상수 증가로 자연스러운 결과)

4) CMOS 송신 칩 아키텍처: “4상 생성 → ×8 → PA”

공정/구성: 28-nm CMOS SOI, 블록은 4상(Quadrature) 발생기 + ×8 배수기 + Ka-대역 PA. 32 GHz 출력을 위해 입력은 약 4 GHz 단일종단. 트랜스포머 발룬 + RC 폴리페이즈로 4상을 만들고, 인버터 버퍼 체인으로 손실을 보상·레일-투-레일 스윙 확보 → 저주파에서 매칭망 면적 부담 없이 ×8을 구동.

×8 배수기: 1단 쿼드러플러(4상 전류 결합 + 푸시-푸시)로 4고조파를 단일 트랜스포머 부하에서 전압으로 변환 → 2단 푸시-푸시 더블러로 ×8 완성. 인버터-트랜스포머 공진으로 고조파 추출을 돕고, 매칭 없이 다음 단계 구동(대역폭 제한으로 고차 고조파 억제).

PA: 2단(드라이버 차동 CS + 파워 차동 캐스코드), 전단/후단 모두 트랜스포머 매칭, 모든 스테이지에 크로스-커플드 중화 커패시턴스로 안정도/이득 개선. 다이 1.26 mm × 0.44 mm. 칩 측정: 입력 3 dBm 기준, 32–32.8 GHz에서 17.5–18.2 dBm 출력, 28.8–35.2 GHz에서 편차 1.5 dB(광대역).

고조파 억제: 시뮬 최소 29.6 dBc, 실측 최소 23.2 dBc(입력 주파수 스윕 전체), 4 GHz 지점에서 36 dBc. (배수기 누설·스퓨리어스를 충분히 억제)

⸻

5) 안테나/모듈 통합: “RT/Duroid + FR-4 적층, d=0.7λ 간격”

적층 구조: 위에는 RT/Duroid 패치 배열, 아래 4-레이어 FR-4에 VLTL/드라이버/전압증폭/DC 바이어서 구현. 에폭시로 접합, FR-4에 에어 캐비티를 파서 칩을 노출 GND면 위에 탑재. GCPW 50 Ω 라인으로 VLTL→칩 입력을 와이어 본딩으로 연결. 요소 간 간격 d=0.7\lambda.

패치 배열(1×4 수직): 각 요소는 90°로 꺾인 마이크로스트립 급전, 임피던스 매칭용 오픈 스터브는 상호 결합 저감을 위해 45°로 꺾음. 칩→안테나 전송은 와이어 본딩→비아→마이크로스트립으로 이어지는 Ka-대역 전이 네트워크를 설계.

III. PHASED ARRAY TRANSMITTER MODULE MEASUREMENT RESULTS

1) 측정 셋업과 모듈 개요

모듈은 FR-4(하부: 위상천이기/구동/바이어스)와 RT/Duroid(상부: 패치 안테나)를 적층해 제작했으며, 사진은 Fig. 14에 제시됩니다. 빔 패턴 측정 셋업은 Fig. 15로, 4 m 거리에서 23 dBi 혼(horn) 안테나를 사용했습니다.

2) 방사 패턴(32 GHz) 측정 결과

정규화 빔 패턴(E/H-plane): 32 GHz에서 E-plane 3 dB 빔폭 17°, H-plane 56°를 달성했습니다. 모든 스캔 각도에서 사이드로브 ≤ −13.5 dB, E-plane의 peak-to-null ≥ 22 dB(0°에서)로 보고됩니다. (Fig. 16a)

해석:

E-plane 17°는 1×4 직렬 배열의 이론적 지향성과 합치되는 합리적 수치로, 수직(배열 방향) 분해능이 준수합니다.

사이드로브 −13.5 dB는 전형적인 소형 선형 배열 수준에서 무난하며, 0°에서 22 dB의 peak-to-null은 주엽 대비 억제가 충분함을 시사합니다.

3) EIRP 및 대역폭

EIRP(f) 측정: 칩 출력이 포화 상태일 때, 31.6 GHz에서 피크 EIRP 38.1 dBm을 달성했고, 3 dB EIRP 대역폭은 30–32.4 GHz(= 2.4 GHz)입니다. (Fig. 16b)

해석:

38.1 dBm(약 6.5 W EIRP)은 1×4 소형 모듈로서 실용적인 송신 등가 방사 전력을 보인다는 의미입니다.

2.4 GHz의 광대역 EIRP 평탄도는 칩 단계(×8 배수기+PA)와 안테나/급전 통합품질이 균형 있게 설계되었음을 뒷받침합니다.

4) 전기적 빔 스티어링(조향) 성능

E-plane 조향(32 GHz): VDAC 0.65 V(Vc≈3.71 V)에서 −20°, VDAC 2.5 V(Vc≈14.3 V)에서 +20° 조향을 달성해, 연속 조향 범위 ±20°를 입증했습니다. (Fig. 16c)

해석(설계와의 연결):

-앞서 VLTL-커플러 구조와 ×8 배수기를 결합해 기준 주파수에서의 요구 위상 제어량을 축소(식 (2) 효과)했고, 그 결과 단일 제어 전압으로도 4채널에 필요한 다위상을 안정적으로 제공할 수 있음을 실측이 확인합니다.

-II장에서 보였던 채널 간 삽입손실 불일치(최대 2.1 dB)가 사이드로브에 유의미한 악영향을 주지 않는다는 시뮬레이션 결과도 있었습니다(보정 불필요 수준).

5) 성능 맥락화(타 연구와 비교되는 포지셔닝)

본 논문은 별도의 표(Table 1)로 동향을 정리하며, 더 넓은 조향각을 보인 사례들도 있지만 채널별 개별 위상천이기 구성으로 제어 복잡도가 커지는 경향을 짚습니다. 제안 구조는 단일 VLTL의 누적 위상과 온칩 ×8 배수기를 활용해 필요 제어 범위를 대폭 축소(±20° 구현에 기준주파수에서 ≈21.5°급)했고, 이 접근을 ±60°까지 일반화할 때도 VLTL 단위 위상 제어 범위가 ≈54.5°면 충분하다는 점을 강조합니다.

해석:

대규모 배열로 확장할수록 제어 선로 수/보정 복잡도가 병목이 되는데, 이 구조는 “제어 단순성 ↔ 조향 성능”의 좋은 트레이드오프를 제시합니다.

특히 저주파 제어 → 고주파 방사라는 아키텍처는 바랙터 용량 변화에 따른 임피던스/손실 변동을 억제하고, 제조·집적 난이도를 낮춘다는 공학적 이점이 있습니다.