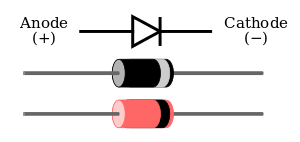

PN 접합 다이오드 구조

한쪽에 3가 불순물, 다른쪽에 5가 불순물 도핑

P형반도체와 N형반도체가 경계를 이루는 PN접합 형성

일반적으로 다이오드라고 한다.

P형 양극 단자를 애노드 N형 음극 단자를 캐소드라 한다.

화살표방향으로 전류가 흐르는 단방향 2단자 소자이다.

P형반도체에 정공이 더많아 외부 bias없이도 확산이동한다.

N형의 자유전자가 P형 정공으로 재결합 한다.

접합 부분에 억셉터 이온과 도너 이온이 만나 공핍층을 형성한다.

공핍층은 내부전계(Ein) 형성

전계가 확산이동을 막아 열평형상태(캐리어의 이동도 없고 전류도 안흐르는)를 유지한다.

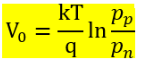

애노드와 캐소드의 접합 전위차는 si기준 0.7V Ge기준 0.3V이다.

공핍층은 접합 커패시터(Ct)를 형성하는데 공핍층이 커질수록 작아진다.

Vo(접합 전위차) = Vtln[(Na ND)/ni^2]

다이오드 바이어스

순방향 바이어스는 On

역방향 바이어스는 Off 로서

다이오드를 스위치화 할수 있다.

순방향 바이어스

애노드의 + 전압을 가하면 +정공들이 N형반도체쪽으로 밀리고

캐소드의 - 접압을 가하면 -자유전자들이 P형반도체 쪽으로 밀려 확산이동을 더 활발히 하며, 공핍층이 작아진다.

전위 장벽은 (Vo-Vf) 즉 실리콘 기준 0.7V- 외부바이어스전압 만큼 작아지게 된다.

소수캐리어에 의한 역방향 전류가 있지만 무시될수 있는 크기이다.

실제 다이오드는 스위치 앞에 미세한 순바이어스저항을 갖는 형태 이다.

역방향 바이어스

애노드의 -전압이 +정공을 끌어당기고, 캐소드의 + 전압이 -자유전자를 끌어당겨 공핍층이 커지게 된다.

전위 장벽 또한 Vo+Vf 즉 실리콘 기준 0.7V에서 외부바이어스 전압만큼 커지게 됨

확산이동을 막아 외부전압만큼 전위장벽이 커지면 순방향 전류가 0이된다. OFF

소수캐리어로 인해 역방향 전류 Io 가흐르게 되는데 접합부의 온도에 따라 좌우된다.

실제 다이오드는 미세한 역방향 전류가 흐른다.

공핍층의 크기에 따라 접합커패시터가 작아지며

순방향 바이어스는 접합커패시터보다 훨씬 큰 Cd(확산용량)이 형성된다.

다이오드 항복 상태

역바이어스 전압이 한계치를 넘으면 역방향 전류가 급격히 증가해 전력손실로 인해 손상을 일으킨다. 이를 항복현상이라 함

그래서 항복전압 이내로 역바이어스 전압을 가해야 한다.

- 에벌란치 항복 : 역바이어스 전압으로 소수캐리어를 가속시켜 역방향 전류로 인해 다이오드를 파괴시키는 현상

- 제너 항복 : 불순물을 강하게 도핑시켜 공핍층을 매우 좁게 만들어 낮은 전압에도 큰 전계가 생성되면 터널효과로 역방향 전류를 제한해 손상을 막는다.