1. What is Bus

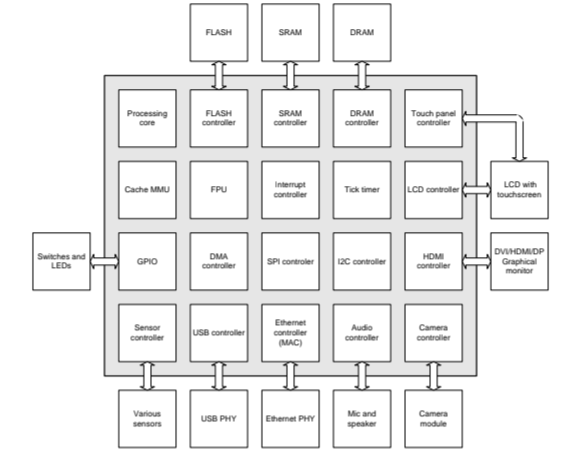

디지털 시스템에서는 여러 하드웨어 블록이 서로 데이터를 주고받아야 한다. 이 때 이들 사이의 공통 통신 경로 역할을 하는 것이 Bus이다.

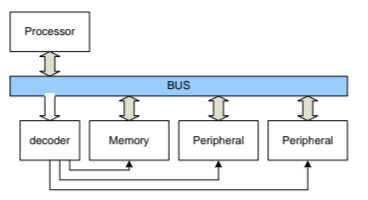

Bus는 여러 블록이 데이터를 주고받기 위해 사용하는 공통 통신 경로이며, 전통적으로는 공유 신호선 형태로 구현된다.

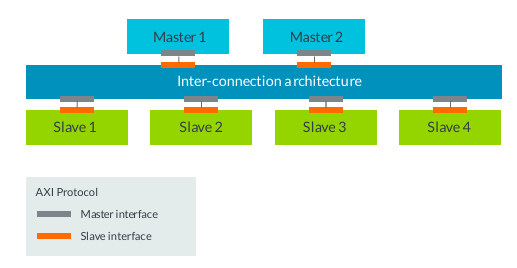

이 과정에서 전송을 시작하는 주체를 Master, 요청에 응답하는 주체를 Slave라고 한다. 예를 들어 어떤 장치가 특정 주소로 읽기 또는 쓰기 요청을 보내면 그 장치는 Master가 되고, 그 요청을 받아 데이터를 저장하거나 반환하는 장치는 Slave가 된다.

- Address Decoding

시스템에서는 보통 여러 개의 Slave가 연결되어 있으므로, 어떤 장치가 응답해야 하는지는 주소(Address)를 기준으로 결정된다. 즉, Address Decoder가 전달된 주소를 해석하여 해당 주소 공간을 담당하는 Slave를 선택하게 된다.

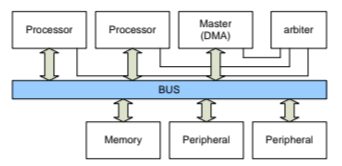

- Arbitration

또한, 시스템에서는 한 번에 여러 Master가 존재할 수 있다. 이 경우 어떤 Master의 요청을 먼저 처리할지를 정하는 과정이 필요한데, 이를 Arbitration이라고 한다. Arbiter는 여러 요청 가운데 하나를 선택하여 Bus 자원을 사용할 수 있도록 한다.

즉, Address Decoder는 어느 Slave를 선택할지 결정하고, Arbiter는 어느 Master의 요청을 먼저 처리할지 결정한다.

2. About the AXI protocol

현대 SoC(System on Chip) 설계에서 CPU와 주변 장치 간의 통신은 필수적이다. 모든 시스템은 CPU가 메모리에 데이터를 읽고 쓰듯이 주변 장치의 레지스터에 접근할 수 있어야 한다.

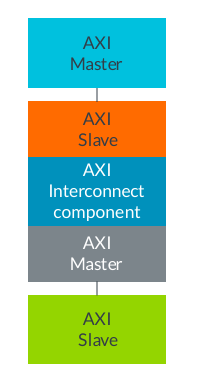

이때 가장 널리 사용되는 표준 인터페이스가 바로 AXI(Advanced eXtensible Interface) 프로토콜이다.

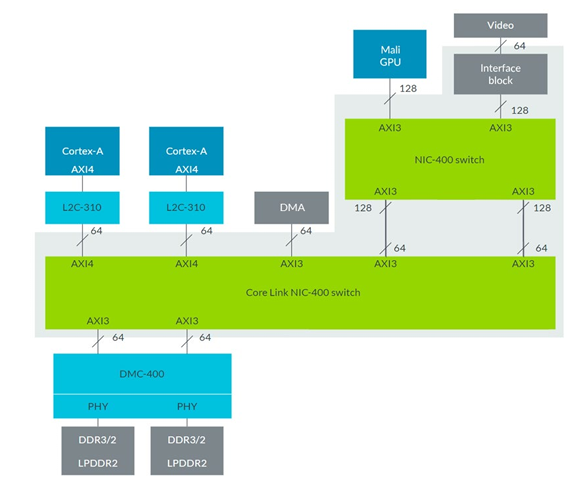

AXI는 단순한 “공유 버스”보다는, 보통 AXI Interconnect 위에서 여러 Master와 Slave 간 트래픽을 중재하며 동작하는 SoC 내부 표준 인터페이스로 이해하는 것이 더 정확하다.

AXI의 특징으로는 높은 대역폭, 낮은 지연 시간, 유연성 및 호환성, Burst 기반 연속 접근 등이 있다.

ARM社의 AMBA(Advanced Microcontroller Bus Architecture) 규격에는 서로 다른 용도에 최적화된 세 가지 AXI 계열 인터페이스가 존재한다.

- AXI4-Lite

-

간단한 레지스터 접근에 특화되어 있다.

-

CPU나 DMA 컨트롤러가 주변 장치의 제어 레지스터를 읽거나 쓸 때 주로 사용된다.

-

Burst 전송을 지원하지 않는 단순한 memory-mapped I/O 형태이며, 데이터량이 많지 않은 제어 경로에 적합하다.

- AXI4

-

대용량 데이터의 고속 전송에 특화되어 있다.

-

Burst 전송을 통해 주소 오버헤드를 줄이고, 연속적인 데이터 beat 전송으로 DRAM/메모리 컨트롤러가 선호하는 접근 패턴을 만들기 쉽다.

-

메모리 컨트롤러, DMA 엔진, 고속 I/O 인터페이스처럼 많은 양의 데이터를 빠르게 전송해야 하는 곳에 사용된다.

- AXI4-Stream

-

연속적인 데이터 스트림 전송에 특화되어 있다.

-

주소 개념이 없고, 데이터가 계속 흘러가는 파이프라인 구조이다.

-

영상/오디오/네트워크 패킷/신호처리(DSP)처럼 데이터 흐름 자체가 중요한 경로에 많이 사용된다.

정리: CPU 중심 시스템의 전형적인 구성으로는, CPU가 AXI4로 메모리 컨트롤러에 연결되어 DRAM에 고속으로 접근하고,

동시에 CPU는 AXI4-Lite로 여러 주변 장치의 제어 레지스터에 연결되어 설정을 변경하고 상태를 읽는다.

또한 주변 장치들은 AXI4-Stream으로 서로 연결되어 연속 데이터를 처리한다.

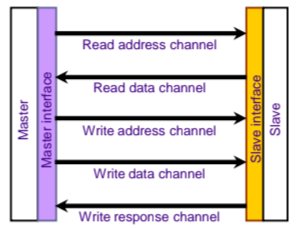

3. AXI Channel Structure

위 5채널(AW/W/B/AR/R) 구조는 AXI4/AXI4-Lite 같은 Memory-Mapped AXI 기준이며, AXI4-Stream은 주소 채널이 없는 별도의 스트리밍 인터페이스이다.

이러한 채널 분리는 주소, 데이터, 응답 경로를 서로 독립적으로 처리할 수 있게 하여, 단일 버스 구조보다 더 높은 처리량과 유연한 파이프라이닝을 가능하게 한다.

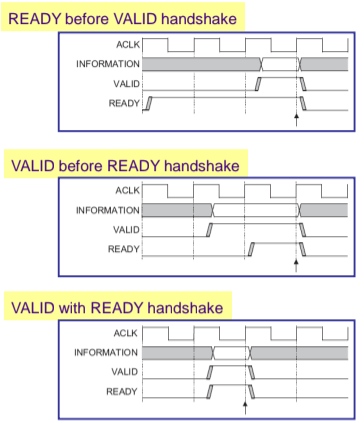

각 채널은 VALID/READY 핸드셰이크를 사용하여, 상대가 느릴 때 전송을 잠시 멈추는 backpressure를 자연스럽게 지원한다.

이때 송신 측이 READY를 기다렸다가 VALID를 올리면, 상대도 VALID를 기다리는 경우 deadlock이 발생할 수 있다.

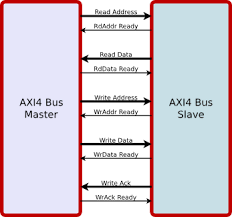

AXI는 총 5개의 채널로 Transaction을 처리한다.

- Write request, which has signal names beginning with AW

- Write data, which has signal names beginning with W

- Write response, which has signal names beginning with B

- Read request, which has signal names beginning with AR

- Read data, which has signal names beginning with R

- AXI의 5개 채널과 각 역할

-

Write and read request channels : 전송될 데이터의 주소 및 제어 정보를 전달하며, 이를 Request라고 부른다. 쓰기 요청과 읽기 요청을 위한 채널이 각각 별도로 존재한다.

-

Write data channel : Master에서 Slave로 실제 데이터를 전송한다. 데이터 폭은 최대 1024비트까지 가능하며, 8비트마다 유효한 바이트를 나타내는 Byte lane strobe 신호를 포함한다.

-

Write response channel : Slave가 Master에게 쓰기 작업이 정상적으로 완료되었음을 알린다. 이 응답은 개별 데이터 전송마다 발생하는 것이 아니라, 전체 write transaction이 끝난 뒤 한 번 전달된다.

-

Read data channel : Slave에서 Master로 데이터를 전송한다. 이 채널은 읽기 데이터와 함께 해당 transaction의 응답 정보도 함께 전달한다.

4. Summary

이번 글에서는 Bus의 기본 개념부터 AXI 프로토콜의 전체 구조, 그리고 AXI의 채널 구성까지 정리해보았다.

AXI는 주소, 데이터, 응답을 독립적인 채널로 분리함으로써 높은 성능과 유연성을 제공한다.

이후 글에서는 AXI4-Lite와 AXI4 인터페이스를 직접 설계하고, handshake와 read/write transaction이 실제 RTL에서 어떻게 구현되는지 살펴볼 예정이다.

AXI4 Protocol에 대해 이해하기 쉽게 설명해두셨네요!