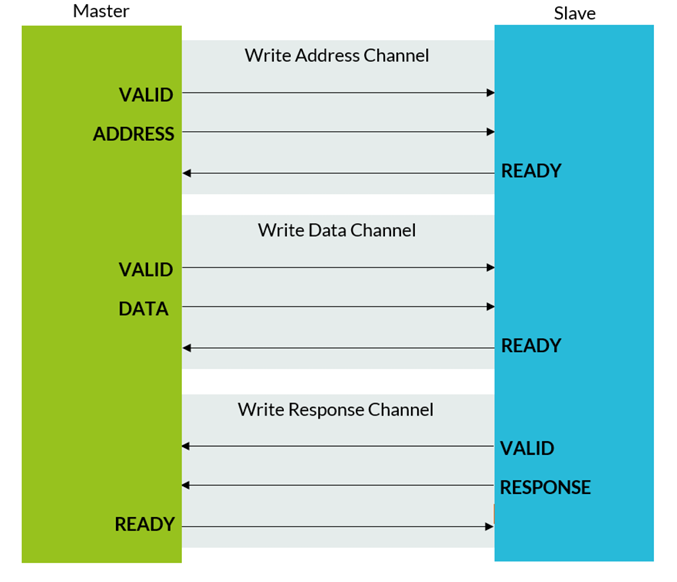

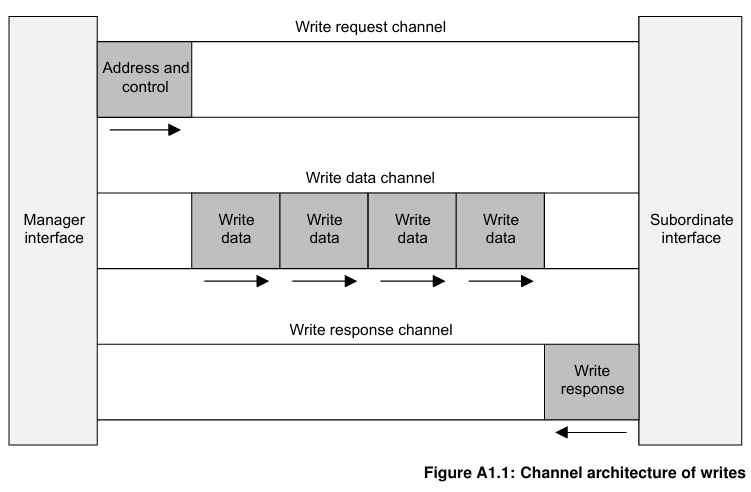

1. Write Transaction

AXI4-Lite에서 CPU(Master)가 주변 장치(Slave)의 레지스터에 데이터를 쓰는 과정은 세 개의 독립적인 채널을 통해 이루어진다.

각 채널에서 전송은VALID와READY가 동시에 1이 되는 클럭 사이클에 성립한다.

STAGE 1: Write Address Channel (AW)

- 이 채널을 통해 전달되는 정보는 쓰기 주소

AWADDR[31:0]이다. 핸드셰이크 신호로는AWVALID와AWREADY가 있다.

STAGE 2 : Write Data Channel (W)

- 이 채널을 통해 전달되는 정보는 쓰기 데이터

WDATA[31:0]와 바이트 선택 마스크WSTRB[3:0]이다. 핸드셰이크 신호로는WVALID와WREADY가 있다.

STAGE 3 : Write Response Channel (B)

- 이 채널을 통해 전달되는 정보는 응답 코드

BRESP[1:0]이다. 핸드셰이크 신호로는BVALID와BREADY가 있다.

여기서 중요한 점은 세 채널이 핸드셰이크 관점에서는 서로 독립적으로 동작한다는 것이다. 즉, Write Address Channel과 Write Data Channel은 서로 다른 시점에 핸드셰이크가 성립할 수 있다.

다만 Slave는 주소와 데이터를 모두 정상적으로 수신한 뒤에야 Write Response를 반환할 수 있으므로, 전체적인 처리 순서는 논리적으로 유지된다.

- Write Address Channel 상세 분석

-

AWADDR[31:0]- Write Address

[31:10] : Reserved(예약됨, 사용하지 않음). AXI-Lite는 최대 1024비트까지만 주소 공간을 사용하는 경우가 많다. 이보다 큰 주소 공간이 필요하면 AXI-Full을 사용한다.

[9:2] : 레지스터 인덱스(8비트). 이 비트들은 실제로 어느 레지스터를 선택할지를 결정한다.

[1:0] : 항상2'b00(바이트 오프셋). -

AWVALID- Address Valid -

AWREADY- Address Ready

- Write Data Channel 상세 분석

-

WDATA[31:0]- Write Data

실제로 레지스터에 쓸 32비트 데이터이다. Master가 이 값을 Slave에게 전달하면, Slave는 이 값을 레지스터에 저장한다. -

WSTRB[3:0]- Write Strobe

32비트의 데이터 중에서 어느 바이트를 실제로 쓸 것인지 선택할 수 있다.

예를 들어WSTRB = 4'b1111이면 4바이트 전체를 쓰고,WSTRB = 4'b0011이면 하위 2바이트만 갱신할 수 있다. -

WVALID- Data Valid -

WREADY- Data Ready

- Write Response Channel 상세 분석

-

BRESP[1:0]- Write Response Code

쓰기 동작의 결과를 나타내는 응답 코드이다. AXI4-Lite에서는 보통OKAY,SLVERR,DECERR를 사용한다. (OKAY, SLVERR, DECERR,EXOKAY) -

BVALID- Response Valid -

BREADY- Response Ready

즉, AXI4-Lite의 write transaction은 Address handshake, Data handshake, 그리고 Write Response handshake가 모두 완료되어야 최종적으로 끝난다.

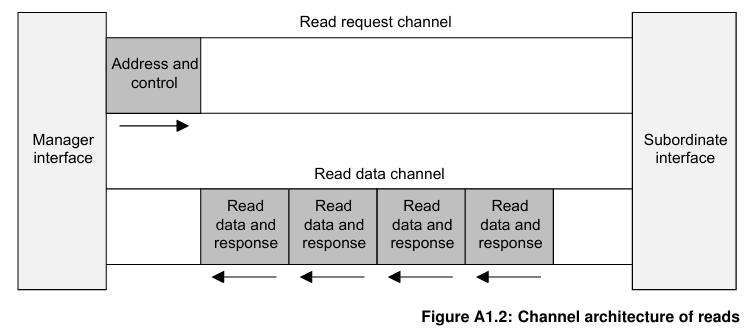

2. Read Transaction

Write transaction이 3개의 채널로 구성되는 반면, Read transaction은 2개의 채널만으로 처리된다.

STAGE 1 : Read Address Channel (AR)

- 이 채널의 신호로는

ARADDR[31:0],ARVALID,ARREADY가 있다.

STAGE 2 : Read Data Channel (R)

- 이 채널의 신호로는

RDATA[31:0],RRESP[1:0],RVALID,RREADY가 있다.

- Read Address Channel 상세 분석

-

ARADDR[31:0]- Read Address

읽기를 수행할 레지스터의 주소를 나타낸다.AWADDR와 마찬가지로 비트 필드 구조를 가진다. -

ARVALID- Address Valid -

ARREADY- Address Ready

- Read Data Channel 상세 분석

-

RDATA[31:0]- Read Data

Slave가 내부 레지스터에서 읽어 반환하는 32비트 데이터이다. Master는 이 값을 받아 CPU 레지스터나 메모리에 저장하게 된다. -

RRESP[1:0]- Read Response

읽기 동작의 결과를 나타낸다. 기본적으로 Write의 BRESP와 동일한 코드를 사용한다. -

RVALID- Read Valid -

RREADY- Read Ready

즉, AXI4-Lite의 read transaction은 Read Address handshake 이후, Slave가 Read Data와 Response를 반환하고 이에 대한 handshake가 완료되면 끝난다.

3. Register Type

AXI4-Lite Slave를 설계할 때, 주소로 선택되는 각 레지스터는 보통 접근 방식에 따라 R/W(Register) 와 RO(Register) 로 구분된다.

이 구분은 단순한 속성 차이가 아니라, write/read transaction이 실제 하드웨어에서 어떻게 처리되는지를 결정한다.

- R/W (Read/Write) Register

-

CPU가 읽고 쓸 수 있는 레지스터이다.

-

보통 Control, Config, Data register처럼 소프트웨어가 값을 설정해야 하는 항목들이 여기에 해당한다.

-

Write transaction이 성공하면 해당 주소의 내부 플립플롭 값이 갱신되고, Read transaction에서는 현재 저장된 값이 그대로 반환된다.

- RO (Read-Only) Register

-

CPU가 읽을 수만 있고 직접 쓸 수는 없는 레지스터이다.

-

보통 Status, Error, Version register처럼 하드웨어 상태를 소프트웨어에 알려 주기 위한 용도로 사용된다.

-

이 레지스터의 값은 내부 하드웨어 로직이 실시간으로 갱신하며, CPU가 write를 시도하더라도 무시하거나 에러 응답으로 처리할 수 있다.

결국 AXI4-Lite 인터페이스의 핵심은 주소 채널로 어떤 레지스터를 선택하고, 데이터 채널로 그 레지스터를 읽거나 쓰는 구조라고 볼 수 있다.

4. Summary

지금까지 AXI4-Lite의 Write / Read Transaction 구조와, 이를 통해 접근되는 레지스터의 종류(R/W, RO)를 살펴보았다.

AXI4-Lite는 burst transfer를 지원하지 않는 대신, 비교적 단순한 구조로 제어 레지스터 접근에 적합한 인터페이스이다.

따라서 주변 장치의 제어/상태 레지스터를 설계할 때 가장 널리 사용되는 방식 중 하나이다.

아래 저장소에는 이러한 구조를 바탕으로 작성한 AXI4-Lite 설계가 정리되어 있다.

- Github :

https://github.com/bjunverse26/AXI4_Lite