1. 프로젝트 소개

이번 프로젝트에서는 반도체 공정 편차를 이용해 고유한 응답을 생성하는 9T Dual-Mode SRAM PUF를 설계하였다.

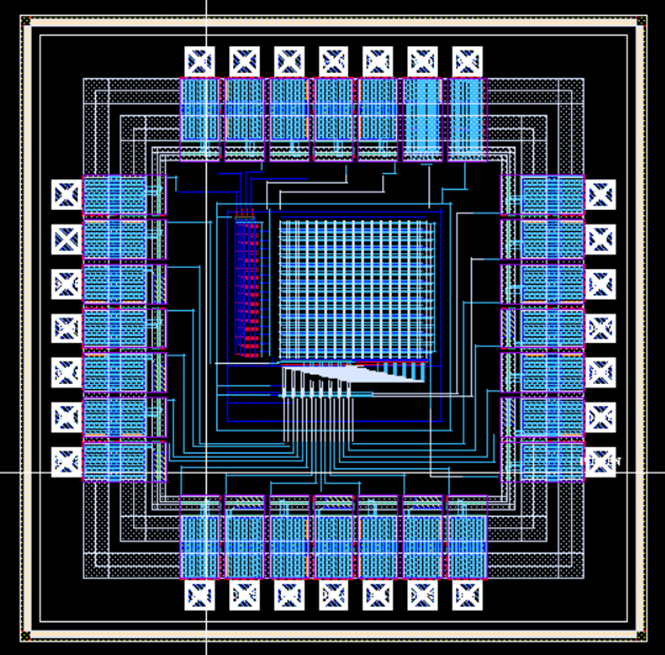

설계는 0.5um Analog CMOS 2P3M 5V 공정의 MPW를 기반으로 진행했으며, 회로 설계 및 시뮬레이션은 Cadence Virtuoso 환경에서 수행하였다.

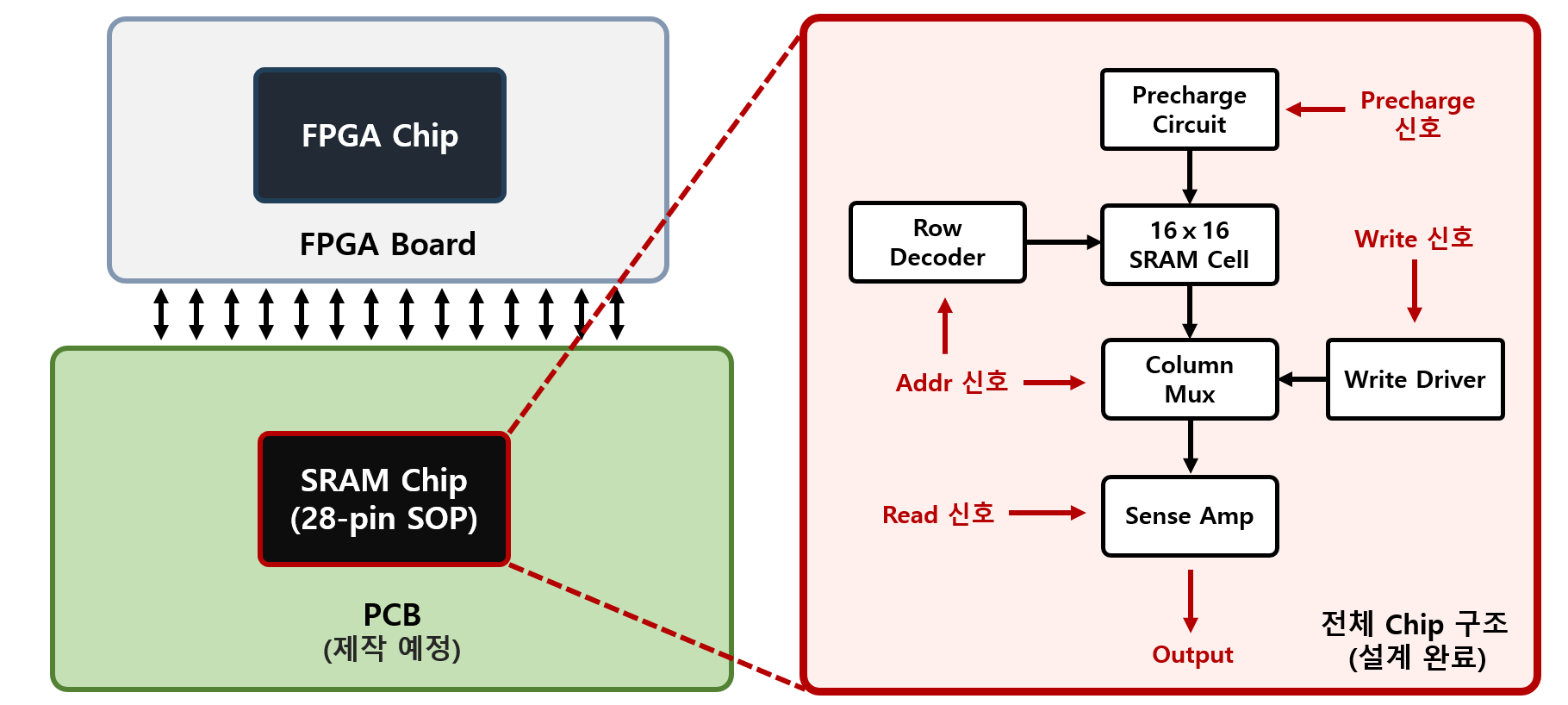

본 프로젝트에서는 단순히 SRAM PUF 셀만 설계한 것이 아니라, Precharge Circuit, Decoder, Write Driver, Sense Amplifier 등 SRAM 동작에 필요한 주변 회로를 포함한 통합적인 16×16 Array 구조를 설계하였다.

또한 회로 수준의 설계에 그치지 않고, 실제 구현 가능성을 고려하여 레이아웃 설계까지 진행하였다.

프로젝트의 핵심 목표는 기존 6T SRAM PUF에서 발생할 수 있는 bit flip 문제를 줄이고, 보다 안정적인 PUF 응답 특성을 갖는 새로운 셀 구조를 설계하는 것이었다.

이를 위해 먼저 8T 기반 구조를 통해 PUF 응답 안정성을 높이는 방향을 검토하였고, 최종적으로는 여기에 transistor 1개를 추가한 9T dual-mode 구조를 설계하여 SRAM mode와 PUF mode를 분리해 사용할 수 있도록 구현하였다.

PUF의 핵심 성능 지표인 Reliability, Randomness, Uniqueness 또한 고려하였으며, 0.5um(500 nm) 공정을 감안해 각각 97%, 40%, 45% 수준을 목표로 설정하였다.

마지막으로 설계한 16×16 chip은 레이아웃까지 완료한 뒤, 2026년 3월 7일 MPW 측에 GDS로 제출하였다.

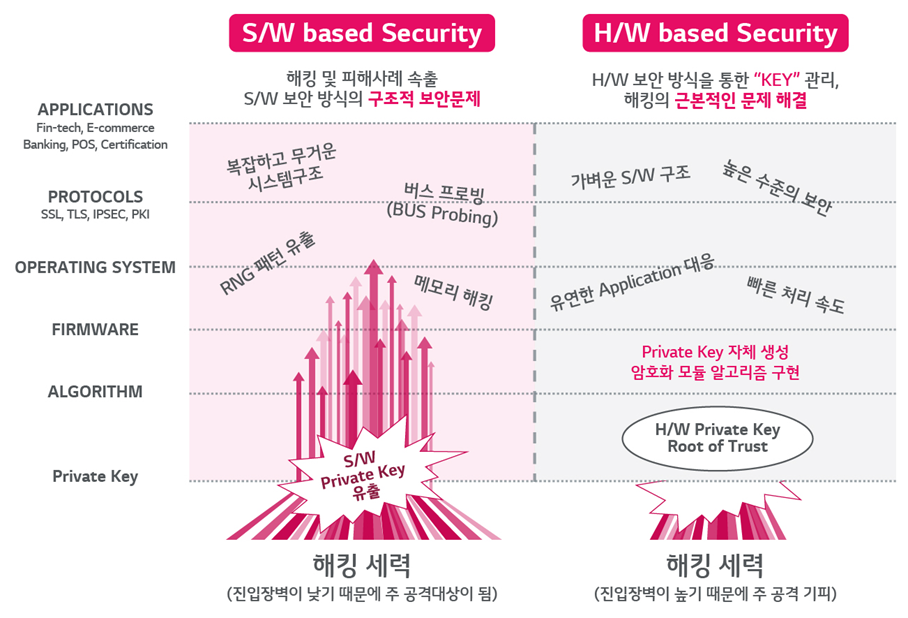

2. PUF (Physical Unclonable Function)

PUF는 반도체 제조 과정에서 자연스럽게 발생하는 공정 편차(process variation) 를 이용하여, 각 칩마다 고유한 응답을 생성하는 하드웨어 보안 기법이다.

동일한 구조의 회로를 동일한 공정으로 제작하더라도, 내부 소자의 미세한 차이로 인해 각 칩은 서로 다른 응답 특성을 가지게 된다. 이러한 특성 덕분에 PUF는 복제가 매우 어려운 하드웨어 기반 고유 식별자로 활용될 수 있다.

이러한 차이는 소자의 문턱전압(Vt), 이동도(mobility), 채널 길이 및 폭, 배선 및 소자 mismatch 등의 미세한 공정 편차에서 비롯된다. 동일한 회로를 동일한 공정으로 제작하더라도 이러한 물리적 특성이 완전히 같을 수는 없기 때문에, 각 칩은 물리적으로 복제하기 어려운 고유성을 갖게 된다.

즉, PUF는 별도의 비밀 키를 저장하지 않고도 칩 자체의 물리적 특성을 바탕으로 device authentication, key generation 등에 활용될 수 있다.

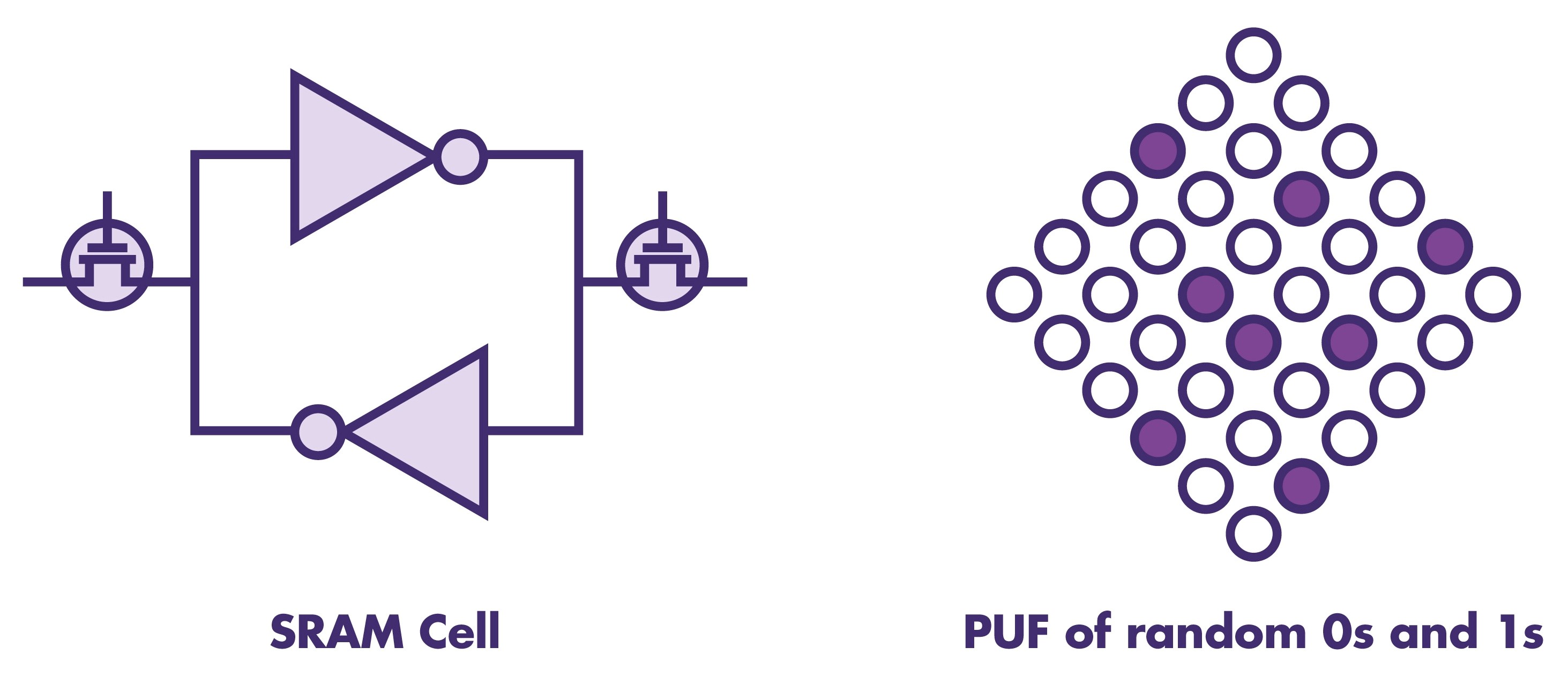

3. SRAM PUF

SRAM PUF는 SRAM 셀의 power-up 초기 상태를 이용하는 대표적인 PUF 구조이다.

SRAM 셀은 전원이 인가되는 순간 내부 소자의 미세한 공정 편차에 의해 특정한 한쪽 상태로 수렴하게 된다. 이때 형성되는 초기값은 셀마다 다르게 나타나며, 여러 셀의 초기값을 모으면 칩 고유의 bit pattern을 얻을 수 있다.

이러한 특성 덕분에 SRAM PUF는 별도의 복잡한 회로 없이도 구현할 수 있으며, 기존 SRAM 구조를 그대로 활용할 수 있다는 점에서 하드웨어 보안 분야에서 널리 연구되어 왔다.

다만 실제 SRAM PUF에서는 모든 셀이 항상 안정적인 초기값을 보장하지는 않으며, 이러한 안정성 문제는 곧 PUF의 reliability 저하와 직접적으로 연결된다.

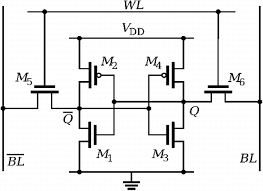

4. 6T SRAM Cell과 제안한 8T SRAM Cell

Conventional 6T SRAM cell은 두 개의 cross-coupled inverter와 두 개의 access transistor로 이루어진 가장 기본적인 SRAM 구조이다.

일반적인 메모리 용도로는 면적 효율이 높고 구현이 단순하다는 장점이 있지만, PUF 관점에서는 power-up 시 초기 상태가 얼마나 안정적으로 결정되는지가 매우 중요하다.

특히 셀 내부의 mismatch가 충분하지 않은 경우에는 전원 인가 시 특정 상태로 강하게 수렴하지 못하고, 외란이나 조건 변화에 따라 초기값이 달라질 수 있다. 이러한 현상은 반복 동작 시 bit flip으로 나타나며, 결국 PUF의 reliability를 저하시키는 원인이 된다.

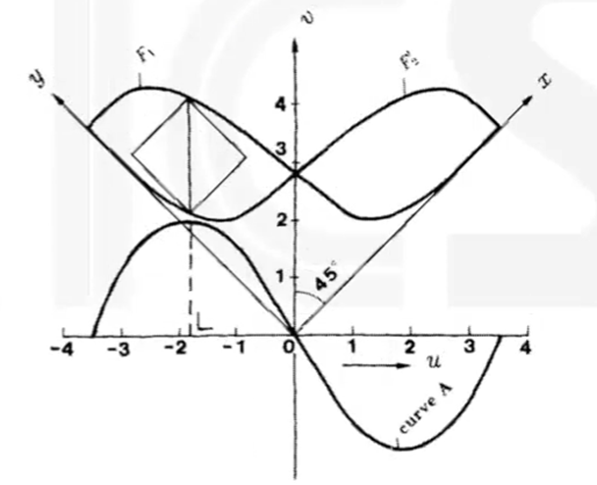

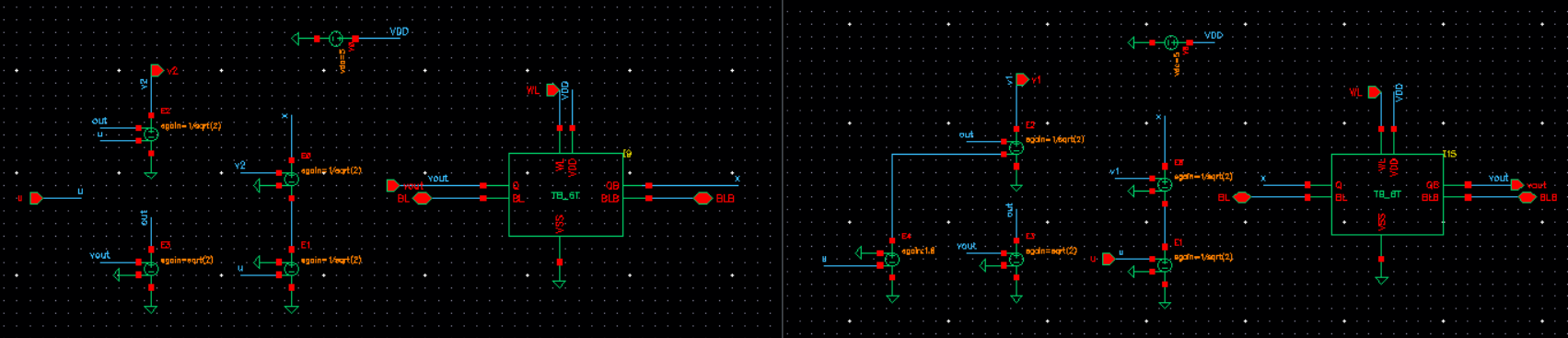

따라서 본 프로젝트에서는 기존 6T SRAM cell의 안정성을 정량적으로 확인하기 위해 SNM(Static Noise Margin) 을 기준으로 분석을 진행하였다.

이를 위해 Virtuoso 환경에서 graphical technique을 적용할 수 있도록 transformation 회로를 구성하였고, 이를 바탕으로 Abs. SNM과 Diff. SNM을 측정하였다.

구체적으로는 곡선을 45도 회전시킨 뒤, SNM 사각형의 대각선 길이를 측정하고 이를 √2로 나누는 방식으로 값을 계산하였다.

이 분석을 통해 단순히 셀이 동작하는지만 확인하는 것이 아니라, PUF 용도로 사용할 때 초기값의 결정성이 얼마나 확보되는지를 정량적으로 평가하고자 하였다.

5. 최종 9T Dual-Mode SRAM PUF

기존 6T 구조를 분석한 뒤, PUF 응답의 안정성을 높이기 위한 새로운 셀 구조를 설계하였다.

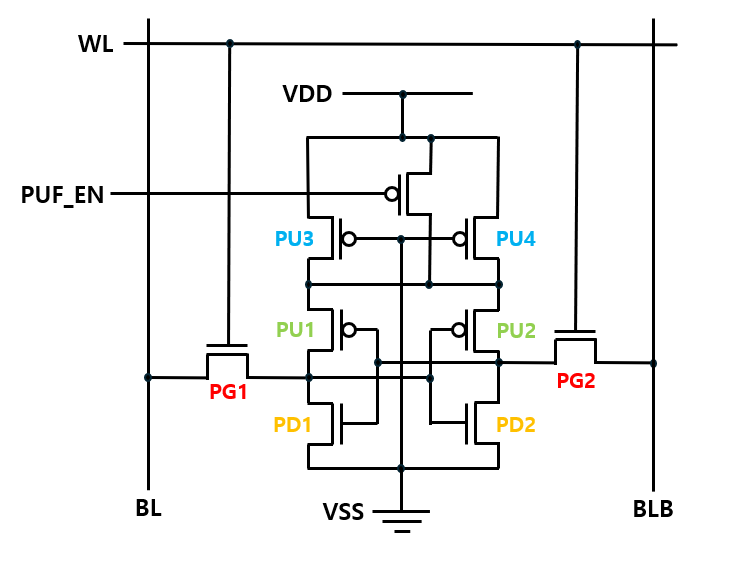

초기 아이디어는 기존 6T SRAM에 항상 ON 상태의 PMOS 2개를 추가한 8T 기반 구조였다.

이 구조에서는 추가된 PMOS의 on-resistance에 의해 내부 Q/QB 노드의 전압 강하가 유도되고, 그 결과 SNM의 상대적 불균형이 커지도록 설계하였다. 이를 통해 power-up 시 초기값이 보다 명확하게 결정되도록 유도하고자 하였다.

제안한 구조의 핵심은 Diff. SNM을 증가시켜 power-up 초기값의 결정성을 높이고, 동시에 Abs. SNM은 read 동작이 가능한 수준으로 유지하는 것이다.

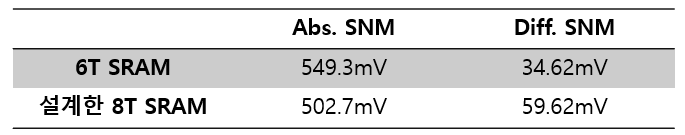

결과적으로, 0.5um 5V 공정 PDK에서 기존 6T SRAM의 Abs. SNM / Diff. SNM은 각각 549.3 mV / 34.62 mV였고, 제안한 8T SRAM에서는 502.7 mV / 59.62 mV로 측정되었다.

즉, Abs. SNM은 일부 감소했지만 Diff. SNM은 약 1.7배 향상되어 PUF 안정성 개선 가능성을 확인하였다.

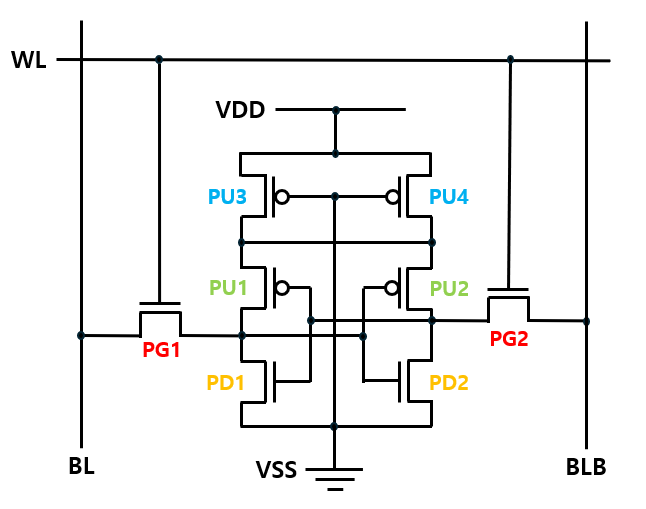

하지만 본 프로젝트의 최종 구현은 8T 기반 구조에 트랜지스터 1개를 추가한 9T SRAM cell이며, 이를 통해 SRAM mode와 PUF mode를 분리해 사용할 수 있는 dual-mode 구조를 구현하였다.

즉, PUF mode에서는 power-up 초기값을 활용하여 고유한 응답을 얻고, SRAM mode에서는 일반적인 메모리 셀처럼 데이터를 저장하고 읽는 방식으로 동작하도록 설계하였다.

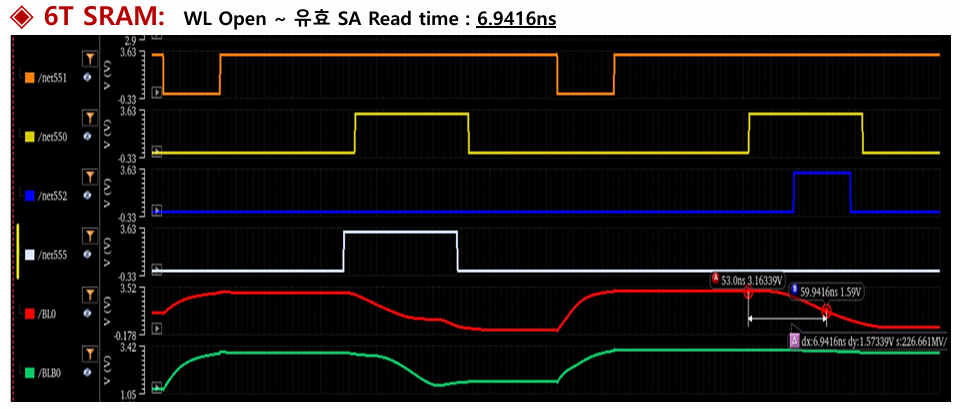

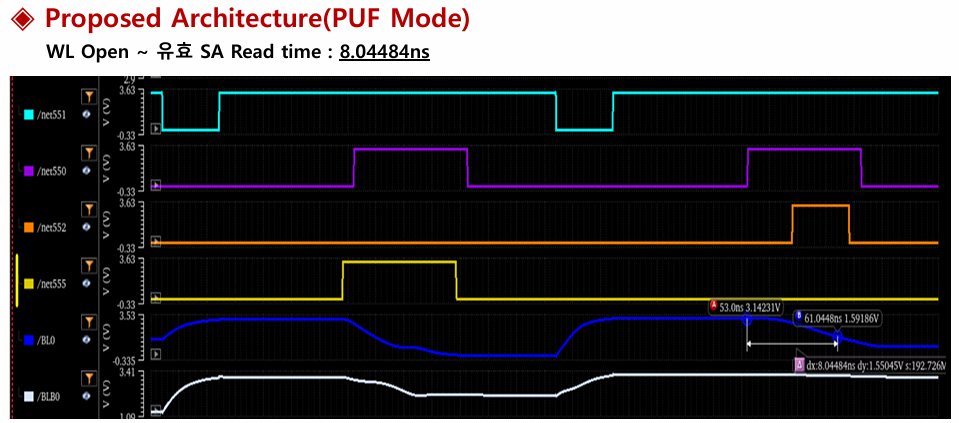

6. Mode에 따른 Latency 비교 및 개선

본 프로젝트에서 9T 구조로 확장한 중요한 이유 중 하나는 latency를 줄이기 위함이었다.

제안한 9T dual-mode SRAM PUF는 SRAM mode와 PUF mode를 구조적으로 구분하여 사용할 수 있도록 설계하였기 때문에, 동작 목적에 맞는 경로를 보다 명확하게 선택할 수 있다.

그 결과, 단순히 PUF 응답 안정성을 높이는 것을 넘어 전체 동작 latency 측면에서도 개선 가능성을 확보하였다.

7. 마무리

이번 프로젝트에서는 기존 6T SRAM PUF의 한계로 지적될 수 있는 bit flip 문제에 주목하여, 보다 안정적인 응답 특성을 갖는 8T SRAM PUF 구조를 먼저 고안하였다. 이후 이를 실제 활용 관점에서 확장하여, transistor 1개를 추가한 9T dual-mode SRAM PUF 구조를 최종 설계하였다.

또한 셀 단위 설계에 머무르지 않고, 16×16 Array와 주변 회로를 포함한 통합 매크로 설계, SNM 기반 안정성 분석, 레이아웃 구현, 그리고 MPW용 GDS 제출까지 수행하였다.

향후 칩이 수령되면 28-pin SOP 패키지를 장착할 수 있는 PCB를 설계하고, FPGA를 활용하여 실제 칩 구동 및 응답 수집을 진행할 예정이다. 이를 통해 randomness, uniqueness, reliability와 같은 PUF의 핵심 성능 지표뿐만 아니라 실제 latency 특성까지 추가적으로 검증하고자 한다.

결과적으로 본 프로젝트는 8T 기반 셀 구조 제안, 이를 확장한 9T dual-mode SRAM PUF 구현, 주변 회로를 포함한 매크로 설계, 안정성 분석, 레이아웃 구현, 그리고 MPW 제출까지 완료한 통합적인 SRAM PUF 설계 프로젝트라고 할 수 있다.