1. Logic Gate(논리 게이트) 구조

-

AND, OR, NOT, XOR 등은 디지털 회로에서 가장 기본적인 논리 게이트입니다.

-

이 게이트들이 수십~수억 단위로 모여서 CPU, GPU, NPU의 연산 장치를 구성합니다.

예시: AND 게이트

입력 A ──┬────

| AND ── 출력 Q (A AND B)

입력 B ──┘- 구성: 트랜지스터 몇 개로 만듭니다(CMOS 경우 NMOS, PMOS 조합).

2. ALU 등 내부 로직 구조

-

CPU, GPU, NPU 모두 내부에 "ALU(Arithmetic Logic Unit)"가 다수 존재합니다.

-

이 ALU 안에 논리 연산(AND, OR 등)을 수행하는 하드웨어가 있습니다.

-

NPU는 행렬 곱, 합성곱 등 딥러닝 연산 특화 회로가 추가되고, 역시 AND, OR, XOR, NOT 등이 기초로 들어갑니다.

3. 각 장치 내부의 논리 연산 회로

논리 게이트 → ALU → CPU/GPU/NPU 구조관계 흐름

[AND, OR, NOT, XOR ...] (기본 논리 게이트)

│

▼

[ALU] (산술논리유닛, 내부적으로 여러 논리회로 포함)

│

┌───────┼───────────────────────────────┐

│ │

▼ ▼

(다양한 조합) (수백~수천 개 배치)

[CPU] [GPU]

└─ 소수(몇 개)의 ALU └─ 수많은 ALU를 병렬로

+ 복잡한 제어부 + 간단한 제어부

│

│ (특화된 대규모 조합)

▼

[NPU]

└─ 수천~수만개 MAC(곱,누산) 유닛 + 행렬 곱, 합성곱 특화

+ Activation/Norm 등 연산기 하드웨어CPU

ALU ┐ ALU ┐

│ │

[Control Unit] [RegFile]

│

[CPU]GPU

[ALU] [ALU] [ALU] [ALU]

│ │ │ │

[Stream MultiProcessor] .... (수백 개)

│

[GPU]NPU (예시)

[MAC] [MAC] [MAC] [MAC]

[MAC] [MAC] [MAC] [MAC]

... (격자 형태 대규모 병렬)

│

[Special activation, Norm block]

│

[NPU]-

모든 칩의 물리적 최소단위는 논리게이트(AND, OR 등)

→ 결합해서 ALU 또는 MAC 등의 모듈로 커짐

→ 이것들이 각각 CPU/GP회/NPU 구조로 조립됨

-

구조의 차이점: 조립 방식, 배치/병렬화/특화 정도에서 큰 차이가 납니다

4. 각 내부 구조의 세부 흐름과 차이점

-

AND, OR, NOT 등 논리게이트는 반도체 내부 모든 연산 회로의 기본

-

논리게이트 → ALU/곱셈기/누산기 등 고차 회로 → 이들로 CPU/GPU/NPU 등 주요 칩 구조 형성

-

CPU: 다기능을 소수의 ALU로

-

GPU: ALU를 대량 병렬 배치로

-

NPU: 곱셈-누산(MAC) 등 AI 특화 유닛을 대규모 병렬로

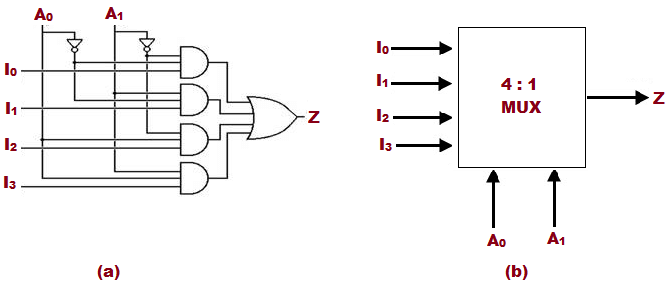

CPU의 ALU 내부

CPU의 ALU는 여러 논리 연산 회로(AND, OR, XOR 등)와 산술 연산 회로(가산기 등)로 구성되어 있습니다.

어떤 연산을 쓸지는 제어 신호(선택 신호)에 따라 정해집니다.

입력A ─────────┐

▼

┌─────────────────┐

│ AND 회로 │

입력B ────▶│ │───┐

└─────────────────┘ │

│

┌─────────────────┐ │

│ OR 회로 │ │

입력B ────▶│ │───┼─── MUX(멀티플렉서: 선택회로) ──▶ 연산 결과

└─────────────────┘ │

│

┌─────────────────┐ │

│ XOR 회로 │ │

입력B ────▶│ │───┘

└─────────────────┘- 제어 신호(명령어)에 따라 어떤 연산 결과를 출력할지 MUX가 선택합니다.

GPU 스트림 프로세서(SM) 내부

GPU는 넓은 범위의 병렬 연산에 최적화되어 있습니다.

한 번에 여러 데이터를 동시에 처리하기 위해 같은 구조의 작은 ALU(또는 연산 유닛)를 대량으로 배치합니다.

[ 입력 데이터들 ]

│

┌───────────┼─────────────┐

▼ ▼ ▼

[ALU] [ALU] [ALU] ...... (수백~수천 개)

│ │ │

[출력1] [출력2] [출력 n]-

각 작은 ALU 내부는 CPU ALU와 비슷하게 AND, OR, ADD, MUL 등의 회로로 이루어져 있습니다.

[MUL]

-

차이점은 동일한 명령을 여러 데이터에 병렬 적용(SIMD) 하는 데 특화되어 있다는 점입니다.

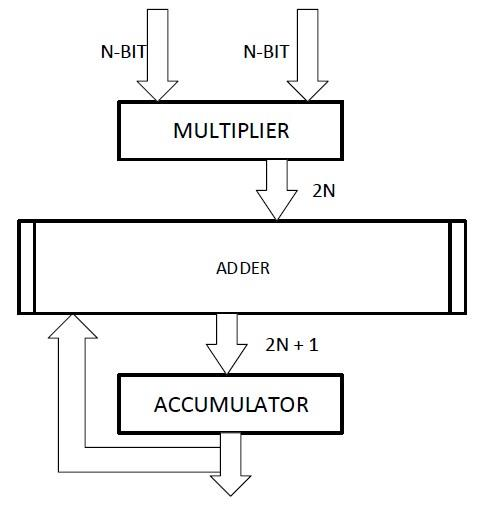

NPU(Neural Processing Unit) 행렬 곱 유닛 내부

NPU는 인공지능 연산에 특화되어 대규모 행렬 곱, 누산 연산을 빠르게 처리합니다.

[Input Vector/Matrix]

│

┌─────────▼─────────┐

│ 곱셈 회로 │ (Multipliers, AND는 곱의 기본 논리)

└─────────┬─────────┘

│

┌───────▼───────┐

│ 누산기(Adder) │ ← 값 누적 (가중합: MAC - Multiply-Accumulate)

└───────┬───────┘

│

┌─────────▼──────────┐

│ 활성화/정규화 회로 │ (ReLU, Sigmoid 등)

└────────────────────┘

│

[출력값]-

내부 곱샘, 더하기, 비선형 변환 등이 하드웨어로 대규모 병렬 배치됨.

-

주로 MAC(Multiply-Accumulate) 유닛이 '수천~수만 개' 격자처럼 배치되어 있음.

[MAC(Multiply-Accumulate) 유닛]