TSV는 실리콘 칩을 관통하는 수직 전극 구조로, 칩을 3D로 적층할 때 층과 층을 고속·고대역·저전력으로 연결하는 핵심 기술입니다. HBM 메모리, 3D NAND, 이미지센서 등 새로운 첨단 반도체에 빠질 수 없는 혁신적 기술로 자리잡고 있습니다.

TSV(Through Silicon Via)란?

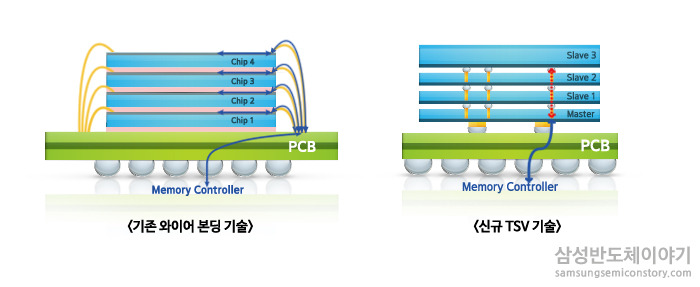

- TSV(Through Silicon Via)는 '실리콘 관통 전극'이라는 뜻으로, 반도체 칩을 3차원으로 적층(쌓는)할 때 칩 내부를 관통하는 미세 구멍을 만들어 그 안에 도체(금속, 보통 구리)를 채워 층과 층을 전기적으로 연결하는 첨단 기술입니다.

1. 등장 배경

-

기존의 2D 반도체는 칩을 옆으로만 넓게 배열해왔습니다.

-

점점 더 집적도를 높이고, 서로 다른 기능(메모리, 로직 등) 칩을 하나로 결합해야 하는 요구가 생기면서 3D 적층(Vertical integration) 방식이 필요해졌습니다.

-

3D로 쌓을 때, 각 칩(다이)마다 신호 및 전원을 빠르고 직접적으로 주고받게 만드는 기술이 바로 TSV입니다.

2. 구조와 제조 방법

-

구조

-

실리콘 웨이퍼(기판)에 미세한 구멍(via, 관통홀)을 만듭니다.

-

그 안을 절연체(산화막 등)로 절연하고, 중심에는 금속(주로 구리)을 채웁니다.

-

이 금속柱(기둥)이 칩의 윗면(또는 아랫면)에서 아래(또는 위)까지 전기적으로 연결해줍니다.

-

-

제조 단계 예시

-

실리콘 웨이퍼에 정밀한 초음파 드릴/식각으로 구멍을 뚫음

-

구멍 벽면을 절연(Dielectric)으로 코팅

-

중앙에 도체(구리 등) 증착

-

각 칩을 스택(적층)하여, TSV와 TSV가 맞닿도록 배열

-

외부 신호/전원 배선을 TSV로 연결

-

3. TSV의 장점

-

고속 신호 전송

- 칩-칩(다이-다이) 사이의 연결거리가 짧아서 신호 지연 및 손실이 매우 적음

-

소형화(고집적도) 실현

- 칩을 위로 올려 쌓으므로 면적 자체를 줄일 수 있음

-

전력 소모 감소

- 신호선이 짧고 저항이 작아, 같은 연산에도 사용 전력이 줄어듦

-

다기능 통합

- 메모리+로직, DRAM+SRAM, 센서+프로세서 등 다른 기능 칩을 하나로 결합 가능

4. 활용 분야

- HBM 같은 3D 스택 메모리

앞서 설명한 HBM(High Bandwidth Memory), 3D NAND 등에서 필수적인 역할

다수의 DRAM 다이를 적층과 TSV 통해 초고속 연결! - 고성능 이미지 센서

픽셀 어레이(센서부)와 신호 처리부(IC)를 적층해서 초고속 영상 처리에 활용 - 3D 시스템 온 칩(SoC), 고성능 FPGA, 모바일 AP 등

멀티 칩의 성능, 전력 모두 잡을 수 있는 구조에 필수

5. 도전 과제와 단점

-

제조 복잡성 증가

- 미세한 구멍 뚫기, 금속 증착, 적층 정렬 등 공정 난이도가 높음

-

불량/수율 문제

- 스트레스, 열, 정렬 오차 등으로 인해 결함이 생기기 쉬움

-

비용 상승

- 첨단 장비, 높은 기술 집약도 때문에 가격도 올라감