RAM은 하드웨어적으로 어떻게 구현할까?

RAM은 크게 두 분류로 나눌 수 있다. SRAM, DRAM

우리가 흔히 부르는 RAM은 D RAM을 지칭하는 것이다.

그럼 두 개의 차이는 무엇일까?

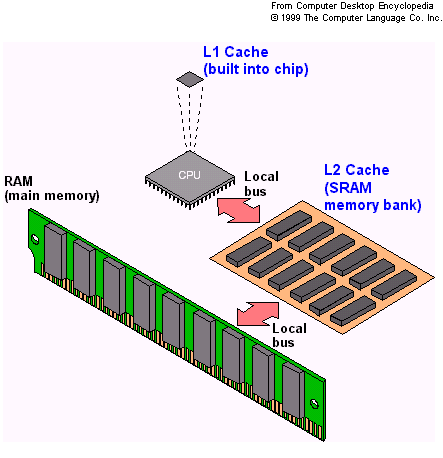

SRAM ( Static RAM ) 은 플립플롭소자로 구성되어 전원이 연결되어 있는 동안에는 내용을 계속 유지하며, Read/Write시간이 DRAM에 비해 무척 빠르다는 특성이 있다.

대신 한 비트 ( 한 cell )당 보통 4~6개의 트랜지스터로 이루어져 있어서 가격이 DRAM보다 비싸다.

빠른 처리 속도가 필요한 CPU 내부의 레지스터 혹은 cache 메모리로 사용된다.

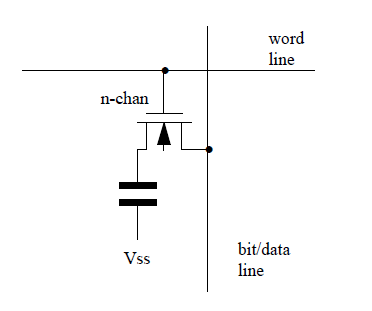

반면 DRAM ( dynamic RAM ) 한 셀당 1개의 트랜지스터와 커패시터로 구성되어 있다.

수 억개의 셀들이 집적된 칩들을 패키지 형식 ( 칩들을 여러개 병합하여 ) 으로

구성하며 Capacitor의 특성상 충방전이 필요하게 되므로 SRAM보다 데이터 접근속도는 느리지만 보다 저렴하고 더 많은 용량을 담아놓을 수 있다.

Capacitor가 방전되기 때문에 주기적으로 Refresh를 해주어야만 값을 유지할 수 있다.

우리가 흔히 말하는 주기억 장치라고 할 수 있다.

아래 사진은 DRAM의 사진이다.

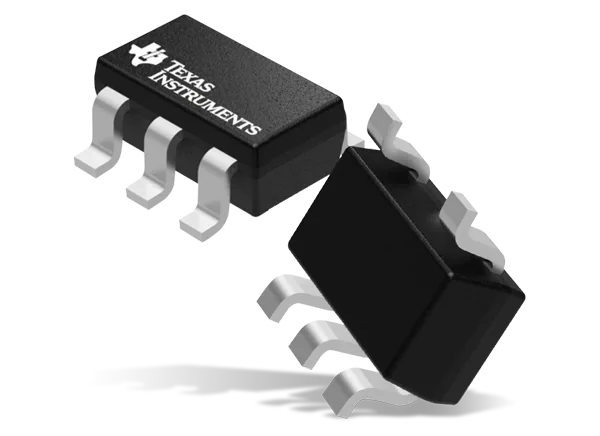

아래 사진은 S RAM의 사진이다.

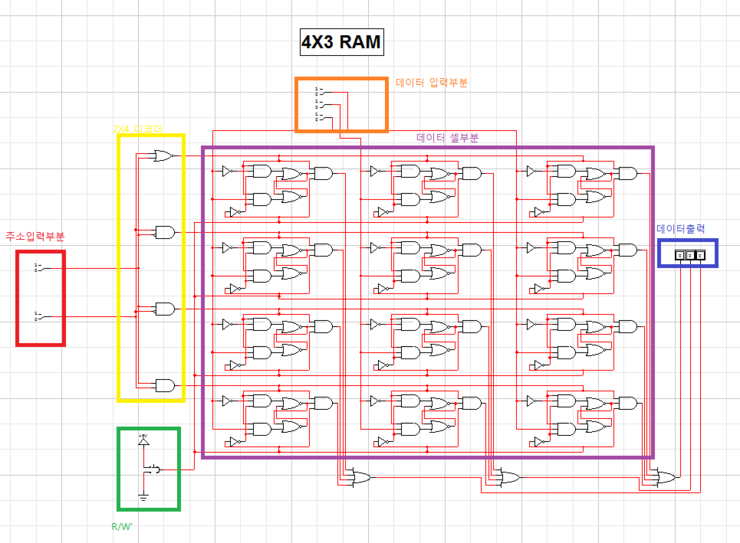

SRAM 내부 구조

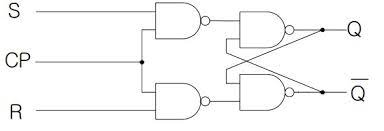

아래 사진은 S RAM의 내부 구조를 디지털 회로로 도식화 한 것이다. 여기서 확인할 수 있는 것은 뒤에서 서술할 플립플롭이다. 여러 개의 플립플롭들의 연결로 구성돼 있음을 확인할 수 있다.

그렇다면 플립플롭은 무엇인가?

< 플립플롭 소자 사진 >

플립플롭은 클럭 신호에 따라 입력을 받는 순차회로의 기본요소로 1비트의 정보를 보관 및 유지할 수 있는 기억소자다. 플립플롭의 종류는 다양하다. D, J-K, S-R 등등 여러 가지 상황에 따라 사용할 수 있다.

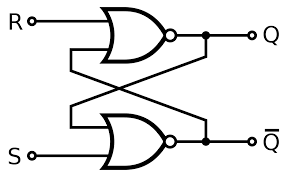

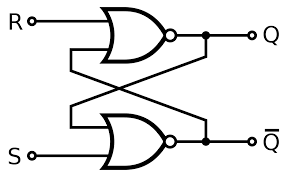

S-R 래치와 플립플롭은 유사하지만 클럭 펄스가 없냐 있냐의 차이이다. 플립플롭 이전의 개념이 래치이고 후에 발전된 개념이 플립플롭이다.

< 래치 > clock 펄스가 없다.

< F-F > clock 펄스가 있다. clock을 추가하게 된 이유는 출력 신호를 동기화시키기 위함인데 상승 신호에 제어하고 싶을 땐 positive trigger, 하강 신호로 원할 땐 negative trigger가 있는데 이 부분에 대해선 생략하겠다.

그렇다면 순차회로란 무엇인가? 순차회로는 조합회로에 현재의 상태를 비교하는 루프를 추가한 것이다.

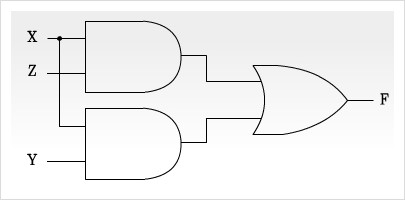

조합회로는 다음과 같이 입력이 들어왔을 때 출력값이 바로 결정된다. 아래의 예시를 보자.

X와 Z가 연결된 AND 게이트1, X와 Y가 연결된 AND 게이트2, 그리고 이 두 개의 게이트의 출력값을 OR 연산하면 F값의 출력을 결정할 수 있다. 즉, 위 회로는 X, Y, Z의 입력값이 들어오기만 하면 출력값 F가 결정된다.

그렇다면 플립플롭의 경우에는 어떨까? 좀 더 빠른 이해를 위해 플립플롭의 베이스 모델인 래치를 통해 알아보자

입력 신호 R과 S만 주어지면 위 회로는 출력이 결정될까? 아니다. R과 S 각 출력단의 상태가 크로스로 비교 입력단으로 들어가기 때문에 R과 S의 입력만으로는 부족하고 초기의 '상태값' ( === 현재의 상태값 ) 즉, 초기 Q값이 존재해야 한다.

예를 들어보자.

출력 Q가 전자 램프라고 치고 ON 버튼과 OFF 버튼이 있다고 치자. 플립플롭으로 동작시키기 위해서는 바로 ON과 OFF 버튼으로 제어를 하지 못하고 초기에 수동으로 램프를 ON 시켜 상태를 만들어준 뒤에 버튼으로 ON / OFF 제어를 할 수 있게 된다.

즉 현재 상태값이 필요한 것이 순차회로이고 플립플롭이다.

링크텍스트 -- 플립플롭의 종류와 진리표 및 출력 파형

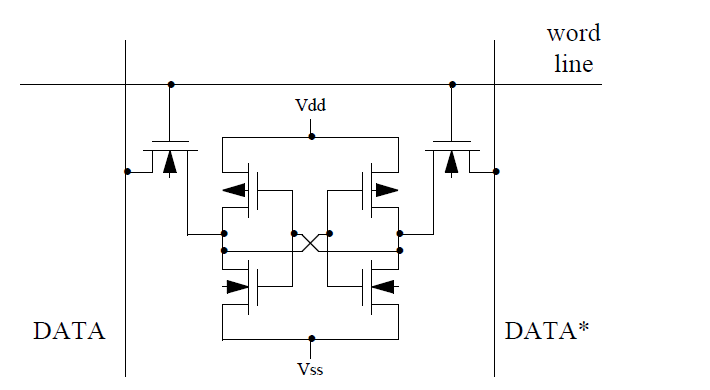

아래는 S RAM의 내부 구조 중 한 셀만을 추출한 이미지다. 보면 6개의 트랜지스터가 존재함을 알 수 있다.

아래는 D RAM의 내부 구조 중 한 셀만을 캡쳐한 이미지다. 한 개의 TR, 그리고 캐패시터로 구성됨을 확인할 수 있다.

다음은 컴퓨터 메인 보드의 주요 부품들을 표현한 것이다. cpu 내부에 cache 메모리가 내장되어 있고 RAM과 CPU를 연결하는 버스라인 사이에 cache용 메모리가 따로 적재되어서 CPU의 효율적인 데이터 처리를 지원하는 것을 확인할 수 있다.

이번 내용을 정리하면 S-RAM, 주기억장치라기 보단 CPU를 보좌하기 위해 존재하는 이 소자는 플립플롭으로 구성되어 있으며 CPU 내부의 레지스터, 혹은 캐쉬 메모리에 사용된다.

https://m.blog.naver.com/tb_elec_engineer/221034769694 --- 참고자료 1

https://nate9389.tistory.com/922 --- 참고자료 2