6.1 하드 디스크

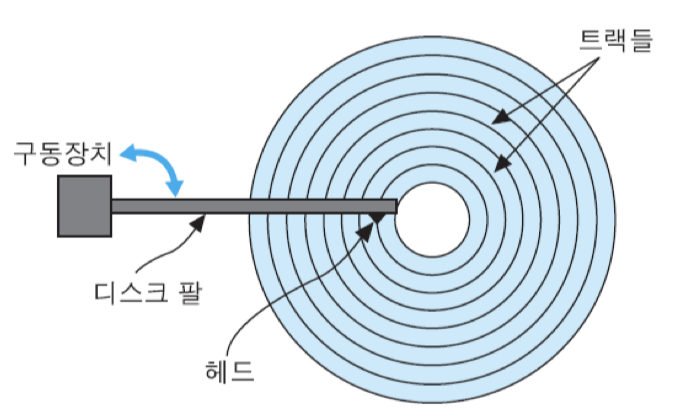

하드디스크 : 자화될 수 있는 물질로 코팅된 플라스틱이나 금속을 이용한 원형 평판으로 만들어지는데, 그 평판 위에 헤드라고 불리는 전도성 코일을 통하여 표면을 자화시킴으로써 데이터를 저장하게 됨. 헤드는 디스크에 저장된 데이터를 읽을 때도 사용됨.

디스크의 표면에는 그림에서 보는 바와 같이 여러 개의 동심원들이 존재하는데, 이 원들을 트랙이라고 부름. 데이터들은 트랙 위에 저장되며, 헤드가 그 트랙을 지나가는 동안에 데이터가 저장되거나 인출됨.

트랙 상에 데이터를 저장하는 동작을 디스크 쓰기라고 함. 쓰기 동작은 헤드의 코일에 전류가 흐르면 자기장이 발생되는 전기적 성질을 이용함. 즉, 전기적 신호가 헤드로 보내지면, 전류의 방향에 따라 서로 다른 형태의 자성 패턴이 표면에 기록됨. 여기서 2진수 '1'은 양전류로, '0'은 음전류로 각각 변환되어 헤드로 보내짐.

그와 같이 저장된 데이터를 디스크 표면으로부터 감지하여 인출하는 동작을 디스크 읽기라고 함. 읽기 동작은 자기장이 존재하는 곳에 코일이 지나가면 코일에 전류가 유기되는 전기적 성질을 이요함. 즉, 디스크 표면이 회전하는 동안에, 원하는 데이터가 저장되어 있는 트랙 부분이 헤드 밑을 통과하면, 기록될 때와 동일한 극성의 전류가 생성됨.

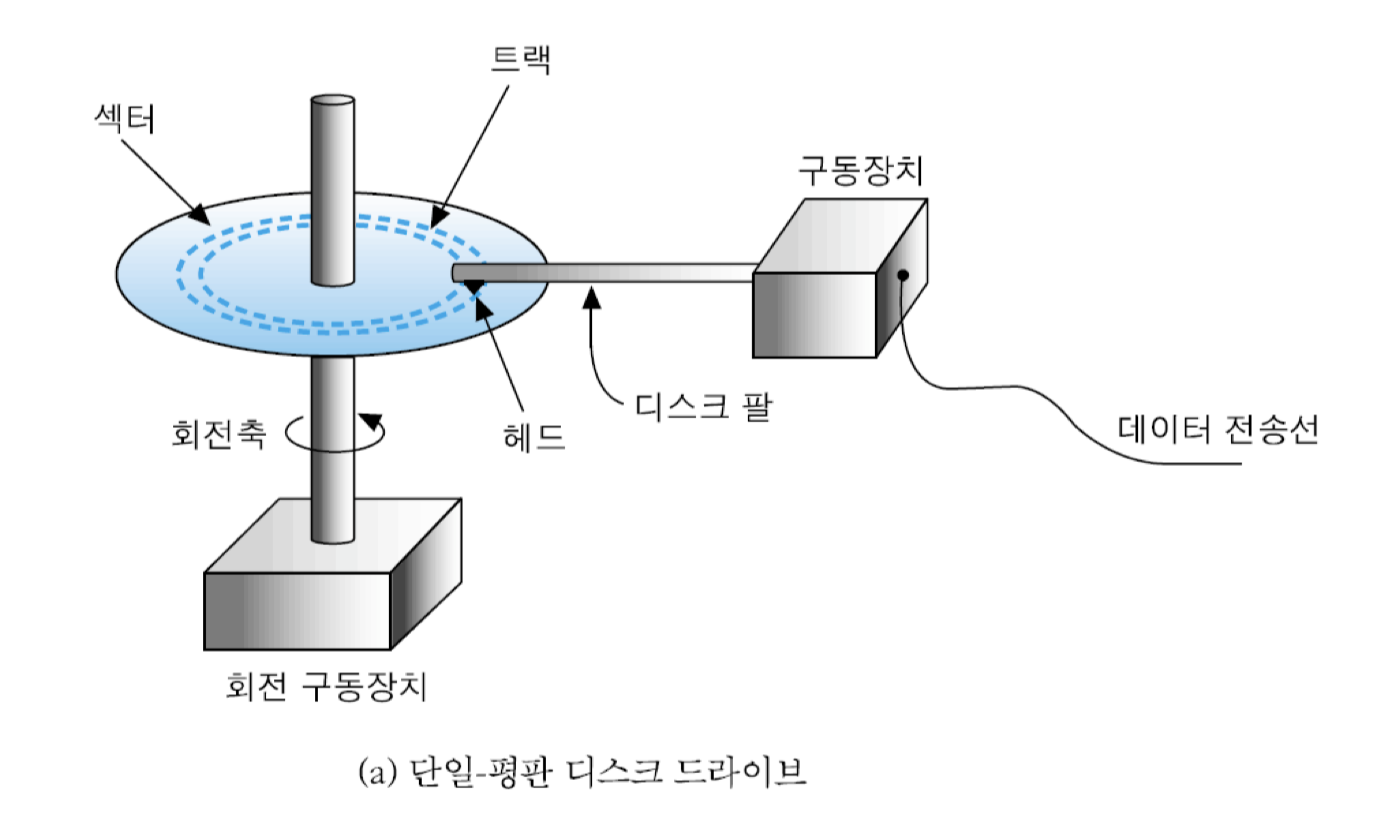

그림에서는 헤드가 디스크 팔이라고 부르는 직선 모양의 금속체 끝에 장착되어 있는 볼 수 있음. 디스크 표면상의 모든 트랙들에 대한 액세스는 헤드를 통해서만 이루어질 수 있음. 따라서 디스크 팔을 움직여 헤드를 이동시킬 수 있어야 하며, 이 동작은 디스크 팔의 끝 부분에 설치된 구동장치에 의해 이루어짐.

6.1.1 디스크의 구조

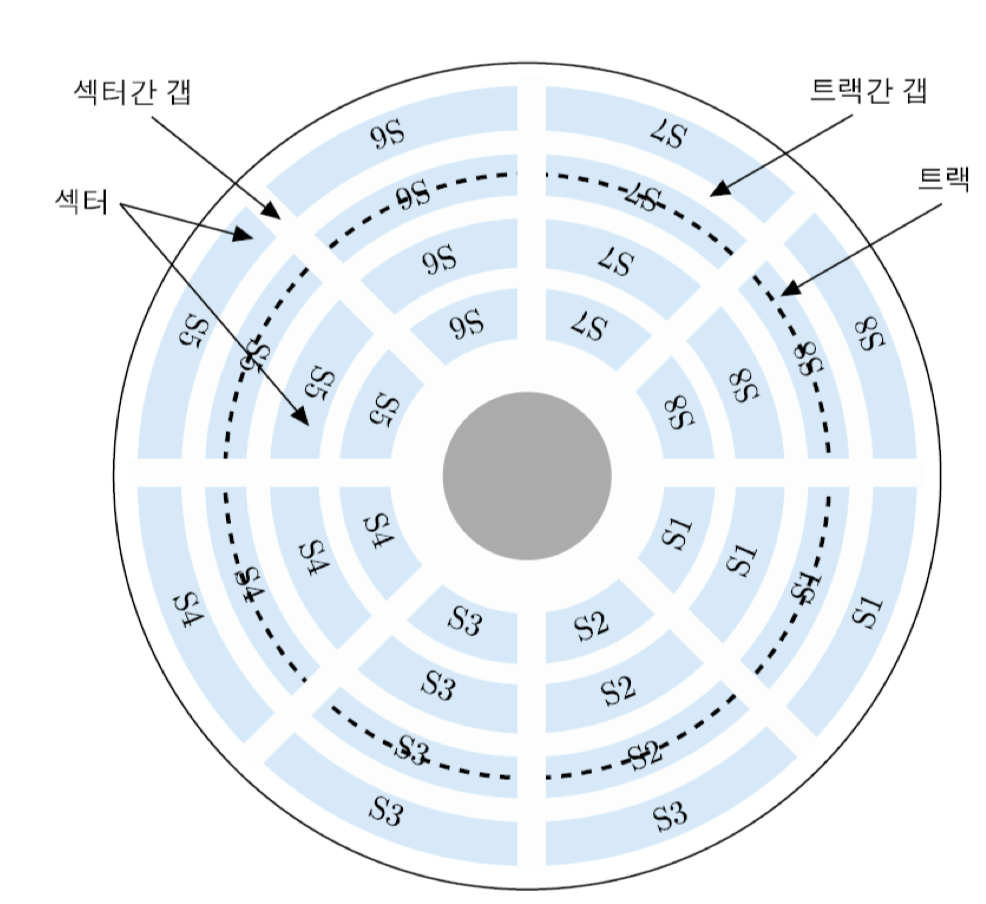

섹터 : 트랙의 분할된 각 부분으로서, 데이터 전송 단위인 한 블록을 저장

섹터간 갭 : 섹터들 간을 구분하기 위한 빈 공간

트랙간 갭 : 트랙들 간을 구분하기 위한 빈 공간

그림은 적은 수의 트랙들과 섹터들만 표시한 디스크 표면을 이용하여 그 세부적인 구조를 보여주고 있음. 이 그림에서는 트랙의 수가 네 개이고, 각 트랙은 8개의 섹터들로 나누어져 있음.

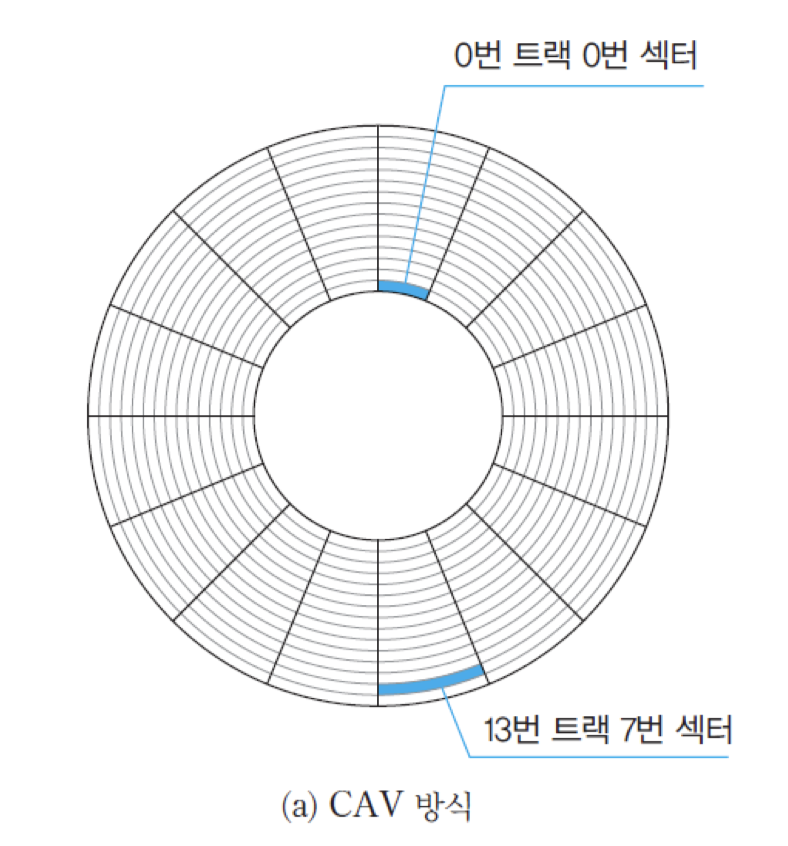

등각속도(CAV) : 중심부에 가까운 트랙을 액세스하든 멀리 위치한 트랙을 액세스하든 일정한 속도로 회전시키는 방식

그림 (a)는 CAV 방식을 사용하는 디스크 표면의 배치도를 보여주고 있음. 동심원 형태의 트랙은 파이 모양의 섹터들로 분할됨. 각 섹터에 저장된 데이터 블록은 그림에 표시된 예와 같이 트랙 번호와 섹터 번호에 의해 주소지정 될 수 있음. 헤드를 현재의 위치에서 특정 주소로 이동시키기 위해서는 먼저 특정 트랙으로 헤드를 이동시킨 다음에, 원하는 섹터가 회전하여 헤드 아래에 도달할 때까지 잠시 기다리면 됨.

CAV 방식을 사용하면 회전 속도가 일정하기 때문에 구동장치가 간단하지만, 길이가 더 긴 바깥쪽 트랙에 저장될 수 있는 데이터 비트 수를 길이가 더 짧은 중심부의 트랙에 저장될 수 있는 데이터 비트 수와 동일하게 해야 함. 이를 위해서는 바깥쪽 트랙의 저장 밀도를 낮추어야 하므로, 저장 공간이 낭비된다는 것이 CAV 방식의 단점임.

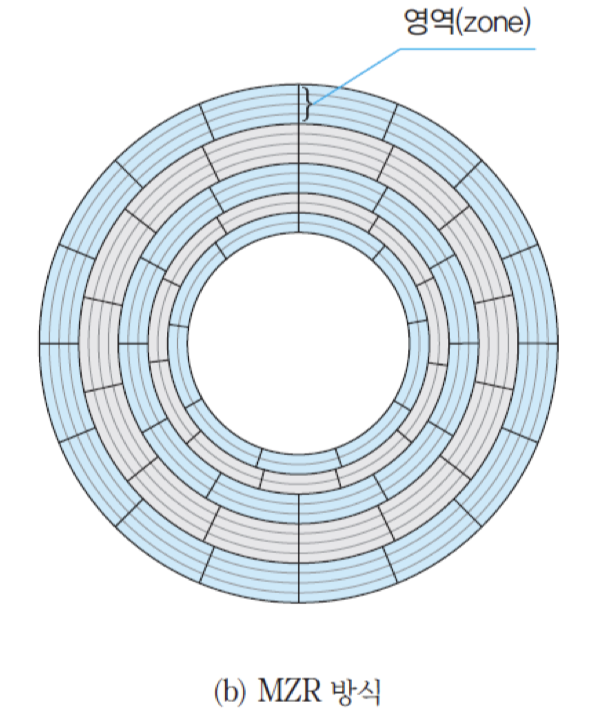

다중 영역 기록(MZR) : 디스크 상의 트랙들을 몇 개의 영역들로 나눔으로써 저장 용량을 늘리는 방식

이 방식에서는 디스크 표면이 그림 (b)와 같이 여러 개의 동심원 영역들로 나누어지며, 같은 영역에 속한 트랙들에는 같은 수의 비트들을 저장하도록 밀도가 조정됨. 그리고 디스크의 모든 트랙들에서 저장 밀도가 거의 같아지도록 함. 결과적으로, 바깥쪽 영역의 트랙들은 길이가 더 길기 때문에 중심부 근처 영역의 트랙들보다 더 많은 비트들을 저장할 수 있어서, 더 많은 수의 섹터들로 나누어질 수 있음.

그림 (b)는 MZR 디스크 표면의 간략화된 예를 보여주고 있는데, 15개의 트랙들이 5개의 영역들로 조직된 경우임. 가장 안쪽에 위치한 두 개의 영역은 각각 두 개씩의 트랙들을 포함하고 있으며, 각 트랙은 9개 혹은 11개의 섹터들로 나누어져 있음. 그 다음 영역은 세 개 트랙들로 이루어져 있으며 각각의 섹터는 12개씩, 그리고 가장 바깥쪽의 두 영역들은 네 트랙씩 포함하고 각 트랙은 14개 혹은 16개의 섹터들로 나누어져 있음. 이 방식을 사용하는 실제 디스크에서는 일반적으로 16개 정도로 분할되고, 각 영역에 포함되는 트랙들의 수는 수천 개씩임.

MZR 방식을 이용하면 제어 회로가 약간 더 복잡해지지만 전체 저장 용량을 증가시킬 수 있음. 그리고 디스크 헤드가 한 영역에서 다른 영역으로 이동할 때 각 비트가 차지하는 트랙 상의 길이가 미세하지만 약간씩 다르기 때문에, 읽기와 쓰기에 걸리는 시간도 차이가 나게 됨.

헤드를 통하여 데이터를 쓰거나 읽을 때 각 트랙 상에서 섹터들을 구분하는 방법이 필요함. 즉, 트랙에는 시작점이 있어야 하고, 각 섹터의 시작과 끝을 구분하는 방법이 있어야 함. 그러한 정보들을 포함하는 제어 데이터는 디스크 형식화 작업 과정에서 각 트랙 및 섹터의 특정 위치에 기록됨.

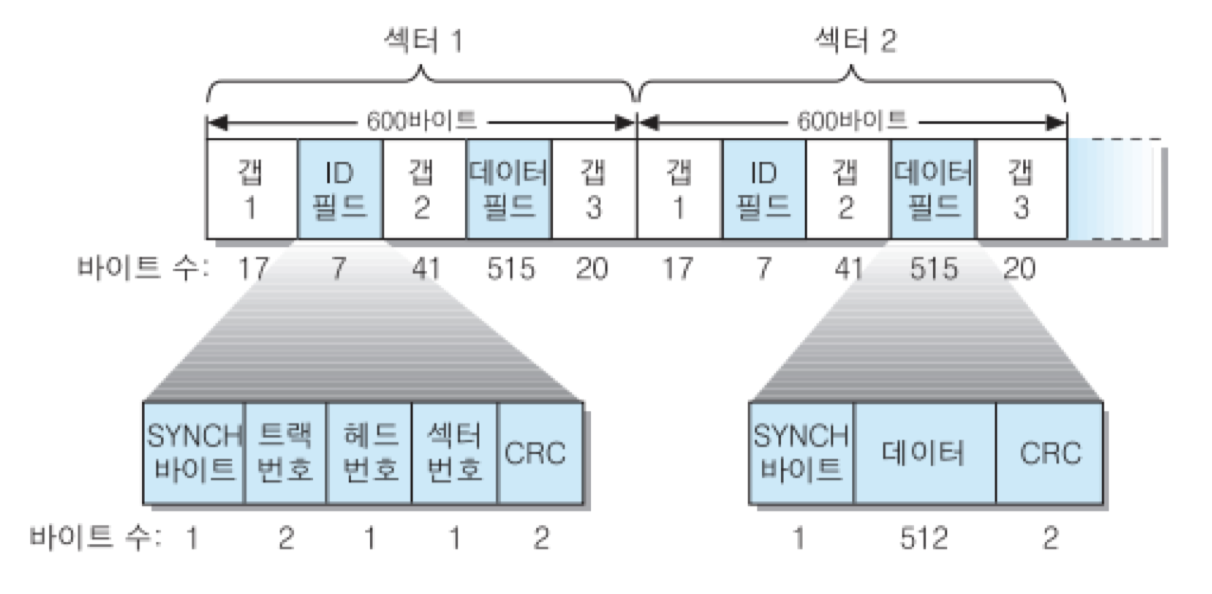

그림은 디스크의 한 트랙을 형식화한 예를 보여주고 있음. 이 디스크에서 각 트랙은 길이가 600바이트인 섹터들로 구성되어 있음. 각 섹터에서 512바이트의 데이터와 제어 정보가 저장되며, 나머지 공간에는 섹터간 갭들 외에도 각 섹터를 식별하기 위한 ID 필드가 포함됨. 즉, ID 필드에는 특정 섹터를 구분하는 데 필요한 식별자 또는 주소가 저장됨.

그림은 ID 필드의 세부 내용도 보여주고 있는데, 먼저 SYNCH 바이트는 필드의 시작점을 구별하는 특수한 비트 패턴임. 트랙 번호는 같은 표면상의 트랙들을 구분하는 데 사용됨. 그리고 디스크의 표면당 헤드가 한 개씩 있으므로, 헤드 번호로 표면을 구분함. 섹터 번호는 각 트랙의 섹터들을 구분해줌. ID 필드와 데이터 필드는 각각 오류 검출을 위한 CRC 코드를 포함하고 있음. 그림에서 각 필드의 밑에 표시된 숫자는 필드의 길이를 바이트 수로 나타낸 것임.

디스크 드라이브 : 디스크 평판, 디스크 팔, 회전 구동장치 및 데이터 전송회로를 포함한 패키지

디스크 드라이브는 그림 (a)와 같이 디스크 외에도 헤드가 부착된 디스크 팔, 디스크 회전 구동장치, 그리고 데이터 전송에 필요한 전자회로 등을 포함하고 있음.

대부분의 디스크들은 평판의 양쪽 면이 모두 자화 물질로 코팅되어 있으며, 이것을 양면 디스크라고 함. 양면 디스크 드라이브에는 각 디스크 표면당 한 개씩의 디스크 팔과 헤드가 존재함. 용량이 적고 가격이 저렴한 디스크 드라이브는 단면 디스크를 사용함.

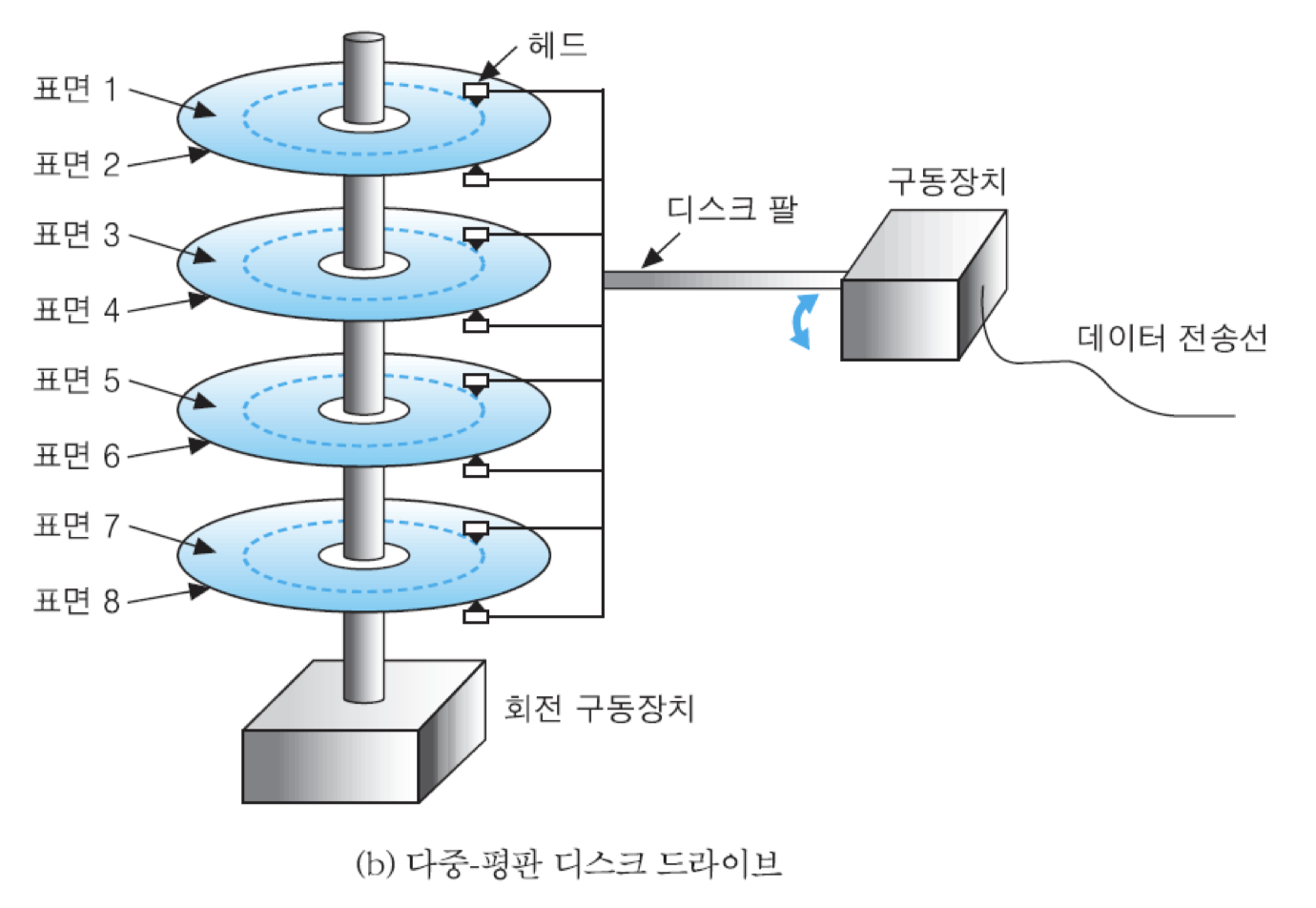

대용량 디스크 드라이브는 그림 (b)에서 보는 바와 같이 여러 개의 평판들이 하나의 회전축에 적절한 간격을 두고 고정되어 있음. 그리고 각 표면마다 한 개씩의 디스크 팔과 헤드가 장착되어 있음. 물론 각 표면의 트랙 수와 데이터 밀도 및 형식은 모두 동일함. 이러한 드라이브에서 디스크 팔들을 동시에 같이 움직이도록 한다면, 여러 표면의 같은 위치에 저장된 데이터들을 동시에 액세스 할 수 있을 것임. 이와 같이 서로 다른 표면에 있지만 같은 반경에 위치하고 있어서 디스크 팔을 움직이지 않고도 동시에 액세스할 수 있는 트랙들의 집합을 실린더라고 함. 예를 들어, 그림 (b)와 같이 네 개의 양면 디스크 평판들이 장착된 디스크 드라이브에서는 한 실린더가 각 표면의 동일한 트랙 번호를 가진 8개의 트랙들로 구성됨. 디스크 드라이브에는 최대 20개까지의 디스크 평판들이 포함되기도 함. 일반적으로 디스크 액세스를 위하여 발생되는 주소는 디스크 드라이브 번호, 실린더 번호, 헤드 번호 및 섹터 번호로 이루어짐.

윈체스터 디스크 : 디스크 표면과 헤드가 가까워질수록 불순물이나 충돌 등에 의한 오류 발생 위험이 더 커지는데, 이러한 문제점을 해결하고 밀도를 더욱 높이기 위하여 개발됨.

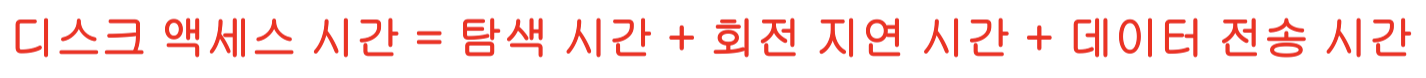

6.1.2 디스크 액세스 시간

단일-헤드 디스크시스템에서 어떤 데이터 블록을 읽거나 쓰는 과정

① 헤드를 해당 트랙으로 이동시킴

② 원하는 데이터가 저장된 섹터가 헤드 아래로 회전되어 올 때까지 기다림

③ 데이터를 전송

디스크 액세스 시간 : 위의 과정에 걸리는 전체 시간

탐색 시간 : ①번에 걸리는 시간

회전 지연시간 : ②번에 걸리는 시간

데이터 전송 시간 : ③번에 걸리는 시간 및 디스크 제어기에서 소요되는 전자회로의 동작 시간

탐색 시간 : 헤드를 액세스할 트랙으로 이동시키는 데 걸리는 시간

회전 지연시간 : 헤드가 해당 트랙에 도달한 순간부터 원하는 섹터가 회전하여 헤드 아래에 도달할 때까지의 시간

데이터 전송 시간 : 헤드를 통하여 섹터의 데이터 비트들을 전송하는 데 걸리는 시간

6.2 RAID

RAID : 다수의 작은 디스크들을 배열로 연결하여 용량을 늘리고 신뢰성도 향상시킨 대용량 디스크시스템

6.2.1 RAID 출현의 배경

하나의 대형 디스크를 사용하는 것보다는 크기가 작은 여러 개의 디스크들을 서로 연결하여 하나의 큰 용량을 가진 디스크 유니트로 사용하는 것이 보다 저렴한 가격으로 더 큰 용량을 가진 디스크 서브시스템을 구성할 수 있는 방법이 됨.

추가적인 장점

• 데이터 분산 저장에 의한 동시 액세스 가능

• 병렬 데이터 채널에 의한 데이터 전송 속도 향상

디스크 인터리빙 : 데이터 블록들을 여러 개의 디스크들에 분산 저장하는 기술

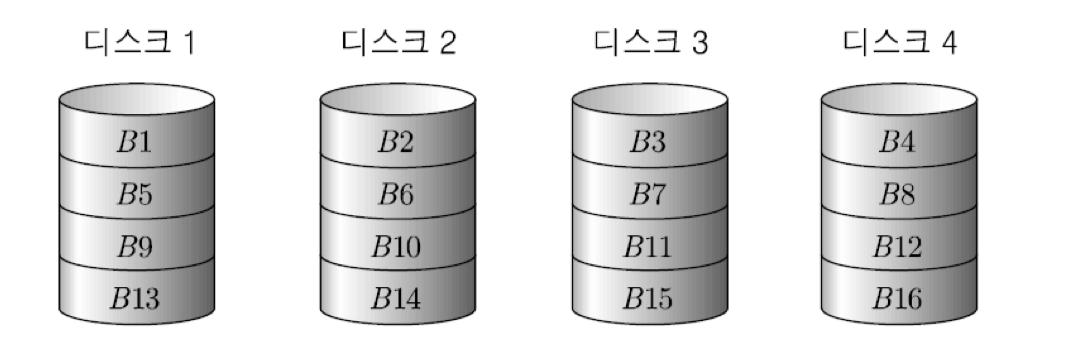

그림에서 보는 바와 같이, 데이터 블록 B1은 첫 번째 디스크에 저장하고, B2, B3 및 B4는 순서대로 다음 디스크들에 저장함. 그리고 블록 수가 디스크 수보다 더 많으므로 다섯 번째 블록인 B5는 다시 첫 번째 디스크에 저장하고, 위와 같은 순서를 계속 반복하게 됨. 결과적으로 데이터 블록들이 네 개의 디스크들에 균등하게 분산 저장됨. 따라서 각 블록들을 동시에 쓰거나 읽는 동작이 독립적으로 수행될 수 있고, 어느 한 디스크에 액세스가 집중되지 않기 때문에 병목 현상도 줄일 수 있음. 그러나 어느 한 디스크에만 결함이 발생하여도 전체 데이터 파일이 손상되는 문제가 있음.

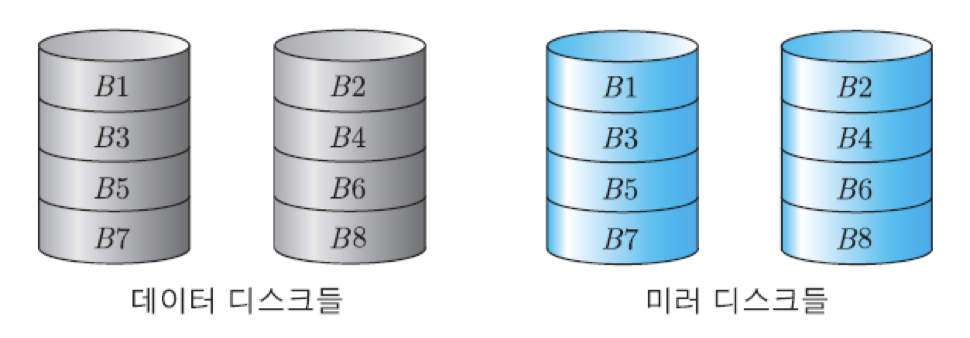

디스크 배열의 주요 단점 : MTTF의 단축

MTTF : 장치에 결함이 발생하는 평균 시간 간격

이러한 문제를 보완하기 위하여 디스크 배열의 결함 허용 능력을 높이기 위하여 RAID가 제안됨

검사디스크 : RAID에서 오류 검출 및 복구에 사용될 비트들을 저장하기 위해 추가되는 디스크

MTTR : 데이터 오류 혹은 디스크 결함 발생 시에 원래 내용을 복구하는 데 걸리는 평균 시간

6.2.2 RAID의 종류

1) RAID-1

디스크 미러링 방식 이용 : 디스크에 데이터를 저장할 때 다른 디스크에도 같은 내용을 동시에 저장하는 기법

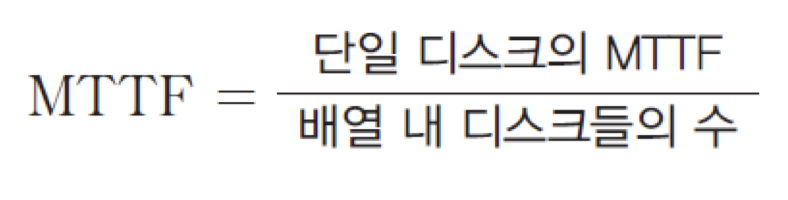

그림의 RAID-1 조직에서는 네 개의 디스크들 중에서 두 개가 데이터 디스크로 사용되고, 다른 두 개는 미러 디스크로 사용됨. 데이터 디스크들에는 데이터 블록들이 그림에서와 같이 순서대로 분산 저장되며 같은 방법으로 미러 디스크들에게도 저장됨. 만약 첫 번째 데이터 디스크에 결함이 발생하더라도, 그 디스크에 저장되어 있는 모든 데이터들이 세 번째 디스크에도 저장되어 있으므로 데이터를 잃어버릴 염려가 없게 되는 것임. 결과적으로, 이 조직은 결함 복구에 시간을 전혀 소모하지 않고도 높은 신뢰도를 얻을 수 있음.

이 조직에서 쓰기 동작은 항상 두 디스크들에서 동시에 수행되어야 함. 만약 쓰기 동작이 시작되는 순간에 두 디스크에서 헤드의 위치가 서로 다르다면, 탐색 시간에 차이가 발생하므로 쓰기 동작에 걸리는 시간이 서로 달라질 것임. 그런 경우에 쓰기 동작은 더 오래 걸리는 디스크에서의 쓰기가 완료되어야 끝남. 반면에 읽기 동작은 원하는 데이터가 저장되어 있는 두 디스크들 중에서 더 짧은 탐색 시간과 회전 지연시간이 요구되는 디스크를 선택하여 수행하면 됨.

RAID-1의 주요 단점은 가격이 높다는 것임. 그 이유는 전체 디스크에서 사용 가능한 용량이 절반으로 줄어들기 때문임. 그렇기 때문에 RAID-1은 높은 신뢰도를 요구하는 결함허용시스템에 주로 사용됨. 일반적인 컴퓨터시스템에서 사용하는 경우에는 주로 시스템 소프트웨어 혹은 중요한 데이터 파일들을 저장하는 목적으로만 사용됨.

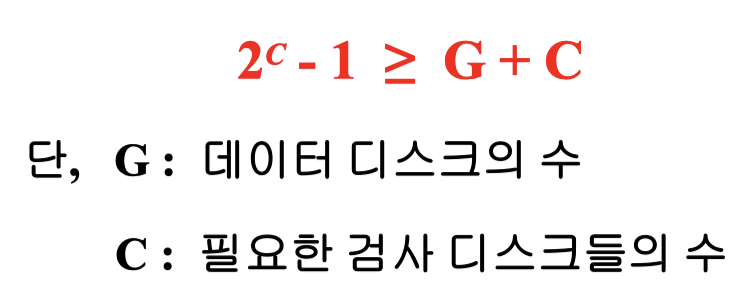

2) RAID-2

비트-단위 인터리빙 방식 사용 : 데이터 단어를 이루고 있는 비트들을 여러 개의 데이터 디스크들에 각각 한 비트씩 분산 저장하는 것

해밍 코드를 이용한 오류 검출 및 정정

필요한 검사 디스크 수를 구하는 식

3) RAID-3

RAID-2에서 사용된 검사 디스크들은 오류가 발생한 비트의 위치를 검출하기 위한 것인데, 많은 수의 검사 디스크들을 사용해야 하기 때문에 낭비가 매우 큼. 이러한 문제를 보완하기 위하여 RAID-3에서는 한 개의 패리티 디스크만 추가함.

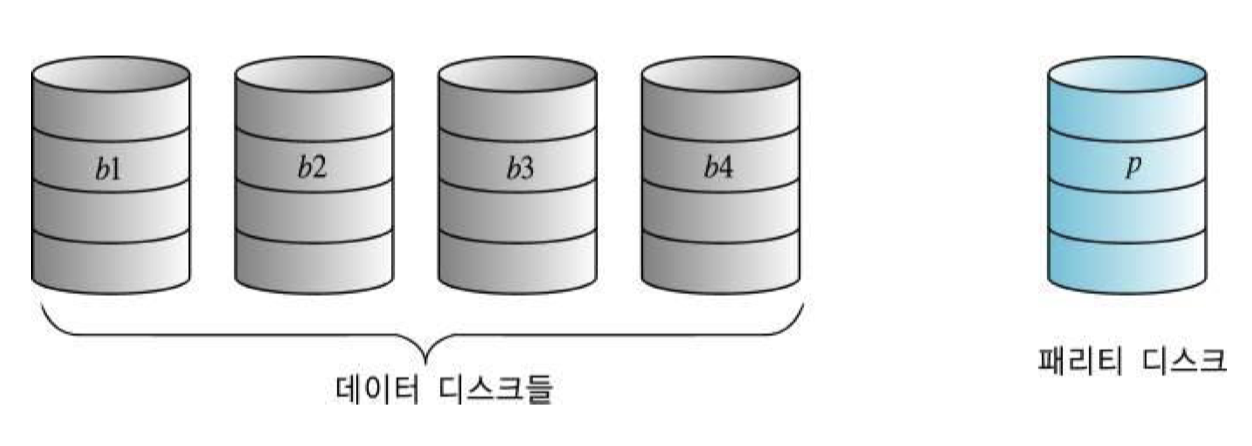

그림에서 보는 바와 같이, 데이터 디스크들의 동일한 위치에 있는 비트들에 대한 패리티 비트가 패리티 디스크의 동일한 위치에 저장됨.

데이터 딧크에 저장된 비트들을 각각 b1, b2, b3 및 b4라 하면, 패리티 비트 p

만약 어느 한 디스크에 결함이 발생하면, RAID 제어기가 내부 회로를 이용하여 그 디스크의 번호를 검출함. 그러면 다른 데이터 디스크들에 저장된 비트들과 패리티 디스크의 비트를 이용하여 결함이 발생한 디스크에 저장되어 있던 비트를 복구할 수 있음.

ex) b2가 저장된 디스크 결함 발생시

어떤 데이터 디스크에 결함이 발생하더라도 다른 디스크들의 데이터를 이용하여 결함 디스크의 데이터들을 복구할 수 있음. 다라서 결함이 발생한 상태에서도 읽기 동작은 일단 정상적으로 계속될 수 있는 것임. 그 상태에서 결함 디스크를 새로운 디스크로 대체하고, 위의 방법으로 데이터 비트들을 모두 복구하여 새로운 디스크에 저장하면 다시 정상적인 상태로 되돌아갈 수 있음.

RAID-3에서는 데이터가 비트 단위로 분산 저장되기 때문에 읽기 및 쓰기 동작이 수행될 때 배열 내의 모든 데이터 디스크들이 참여하게 됨. 또한 데이터 디스크들로부터 병렬 데이터 전송도 가능함. 따라서 전체적으로 디스크 액세스 속도가 높아짐. RAID-3의 문제점은 쓰기 동작 때마다 패리티 비트들을 갱신해야 하므로 쓰기 시간이 많이 걸림. 또한 전체 디스크 배열이 액세스 요구를 한 번에 한 개씩만 처리할 수 있음.

4) RAID-4

블록-단위 인터리빙 방식 사용

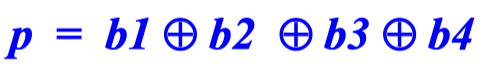

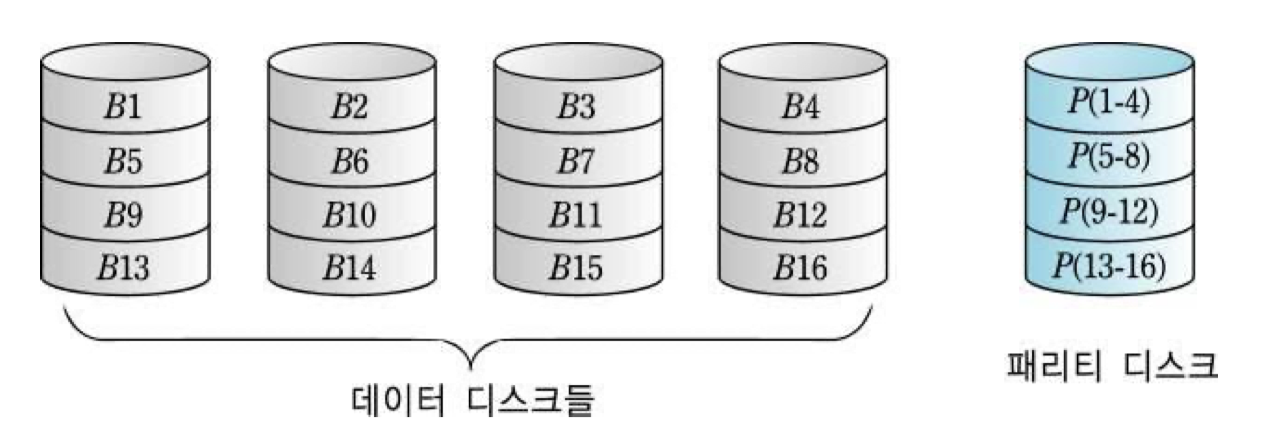

그림에서 보는 바와 같이, 패리티 디스크를 한 개 추가하여 다른 디스크들에 저장된 데이터 블록에 대한 패리티 블록을 저장함. RAID-4에서는 필요한 데이터 블록이 어느 한 디스크에 모두 저장되어 있기 때문에, 각 액세스 요구가 서로 다른 디스크들에서 독립적으로 처리될 수 있음. 따라서 여러 개의 요구들을 동시에 처리할 수 있게 됨.

그러나 이와 같이 패리티를 사용하는 조직에서는 어떤 블록의 내용을 변경하게 되면 해당 패리티 블록도 그에 따라 갱신되어야 함. 그런데 새로운 패리티 값을 구하기 위해서는 변경되는 블록뿐 아니라 다른 디스크들의 같은 위치에 저장되어 있는 데이터 블록들도 사용해야 함.

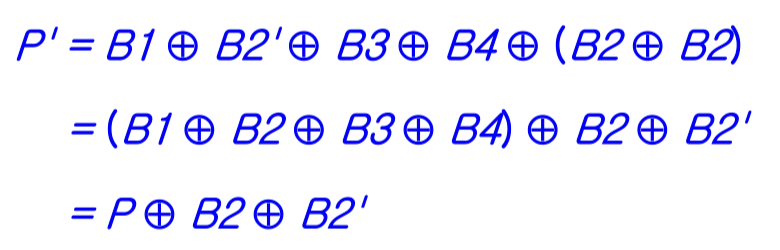

두 번째 디스크에 저장된 블록 B2를 B2'로 바꾸는 경우

세 번의 디스크 읽기(B1, B3 및 B4 읽기)와 두 번의 디스크 쓰기 동작들이 필요 -> 성능 저하

그러한 문제를 해결하기 위해서는 쓰기 동작에 필요한 디스크 액세스의 횟수를 최소화 해야함

즉, 새로운 패리티는 원래의 패리티와 원래 데이터 및 새로운 데이터 사이에 XOR 연산을 수행하면 구할 수 있음. 이를 위해서는 원래의 패리티와 원래의 데이터를 읽어오고, 새로운 데이터와 새로운 패리티를 각각 쓰면 됨. 결과적으로, 디스크 쓰기 동작을 위해서는 네 번의 디스크 액세스(두 번의 읽기와 두 번의 쓰기)만 필요하게 되며, 이것은 데이터 디스크들의 수가 몇 개이든 항상 동일함.

그러나 이 조직에서는 어떤 디스크에든 데이터 블록을 쓸 때마다 패리티 디스크가 반드시 두 번씩 액세스되어야 함. 따라서 패리티 디스크에 액세스들이 집중되기 때문에 병목 현상이 발생하여 성능이 저하되는 문제가 있음

-> RAID-5가 제안

5) RAID-5

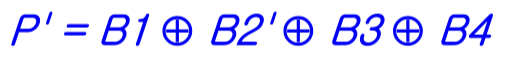

RAID-5의 기본적인 설계 개념은 RAID-4와 동일하며, 패리티 블록들을 모든 디스크에 분산 저장하는 점만 다름.

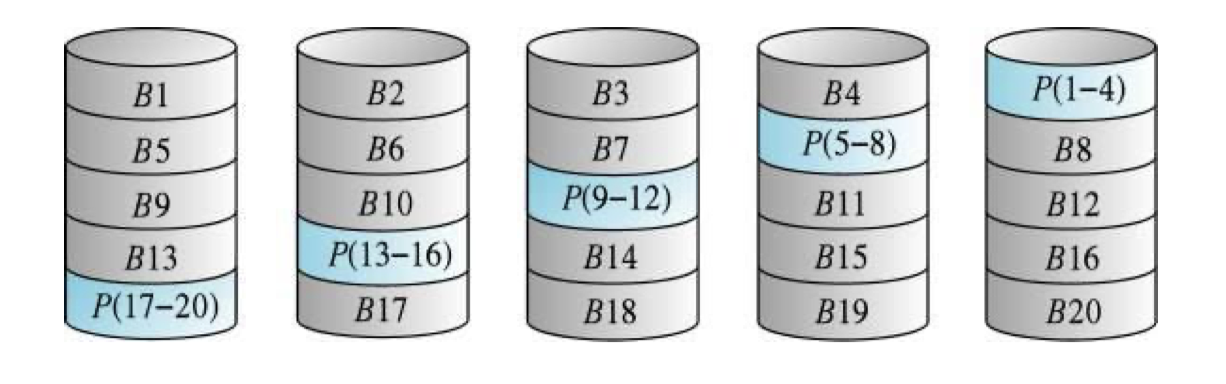

그림은 다섯 개의 디스크들이 하나의 그룹을 형성하고 있고, 각 디스크는 블록들을 다섯 개씩 저장하고 있는 예를 보여주고 있음. 그런데 RAID-4와는 달리, B1, B2, B3 및 B4에 대한 패리티 블록인 P(1-4)는 다섯 번째 디스크에 저장하고, B5, B6, B7 및 B8에 대한 패리티 블록인 P(5-8)는 네 번째 디스크, 그리고 나머지 패리티 블록들도 같은 방법으로 서로 다른 디스크에 저장하고 있음. 만약 디스크들에 더 많은 블록들이 저장된다면, 그 다음의 패리티 블록인 P(21-24)는 다시 다섯 번째 디스크에 저장하는 라운드-로빈 방식을 적용함.

이와 같은 분산 저장 방식을 사용하면, 패리티 갱신을 위한 디스크 액세스들이 분산되어 패리티 디스크에 대한 병목 현상이 완화될 뿐 아니라, 쓰기 동작들을 병렬로 수행할 수도 있게 됨.

순차적인 여러 블록들을 동시에 쓰는 '큰 쓰기'의 경우에는 별 문제가 없지만, 어느 한 블록만 쓰는 '작은 쓰기'의 경우에 문제 발생

작은 쓰기 문제 : RAID-5에서 한 블록을 디스크에 쓰는 경우에 네 번의 디스크 액세스가 필요하게 되는 문제점

6.3 플래시 메모리와 SSD

CPU가 프로그램을 실행하는 중에 주기억장치와 영구저장 능력을 가진 보조저장장치 간에는 아래와 같은 이유로 빈번한 정보 전송이 발생

• 시스템 초기화(부팅) 과정에서 OS 프로그램을 주기억장치로 적재

• 응용 프로그램이 처음 수행될 때는 디스크로부터 주기억장치로 적재

• 새로이 생성되거나 수정된 데이터는 보조저장장치에 영구 저장

• 주기억장치 공간이 부족한 경우에는 적재되어 있는 블록을 보조저장장치로 내보내고, 새로운 블록을 읽어와서 그 공간에 적재

SSD(Solid-State Drive) : 플래시 메모리 칩들을 이용하여 구성한 대용량 저장장치이며, 반도체 드라이브라고도 부름

플래시 메모리 : EEPROM의 일종으로서, 저장밀도가 높고 저전력 고신뢰성의 특징을 가진 반도체 기억장치

6.3.1 플래시 메모리

플래시 메모리의 출현 활성화 계기 -> 비휘발성 반도체 기억장치 분야

• 높은 저장 밀도: 한 개의 트랜지스터만 사용하여 한 비트 저장

• 낮은 전력소모량, 높은 신뢰성, 속도 향상

1) 동작 원리

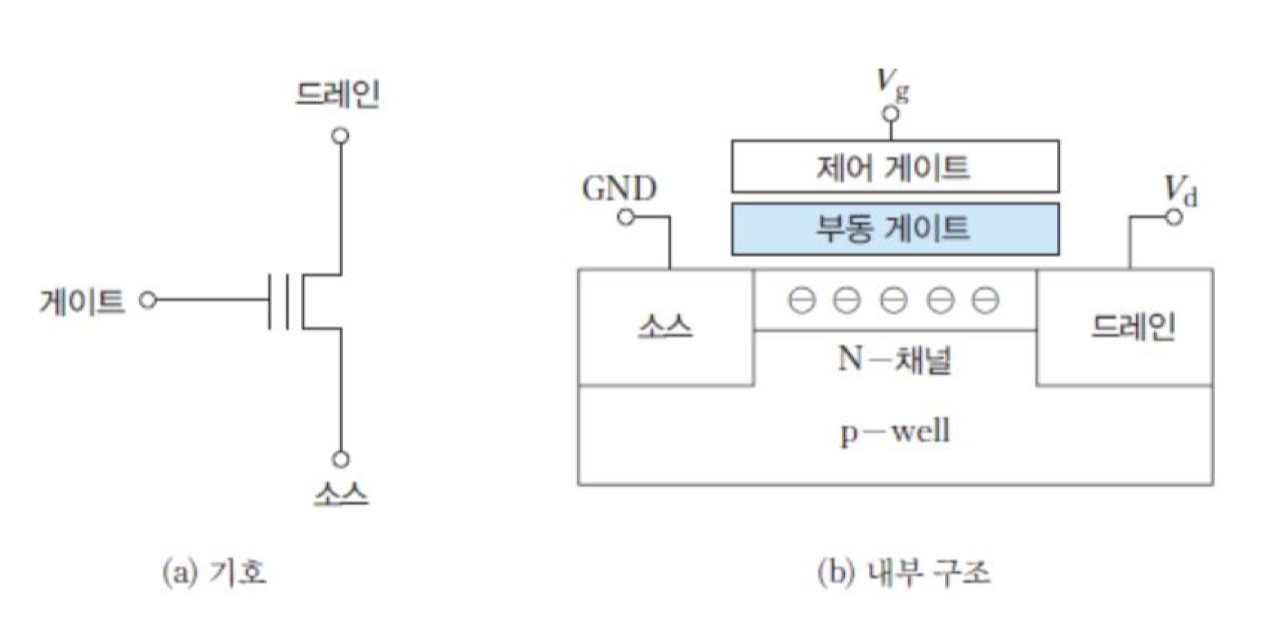

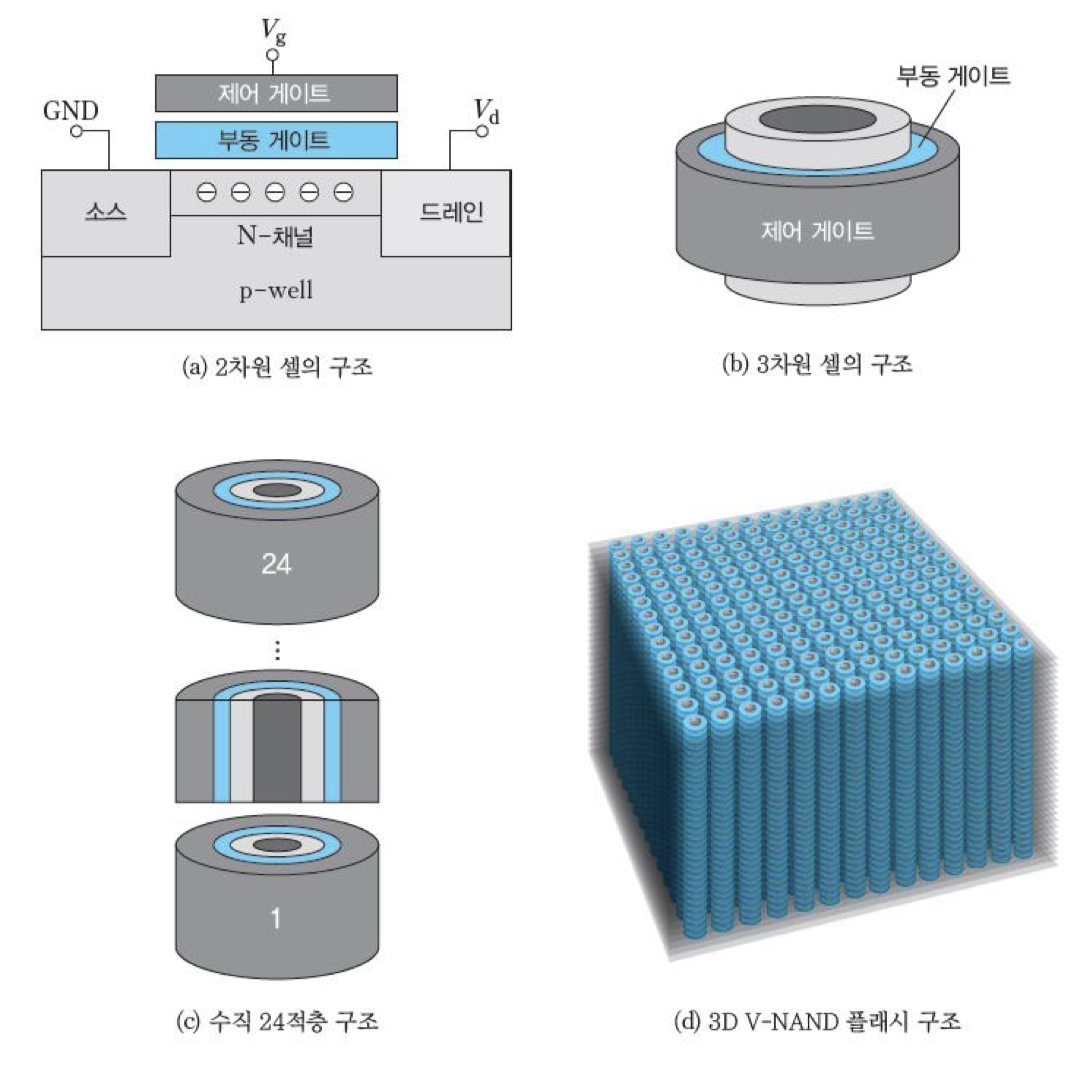

플래시 메모리에서 셀의 구현에는 NMOS 트랜지스터가 사용되며, 그 기호는 그림 (a)와 같음.

기호를 보면, 드레인, 소스 및 게이트로 구성되는 일반적인 NMOS 트랜지스터와 별 차이가 없지만, 게이트가 두 개로 표시되어 있음. 내부 구조를 좀 더 자세히 표시한 그림 (b)에서 볼 수 있듯이, 게이트는 제어 게이트와 부동 게이트로 이루어짐. 그 중에서 부동 게이트는 정보 저장의 핵심적인 역할을 수행하게 되는데, 절연체인 산화막으로 둘러싸여 있어서 전자 NMOS 트랜지스터는 드레인 단자로 양의 전압(Vd)이 인가되고 소스는 접지(GND)로 접속된 상태에서 적절한 크기의 게이트 전압(Vg)이 인가되면, 드레인과 소스 사이의 N-채널을 통하여 전자들이 이동하면서 전류가 흐르게 됨. 그런데 만약 제어 게이트로 충분의 높은 전압의 Vg를 인가한다면, 강력한 전기장이 발생하게 되어 N-채널을 통과하던 전자들의 일부가 절연체인 산화막을 통과하여 ㅂ동 게이트로 들어아게 됨. 이과 같은 현상을 터널링 효과라고 부르며, 부동 게이트로 전자들이 흘러가는 것을 터널 주입이라고 함. 그 후에 게이트 전압이 인가되지 않으면 터널링 효과는 사라지고, 부동 게이트에 들어간 전자들은 그 안에 갇히게 됨. 지금까지 설명한 것이 플래시 메모리에 대한 쓰기, 즉 '프로그래밍'동작임. 이 과정에서 부동 게이트로 들어가는 전자들의 수는 인가하는 게이트 전압의 높이에 따라 달라지며, 그들은 전원 공급이 중단되어도 그대로 머물러 있음으로써 영구저장 기능을 수행하게 되는 것임.

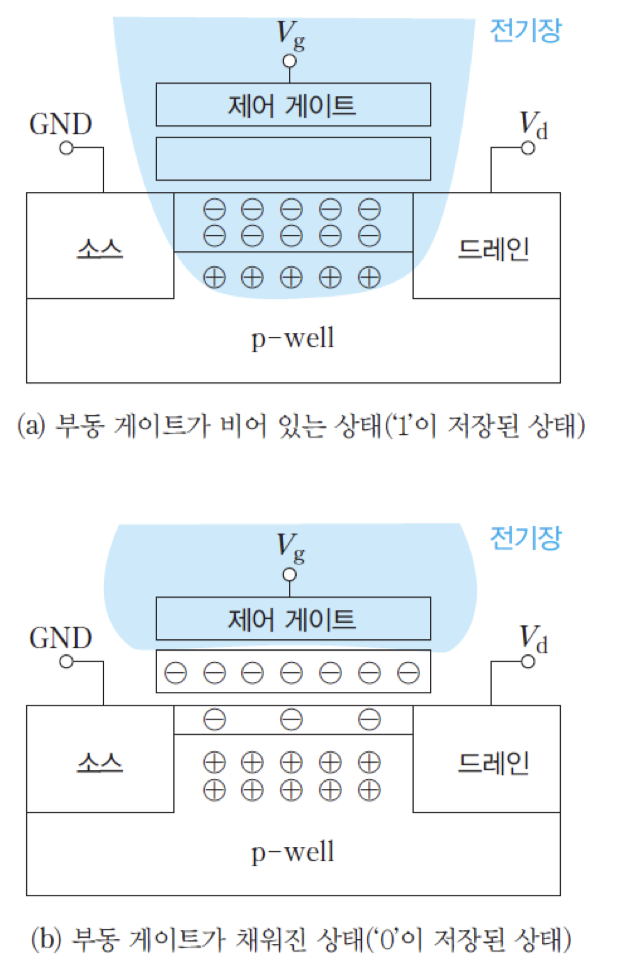

그와 같이 정보가 저장된 상태에서, 하위의 p층에 접속된 별도의 단자를 통하여 충분히 높은 전압을 인가하면, 그 방향에서 발생한 전기장의 영향으로 인하여 부동 게이트에 갇혀있던 전자들이 산화막을 통과하여 N-채널로 빠져나오게 되어 부동 게이트는 비게 됨. 이러한 과정을 터널 릴리스라고 하는데, 메모리 셀에 대한 삭제 동작에 해당함. 즉, 셀에 대하여 삭제 동작이 수행되면, 그 셀은 '논리적 1' 상태가 되며, 그 후에 쓰기 동작에서 '0'을 저장한다면, 다시 부동 게이트가 전자들로 채워짐. 반면에 '1'을 저장한다면, 그대로 두면 되는 것임.

소스가 접지된 상태에서 드레인 양의 전압을 인가하면 N-채널을 통하여 전자가 흐를 수 있는 상태가 됨. 그 상태에서 제어 게이트로 정상 전압의 Vg를 인가하면 게이트 측으로부터 전기장이 발생하게 되는데, 그때 만약 부동 게이트가 비어 있는 상태라면 그림 (a)에서와 같이 전기장의 영향 때문에 p층에 있던 정공들이 아래로 밀려나서 N-채널이 더 넓어짐. 그러면 드레인과 소스 사이에는 더 많은 전류가 흐를 수 있게 되어 트랜지스터는 ON 상태가 되는데, 이것은 '1'을 읽은 결과에 해당함.

그런데 만약 그림 (b)와 같이 부동 게이트가 전자들로 채워져 있다면, 그 전자들이 전기장의 영향을 차단하게 되어 N-채널은 넓어지지 못하며, 결과적으로 전류가 매우 적게 흐르게 됨. 이것은 트랜지스터의 OFF 상태를 의미하며, '0'을 읽은 결과에 해당함.

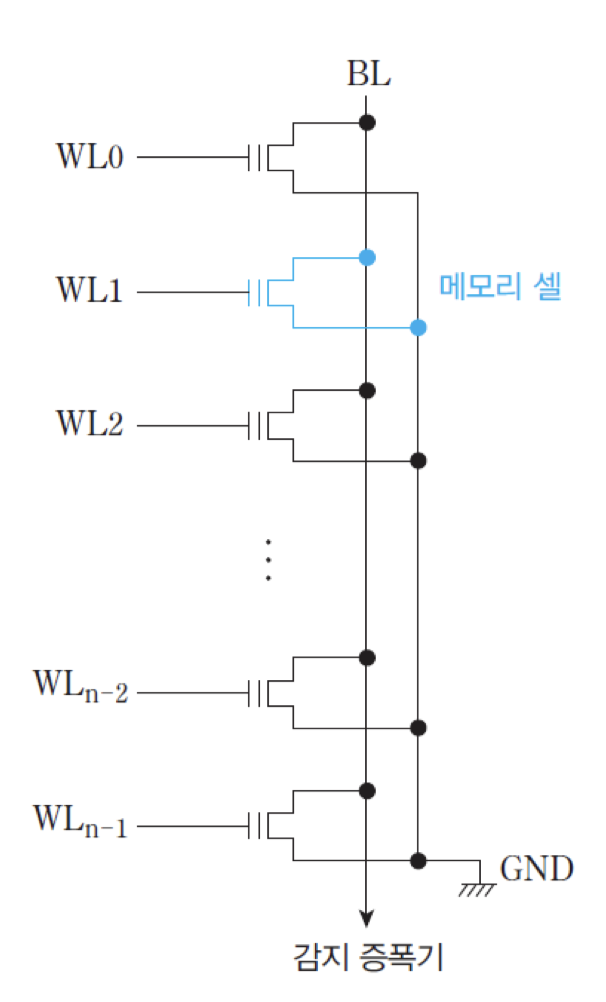

플래시 메모리는 내부 회로의 구성 방식에 따라 NOR형과 NAND형으로 분류됨. NOR형은 트랜지스터들이 첫 번째 그림과 같이 병렬로 접속됨. 여기서 병렬접속이란 모든 트랜지스터들이 Vcc가 들어오는 비트선과 접지 사이에 직접 연결되어 있는 형태를 말함. 그와 같이 연결되면 모든 트랜지스터들은 독립적인 스위칭 동작을 수행할 수 있게 됨. 트랜지스터의 게이트에 입력되는 신호는 단어 선을 통하여 인가됨.

만약 셀 배열의 어느 한 트랜지스터에 '0'이 저장되어 있다면, 게이트로 양의 전압(예 : +5V)이 인가되더라도 트랜지스터가 OFF 상태에 있게 되므로, 비트 선의 전압은 +V5를 그대로 유지하게 됨. 반면에, '1'이 저장되어 있을 때 게이트 전압이 인가되면 트랜지스터는 ON 상태가 되어 전류가 흐르게 되므로, 비트 선의 전압은 0V로 떨어지게 됨. 그런데 그림에서 보는 바와 같이 트랜지스터들이 병렬로 접속되어 있기 때문에, 선택된 어느 한 트랜지스터에 저장된 값만 '1'이라도 비트 선의 전압은 0V가 됨. 즉, NOR 게이트와 같이 동작하며, 따라서 NOR형 플래시라고 불림. 그 비트 선의 값은 출력단의 감지 증폭기로 들어가 스위칭 회로에 의해 반전되어, 최종 출력값으로는 원래 저장된 값인 '1'이 나가게 됨. 이와 같은 구조로 인하여 NOR형에서는 각 셀 단위로 선택 신호를 인가하여 저장된 값을 읽을 수 있음.

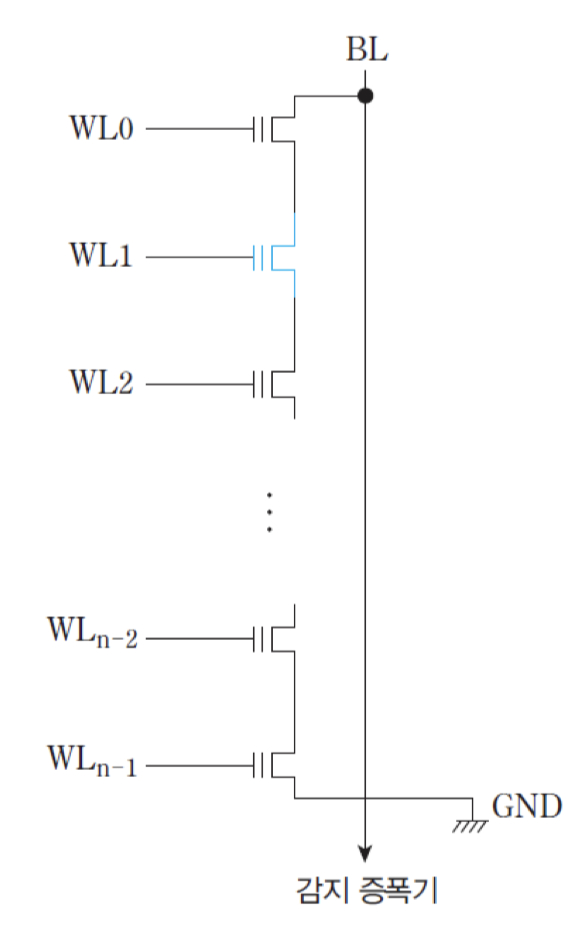

NAND형의 내부 조직은 두 번째 그림과 같이 배열의 모든 트랜지스터들이 직렬로 접속됨. 즉, 비트 선은 첫 번째 트랜지스터의 드레인으로만 접속되고, 그 소스 단자는 두 번째 트랜지스터의 드레인으로 접속되는 방식이며, 가장 아래에 위치한 트랜지스터의 소스만 접지로 연결됨.

NAND형 플래시에서는 각 트랜지스터의 부동 게이트가 비어 있는 상태에서는 전류가 흐르는 상태가 되기 위한 문턱 전압이 -3V 정도임. 그리고 부동 게이트가 전자들로 채워져 있는 상태에서는 Vth = +1V 임. 즉, Vg가 1V 이상이 되어야 트랝니스터가 ON 상태로 될 수 있는 것임.

초기 상태에서는 모든 게이트들로 인가되는 WL들의 전압이 +5V가 되어, 트랜지스터들이 모두 ON 되어 있음. 따라서 비트 선의 전압은 0V가 됨. 그런데 그 중의 어느 한 셀이 선택되어 읽기가 수행될 때는 그 셍의 게이트 전압(Vg)은 0V가 됨. 그때 만약 셀에 저장되어 있는 값이 '1'이라면, Vth = -3V이므로 Vg > Vth가 되어 트랜지스터는 ON이 됨. 따라서 비트 선은 0V를 그대로 유지하고, 최종 출력값은 '1'이 됨. 그런데 만약 그 트랜지스터에 저장된 값이 '0'이라면, Vth = +1V이므로 Vg < Vth가 되어 트랜지스터는 OFF 상태에 있게 됨. 따라서 트랜지스터들로 전류가 흐르지 못하기 때문에 비트 선은 5V를 유지하게 됨. 즉, 읽고자 하는 트랜지스터에 저장된 값에는 상관없이 비트 선의 전압은 5V가 되는 것임. 그것은 NAND 연산에 해당하므로 NAND형 플래시라고 불림. 이 경우에도 비트 선의 전압은 감지 증폭기에 의해 반전되어, 최종 출력으로는 원래 저장된 값을 내보내게 됨.

지금까지의 설명을 정리해보면, NOR형 플래시에서는 병렬로 접속된 트랜지스터들의 드레인과 소스 단자가 각각 비트 선과 접지로 직접 연결되어 있음. 따라서 각 셀 단위의 읽기와 쓰기가 가능하지만, 접속선들의 수가 트랜지스터 당 세 개씩이 필요하기 때문에 공간을 많이 차지하여 칩 당 저장용량이 줄어드는 단점이 있음. 반면에, NAND형 플래시에서는 비트 선은 최상단 트랜지스터의 드레인 단자로만 접속되고 접지선은 최하위 트랜지스터의 소스 단자로만 접속되기 때문에 접속선의 수가 대폭 줄어들어, 칩 당 저장용량이 NOR형보다 더 커질 수 있음.

2) 내부조직

블록들로 구성되며, 각 블록은 다수의 페이지들로 구성

• 페이지 크기: 2Kbyte, 4Kbyte, 16Kbyte, 64Kbyte, 등

블록 : 플래시 메모리에서는 한 블록이 64개 혹은 128개의 페이지들로 이루어지며, 각 페이지의 크기는 2K 혹은 4K바이트

읽기, 쓰기 및 전송: 페이지 단위

삭제: 블록 단위

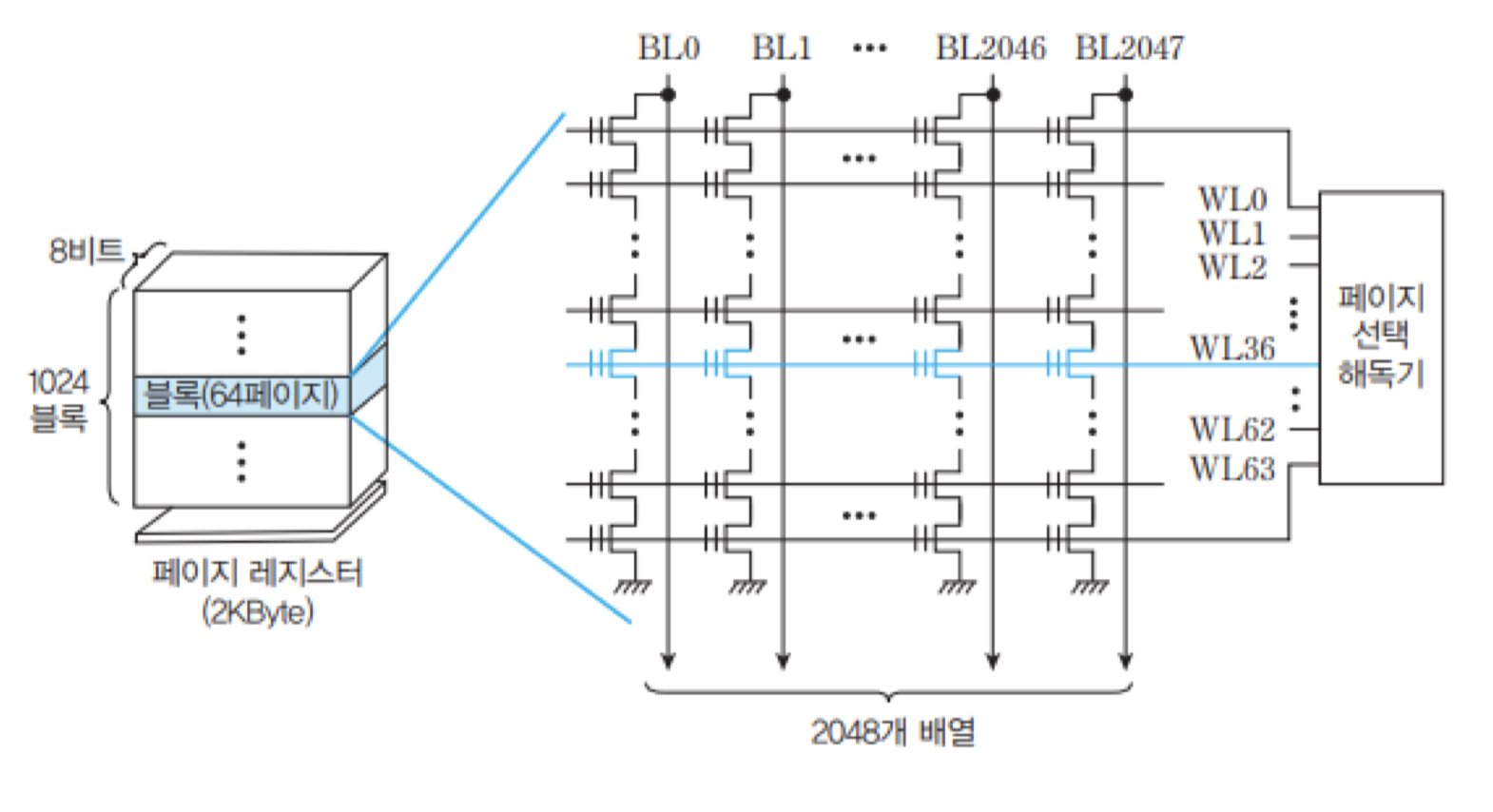

그림에서 보는 바와 같이 1Gbit 플래시 메모리는 y축 방향으로 1024개의 블록들로 이루어짐. 그리고 각 블록은 64개의 페이지들로 구성됨. 즉, 64장의 페이지들이 위로 쪼개져 하나의 블록을 이루고, 그러한 블록들 1024개가 쌓여 있는 형태임. 각 페이지는 x축 방향으로 2048개의 셀들로 구성되어 있으며, z 방향으로는 8개씩의 셀들이 있기 때문에 페이지의 크기는 2KByte가 됨.

그림의 우측에는 각 블록을 위한 NAND형 셀 배열을 좀 더 자세하게 보여주고 있음. 즉, 수식 방향의 셀 배열은 직렬로 연결된 64개의 트랜지스터들로 이루어지며, 그러한 셀 배열들이 수평 방향으로 2048개가 나열된 형태임. 이러한 칩에서 어떤 한 페이지에 대한 읽기 동작이 수행된다면, 그 우측의 페이지 선택 해독기의 한 출력이 수평 방향으로 위치한 2048개 트랜지스터들의 게이트로 동시에 인가됨. 결과적으로, 선택된 페이지의 모든 셀들이 동시에 읽혀짐. 이러한 동작은 z 방향의 8개 배열들에 대하여 같은 방법으로 수행됨. 따라서 해당 페이지 내의 모든 비트들이 인출되어, 같은 크기의 페이지 레지스터에 적재된 다음에 외부 버스로 나가게 됨. 이와 같은 구조로 인하여 읽기 및 쓰기 동작은 페이지 단위로 수행되며, 바이트 단위의 동작이 가능한 NOR형에 비해 액세스 시간이 더 걸리는 것임.

그림과 같이 구성된 칩의 전체 용량은 {(2048 x 8비트) x 64페이지} x 1024블록 = 1Gbit = 128Mbyte가 됨. 그런데 많은 수의 비트들이 저장되는 칩인만큼 오류 발생의 가능성도 있기 때문에, ECC비트들이 함께 저장됨. 따라서 이 칩의 경우에는 페이지마다 64Byte 크기의 ECC가 추가적으로 저장되어 실제로 각 페이지에는 (2K + 64)Byte씩 저장되며, 같은 비율로 계산하면 각 블록에는 (128K + 4K)Byte가 저장됨.

플래시 메모리의 내부 조직의 유형으로는 여러 가지가 있는데, 블록 당 페이지의 수는 32개, 64개, 128개 등이며, 페이지의 크기도 2KByte, 4KByte, 16KByte 및 64KByte로 다양함. 이와 같이 액세스 및 전송의 기본 단위인 페이지의 크기가 일정하지 않으며, 하드 디스크의 섹터 크기와도 다름. 그리고 삭제 동작은 블록 단위로만 가능함.

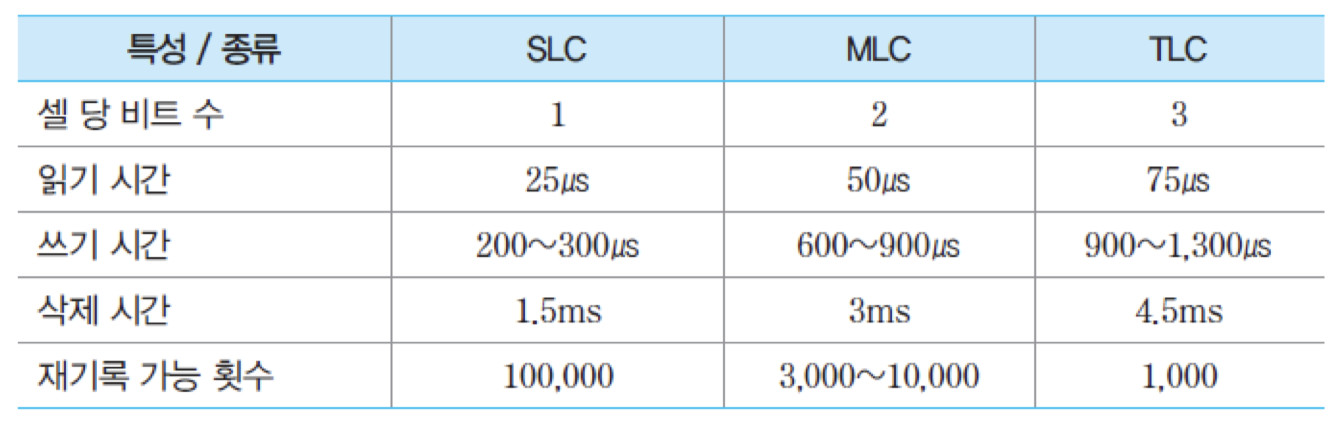

3) SLC, MLC 및 TLC

부동 게이트로 들어가는 전자들의 수를 조정하여 각 셀에 저장되는 상태(비트)의 수를 증가시킴

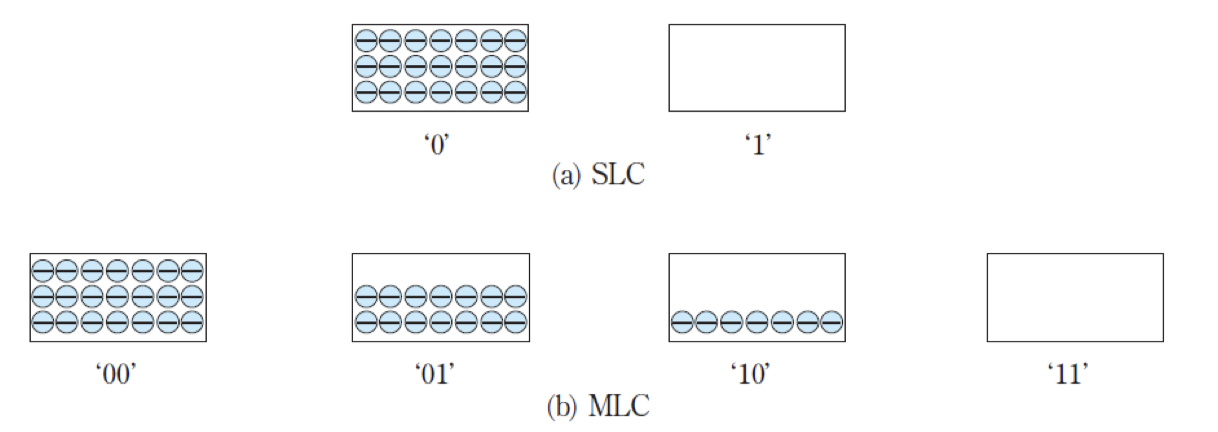

• SLC(single-level cell): 두 가지 상태를 가짐으로써 한 비트를 저 장하는 셀

• MLC(multi-level cell): 셀의 상태를 4가지(00,01,10,11)로 구분 -> 메모리 셀 당 2비트씩 저장

그림은 그림 (b)에서 부동 게이트만 확대하여 SLC와 MLC에 대한 전자 수의 차이를 개념적으로 보여주고 있음. 즉, SLC에서는 부동 게이트가 전자들로 채워진 상태와 비어 있는 상태로서 0과 1을 구분하는 반면에, MLC에서는 채워지는 전자들의 수를 네 단계로 구분하는 것을 볼 수 있음.

• TLC(triple-level cell): 셀의 상태를 8가지(000, 001, 010, 011, 100, 101,110,111)로 구분 -> 셀 당 3비트씩 저장

MLC 및 TLC의 문제점

전자 수 조정을 위한 세밀한 작업 필요

데이터 구분의 어려움으로 인한 액세스 속도 저하

오류 발생 빈도 증가

수명 단축

SLC, MLC 및 TLC의 특성 비교

4) 3차원 V-NAND 플래시 메모리

반도체 제조 공정이 더욱 미세화 됨에 따라, 셀이 점차 더 작아지고 셀 간의 간격이 더 좁아지게 되면서 전자들이 누설되는 간섭 현상이 심화됨. 그 결과, 저장된 데이터를 판독하기 어려워지는 물리적인 한계에 도달함. 그러한 문제를 극복하기 위하여 단층 구조의 주택을 수 십층 쌓아올리는 아파트와 같은 원리로 셀들을 수직 방향으로 적층하는 기술이 새로 개발됨.

그림은 3D V-NAND 플래시의 설계 원리를 단계적으로 보여주고 있음. 먼저 그림 (a)는 2차원 메모리 셀의 내부 구조인 그림 (b)와 같은 것임. 3차원 구조 설계의 첫 번째 단계로서, 원래 구조 하단의 사각형 부분을 그림 (b)의 중심부와 같이 원통관으로 만듦. 그런 다음에, 청색으로 표시된 부동 게이트를 원통형으로 변경하여 그 주위를 둘러싸도록 제조하며, 남아 있는 제어 게이트도 부동 게이트의 바깥을 둘러싸는 형태로 하나의 3차원 구조 셀을 완성함.

두 번째 단계는 수직 적층 기술을 사용하여 그림 (c)와 같이 메모리 셀들을 위로 계속 쌓아 올리는 것임. 이 때 그림에서 보는 바와 같이 셀과 셀 사이에 약간의 공간을 확보하면 셀들 간의 데이터 간섭 현상을 감소시킬 수 있음. 이 그림은 32개의 셀들을 적층시킨 모습을 보여주고 있음.

3D V-NAND 플래시 메모리를 위한 최종 공정은 그림 (d)와 같이 다수의 실리콘 다이들을 아래위로 겹쳐 부착시킨 다음에 미세 크기의 홀들을 만드록, (c)와 같은 수직 다층 구조의 셀들을 그 홀 내부에 삽입 제조하는 것임. 이와 같은 공정은 수억 개의 홀들을 뚫고 각 층마다 전극을 연결하는 에칭 기술 및 수직 셀을 만드는 게이트 패턴 기술과 같은 첨단 반도체공정 기술들이 필요함.

그림 (b)와 같은 3차원 셀에서는 부동 게이트의 공간이 확장되기 때문에 더 많은 수의 전자들을 주입시킬 수 있어서, 전자 수를 기준으로 데이터의 값을 구분하는 과정이 용이해져 오류가 줄어들게 됨. 즉, 앞에서 언급한 TLC의 결점이 보완되는 것임. 더 나아가서, 부동 게이트 내 전자들의 수를 16가지 등급으로 구분하여 4-비트 데이터를 저장하는 QLC(quadruple-level cell)를 제조하는 것도 가능해짐. 그 결과, 플래시 메모리의 저장 용량이 더욱 증가하여 테라비트급의 칩들도 출현하고 있음.

최근에는 부동 게이트 대신에 두께가 얇은 부도체를 이용하여 전자들을 저장하는 CTF 방식이 개발되어 셀의 높이가 더욱 낮아짐에 따라, 적층 구조의 층수가 96층 혹은 그 이상으로 계속 높아지고 있음. 또한 칩 내부에서 셀 배열의 옆에 위치하던 주변부를 아래 부분에 위치시키는 PUC(peripheral under cell) 기술을 적용하는 4D NAND플래시도 개발됨.

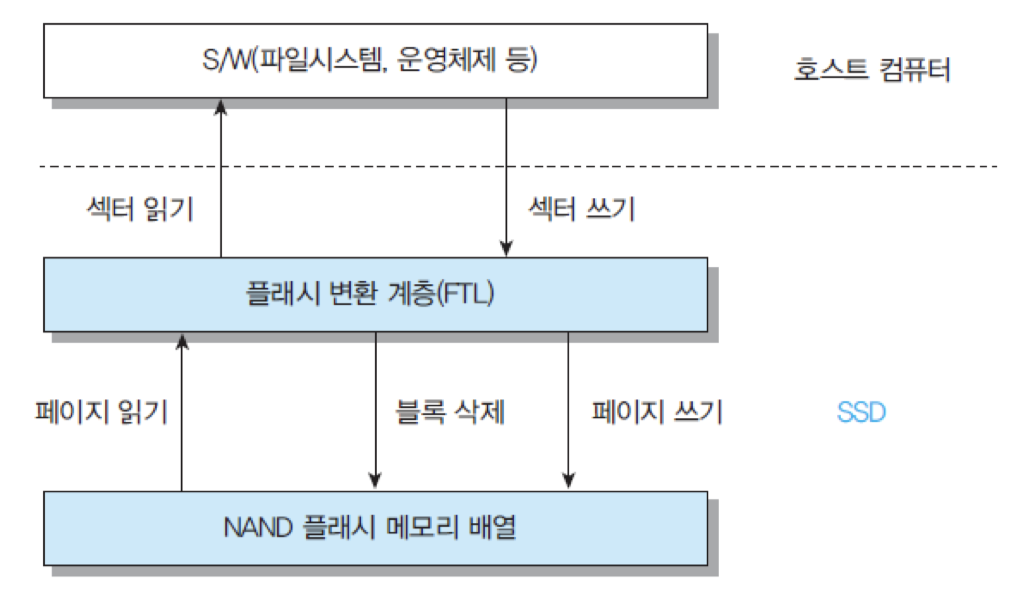

6.3.2 SSD

SSD는 기계적 장치라는 단점을 가진 하드 디스크를 대체하기 위하여 개발된 대용량 비휘발성 반도체 저장장치임

구성요소: 저장밀도가 높은 NAND형 플래시 메모리

다수의 플래시 메모리들을 배열로 구성하여 패키징

장점: 높은 안정성 및 신뢰도

결점: 저장용량 대비 가격이 HDD에 비해 다소 높음

SSD 제어기 : SSD에서 데이터 저장과 인출, 칩 관리 등과 같은 핵심적인 기능을 수행하는 전자회로 모듈

플래시 변환 계층(FTL) : 플래시 메모리의 블록/페이지 구조를 논리적으로 HDD의 섹터와 같은 구조로 변환해주는 S/W

플래시 변환 계층을 포함한 SSD 구성

FTL은 페이지 주소와 섹터 주소간의 매핑 외에도, SSD의 성능 향상을 위하여 아래의 기능들을 수행

• 마모 평준화

• 쓰레기 수집

• 초과 대비공간

마모 평준화

필요성

• 플래시 메모리의 셀 수명 한계

• MLC 및 TLC에서 그 문제는 더욱 심각

• 삭제 및 쓰기 동작들이 일부 블록이나 페이지들에 집중될 경우, 전 체 SSD 수명 단축

해결책: 마모 평준화(모든 페이지들이 고르게 사용되도록 저장 위치 조정)

• 각 페이지의 사용 횟수를 페이지 레지스터에 기록 하여 쓰기 동작 시 참고

• 기록 횟수가 적은 페이지 우선 사용

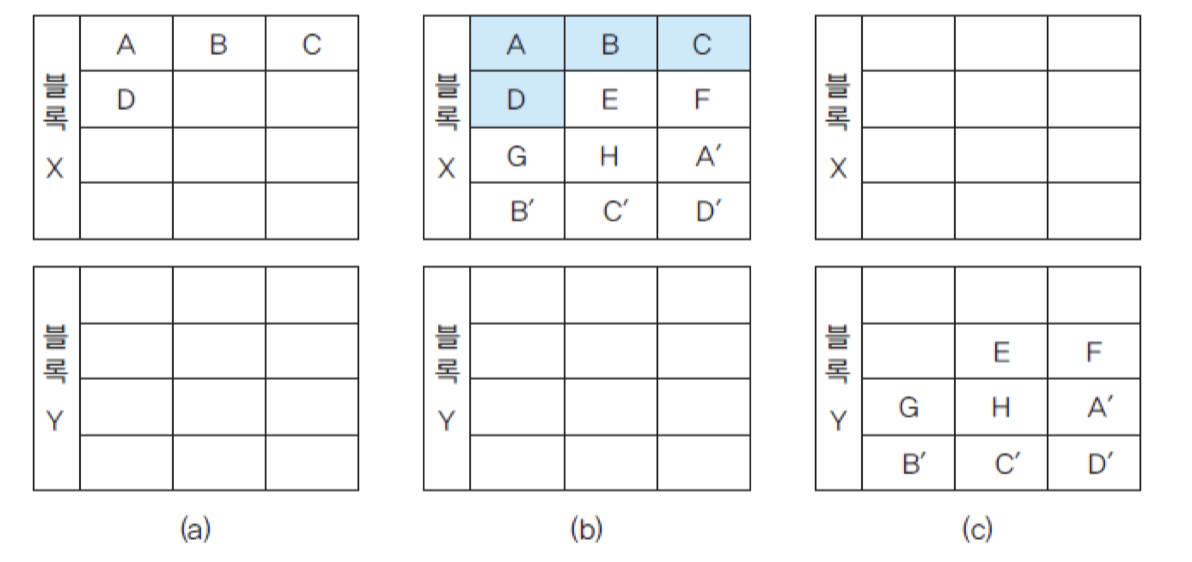

쓰레기 수집

필요성

• 삭제 동작이 블록 단위로만 가능

• 페이지 수정 시 다른 위치에 새로운 페이지를 쓰고, 원래 페 이지(무효 상태)는 삭제 필요

해결책

• 페이지 내용은 수정되었지만 삭제하지 못한 원래 페이지는 쓰레기로 표시

• 쓰레기로 표시된 페이지가 많이 축적된 블록을 한꺼번에 삭제 : 쓰레기 수집 (삭제 전에 유효 페이지는 미리 다른 블록으로 이동)

그림은 쓰레기 수집 과정의 한 예를 보여주고 있음. 그림에는 블록 X와 블록 Y가 각각 12개씩 페이지씩으로 구성되어 있음. 먼저 (a)에서는 네 개의 페이지들 A, B, C, D가 블록 X에 저장된 상태임. 그 후에 새로운 페이지들인 E, F, G, H를 추가로 저장하고, 기존의 페이지들은 각각 A', B', C', D'로 수정하려고 함. 그런데 새로운 페이지들은 그림 (b)에서 보는 바와 같이 그 다음 위치의 페이지들에 저장되지만, 수정될 페이지들은 원래 페이지의 위치에 덧쓰기를 할 수가 없기 때문에 각각 다른 위치에 저장됨. 그 결과로서, 그림에서 청색으로 표시된 네 개의 원래 페이지들은 무효 상태가 되었지만, 페이지 단위로는 삭제할 수가 없으므로 그대로 둘 수밖에 없음. 즉, 이 페이지들은 쓰레기인 것임. 그런데 이 상태에서는 무효 페이지들이 저장되어 있는 공간을 다른 용도로도 사용할 수 없기 때문에 그들을 삭제해야 하는데, 그 동작을 위해서는 먼저 그림 (c)와 같이 블록 X에 있는 유효 페이지들을 다른 블록인 Y로 이동시켜야 함. 그런 다음에 블록 X에 남아있는 무효 페이지들을 포함한 블록 전체를 삭제하면 됨. 이와 같이 유효한 페이지들을 다른 블록으로 이동시키고, 기존 블록 전체를 삭제하는 과정을 쓰레기 수집이라고 함.

위의 과정에서 블록 X로부터 Y로 페이지들을 복사하는 동작에 많은 시간이 걸리기 때문에, 복사할 필요가 없는 무효 페이지들을 선별할 수 있어야 함. 이를 위하여 무효 페이지들이 발생할 때마다 운영체제가 SSD 제어기에게 그 사실을 알려주도록 할 수 있는데, 이 동작은 TRIM이라고 불리는 명령에 의해 이루어짐. 즉, TRIM 명령은 OS로 하여금 SSD 제어기에게 무효가 된 페이지들을 통보해줌으로써 쓰레기 수집의 효율을 높여 SSD의 성능을 향상시켜주는 보조 기능임. 쓰레기 수집과 TRIM 명령은 삭제 횟수를 최소화시키는 데도 도움이 됨.

초과 대비 공간

필요성

• 마모 평준화 및 쓰레기 수집의 효율을 높이기 위해서는 (수정된 페이지와 원래 페이지의 일시적 중복 저장을 위한) 여유 저장 공간 필요

해결책

• SSD 내부에 여분의 저장 공간 제공