정의

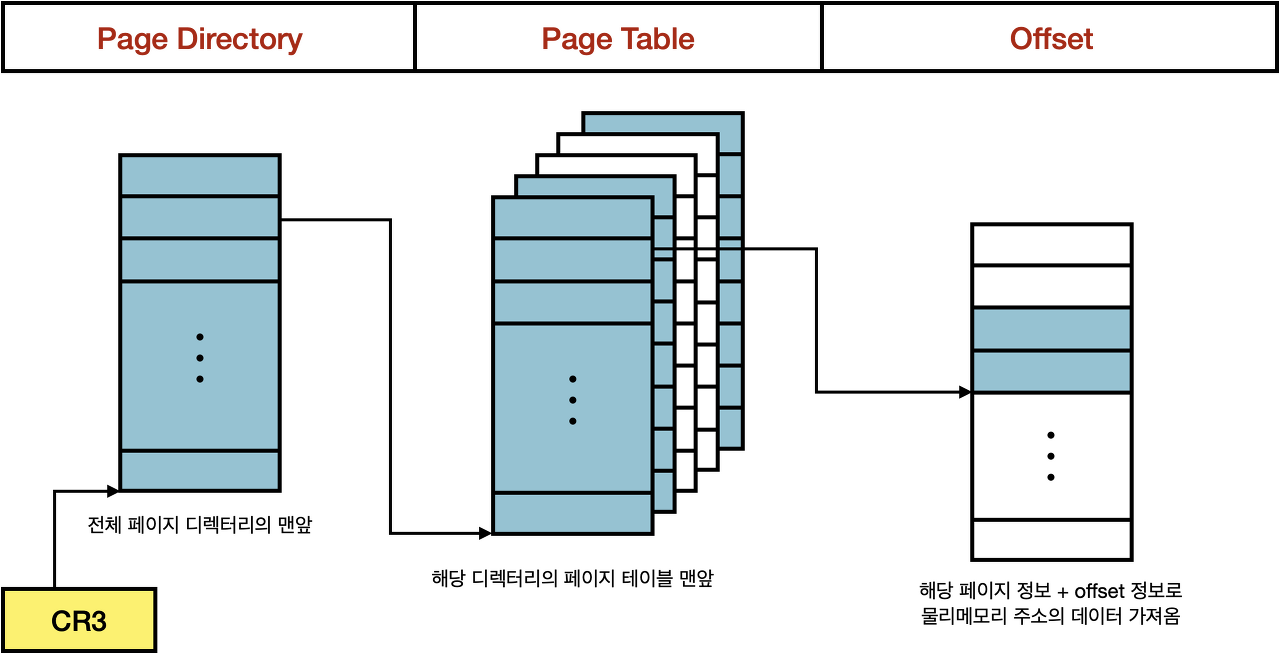

다중단계 페이징 시스템이란, Page Directory로 영역을 구분하여, 그 중에 데이터가 있는 디렉터리만 페이지 테이블을 만들어 메모리 공간을 절약하는 개념이다.

전체 페이지 32bit 중, 12bit는 원래대로 페이지 주소로부터의 변위를 나타내는 정보고, 나머지 20bit 중 10bit는 페이지 디렉터리 정보, 10bit는 해당 디렉터리의 페이지 테이블이다. 리눅스에서는 3단계로 구분했다가, 요즘에는 더 복잡하게 4단계로 나누어 처리한다.

1) CR3 레지스터의 전체 페이지 테이블의 맨 앞이 페이지 디렉터리의 맨 앞 주소를 가리키게 된다.

2) 해당 주소에 대응하는 디렉터리에 가면, 그 디렉터리에 대한 페이지 정보를 가진 페이지 테이블 주소의 맨 앞이다.

3) 그 페이지 테이블에서 해당 페이지 번호를 찾아서 페이지 정보와 offset 정보로 물리메모리 주소의 데이터를 가져온다.

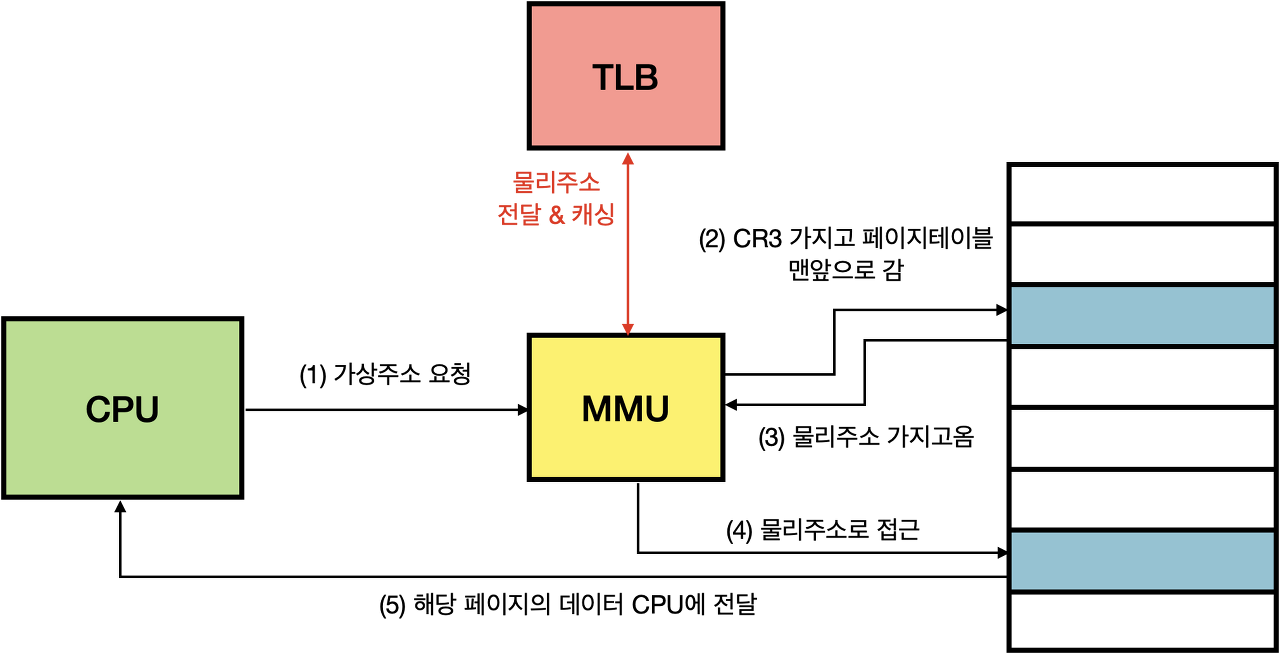

TLB, MMU, Page Table의 동작 과정

TLB가 없으면:

1) CPU의 가상 주소 요청

2) MMU가 CR3의 base 주소를 가지고 페이지테이블로 감 (물리 메모리 접근 1)

3) MMU가 물리 주소를 가지고 옴

4) MMU가 페이지의 물리 주소로 접근함 (물리 메모리 접근 2)

5) 해당 페이지의 데이터를 CPU에 전달

TLB 캐싱이 되어 있으면:

1) CPU의 가상 주소 요청

2) MMU가 TLB에서 캐싱된 물리 주소를 가지고 옴 (시간 세이브)

3) MMU가 페이지의 물리 주소로 접근함 (물리 메모리 접근 1)

4) 해당 페이지의 데이터를 CPU에 전달

64bit 다중 단계 페이징

리눅스는 4단계 페이징 기법을 사용한다. 64비트 선형 주소를 사용하면서 32비트 선형 주소보다 주소 공간이 훨씬 커져 페이지 테이블이 차지하는 용량을 줄이기 위해 4단계로 나누어 페이징한다. 64비트 선형 주소를 4부분으로 나누어 아래 디렉토리를 구성한다.

페이징 유닛은 PGD, PMD, PTE, offset으로 나뉜다.