기술의 변화

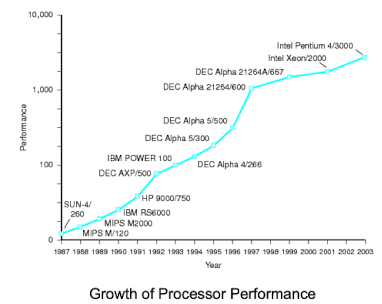

기술은 매우 급속하게 성장해왔다.

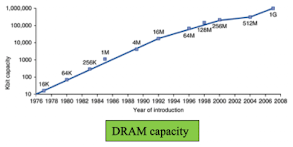

1965년 Moore's 법칙은 2년마다 다음과 같은 성장을 예측했다.

- Memory의 capacity가 2배

- Processors 속도는 1.5배

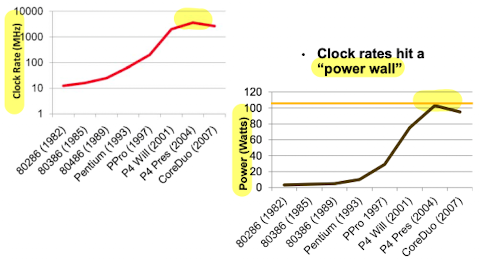

하지만 그 예상과 다르게 Power wall이라는 문제에 부딪히게 된다.

실제로 2002년부터는 desktop에서의 프로그램의 response time 향상율이 연간 1.5배에서 1.2배로 감소했다.

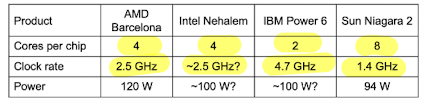

이 문제에 대한 도전은 microprocessors들의 설계를 바꾸게 하였다. 2006년 부터는 server와 desktop에서 microprocessors들이 multiple processors(cores per chip)로 전환하기 시작했다.

Power의 변화

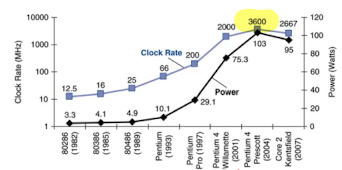

'Power Wall'는 Clock rate이 높아짐에 따라 증가해 왔으며 그에 따라 높아진 Power의 한계점을 의미한다.

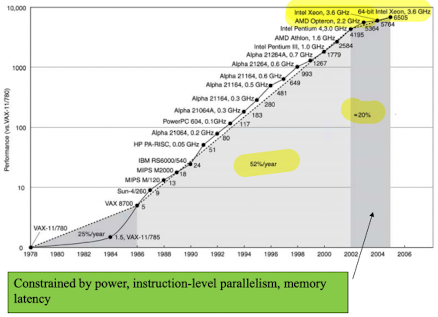

다음 두번째 사진은 uniprocessor의 성능 성장율의 감소를 보이며 성능향상을 위해 이제는 instruction-level 병렬화, memory latency 등을 개선하기 시작한다.

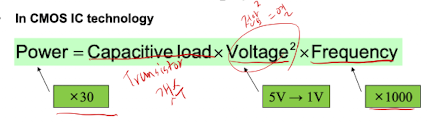

Power는 다음과 같이 계산한다. Transistor의 개수, Voltage, Clock rate이 증가함에 따라 Power가 높아짐을 알 수 있다.

여기에서 아까 말한 'Power Wall'의 문제는 우리는 더이상 Voltage와 Heat를 감소시키기 어려워지게 된 것이다.

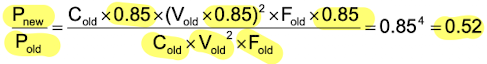

공식을 적용해보자. 새로 개발한 CPU의 스펙이 다음과 같을때 이전 CPU 보다 얼마나 Power가 개선되는지 계산해보자.

- 새로운 CPU는 이전보다 85%의 capacity load를 가짐

- 새로운 CPU는 이전보다 15%의 voltage 다운과 15%의 frequency 다운을 가짐

새로운 Power는 기존 Power의 0.52배, 즉 48%가 감소 되었다.

Multiprocessors 의 등장

chip 하나에 한개 이상의 processors가 들어가게 된다.

그에 따라 하드웨어는 여러개의 instructions를 한번에 처리하게 되었고 instruction level parllelism라는 개념이 생겼다. 이는 개발자들에게는 감춰져 있고 하드웨어 설계자들의 일이다.

하지만 parallel programming은 개발자들의 새로운 숙제가 되었다. 이때부터는 performance에 programming의 방법에 따라 달라지게 되었다. load balancing을 어떻게 해야하는가 synchronization과 communication은 어떻게 할것인가 등의 조정이 필요하게 되었다.

Cloud Computing

요즘은 모르는 사람이 없는 클라우드 컴퓨팅이다.

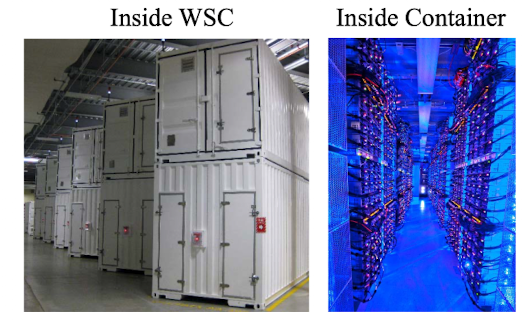

많은 유저가 웹, 앱을 이용하게 되면서 거대한 규모의 컴퓨터와 네트워크 대역폭을 요구하게 됬고 원격 컴퓨터의 발전이 이뤄졌다.

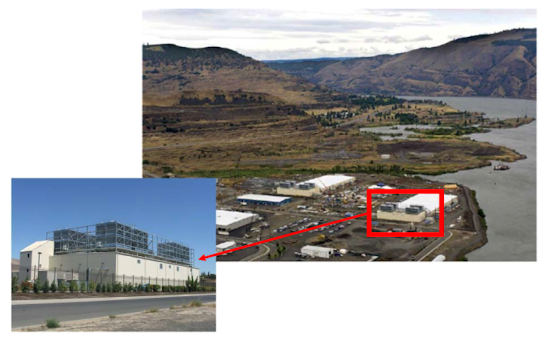

다음은 구글 데이터센터와 그 내부의 사진이다.

출처: [Computer Organization And Design: The Hardware/Software Interface]