Computer 기초 - CPU Clock & Memory Flip-Flop

1. 클럭(Clock)과 주파수

1.1 클럭이란?

클럭(Clock)은 컴퓨터가 작업을 수행할 때, 일정한 주기로 신호를 보내 연산의 타이밍을 맞추는 역할을 합니다.

- 이 신호는 발진기(Oscillator)라는 회로를 통해 생성되며, 정사각파나 사인파와 같은 주기적인 파형으로 나타납니다.

- 발진기(Oscillator): 주기적으로 반복되는 파형을 생성하는 전자 회로로, 클럭 신호의 원천이 됩니다.

1.2 클럭의 주기와 주파수

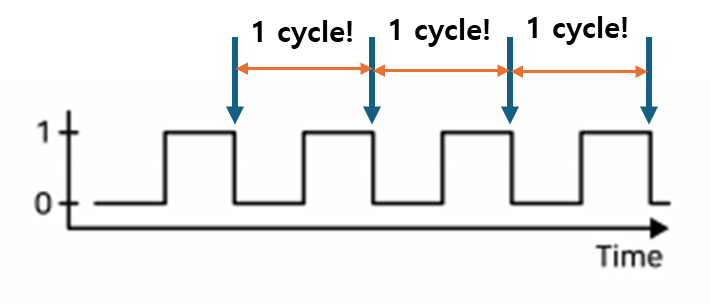

클럭 신호는 주기와 주파수라는 두 가지 주요 속성으로 설명됩니다.

- 주기(Cycle): 한 사이클이 완료되기까지 걸리는 시간입니다.

- 클럭 주기는 CPU의 연산 속도를 결정하는 중요한 요소입니다.

- 주파수(Frequency): 1초 동안 발생하는 클럭 사이클 수로, 단위는 헤르츠(Hz)를 사용합니다.

- 주파수는 주기의 역수로 정의되며, 예를 들어 주기가

0.05초인 경우 주파수는20Hz입니다.

- 주파수는 주기의 역수로 정의되며, 예를 들어 주기가

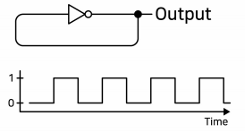

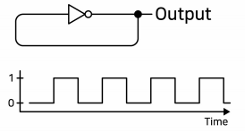

클럭 신호의 상태 변화와 NOT 게이트

클럭 신호는 주기적으로 0에서 1로, 또는 1에서 0으로 전환되면서 CPU의 연산 타이밍을 조정합니다. 이 과정에서 NOT 게이트를 사용하여 클럭 신호를 반전시키기도 합니다.

- NOT 게이트 활용: 클럭 신호를 반전시키면 Positive Edge Triggered (0에서 1로 변할 때 작동)와 Negative Edge Triggered (1에서 0으로 변할 때 작동) 신호를 조정할 수 있습니다.

이렇게 클럭 신호의 상태 변화를 활용하여, CPU는 일정한 타이밍에 맞춰 데이터를 처리하거나 명령을 수행하게 됩니다.

1.3 CPU 클럭 속도의 예시 (GHz)

현대 CPU의 클럭 속도는 보통 기가헤르츠(GHz) 단위로 측정됩니다. 예를 들어, 3.5GHz의 클럭 속도는 초당 35억 개의 사이클을 의미합니다.

- 1GHz = 10억 사이클/초

- 3.5GHz = 35억 사이클/초

1 G (기가) = (대략 1000) M (메가) = 약 1_000_000 K(키로) = 약 1_000_000_000 (약 10억)

주파수가 높을수록 CPU는 더 많은 명령을 더 짧은 시간 내에 처리할 수 있어, 일반적으로 더 빠르게 작동합니다.

- 다만, 클럭 속도만으로 CPU의 성능을 전부 설명할 수는 없으며, 코어 수나 설계 구조도 성능에 영향을 미칩니다.

- 예를 들어, 두 CPU가 동일한

3GHz의 클럭 속도를 갖더라도, 하나가 더 높은 코어 수를 가지고 있다면 더 많은 작업을 동시에 처리할 수 있어 성능이 더 우수할 수 있습니다.

2. 플립플롭(Flip-Flop): 데이터를 저장하는 기본 회로

2.1 플립플롭의 개념

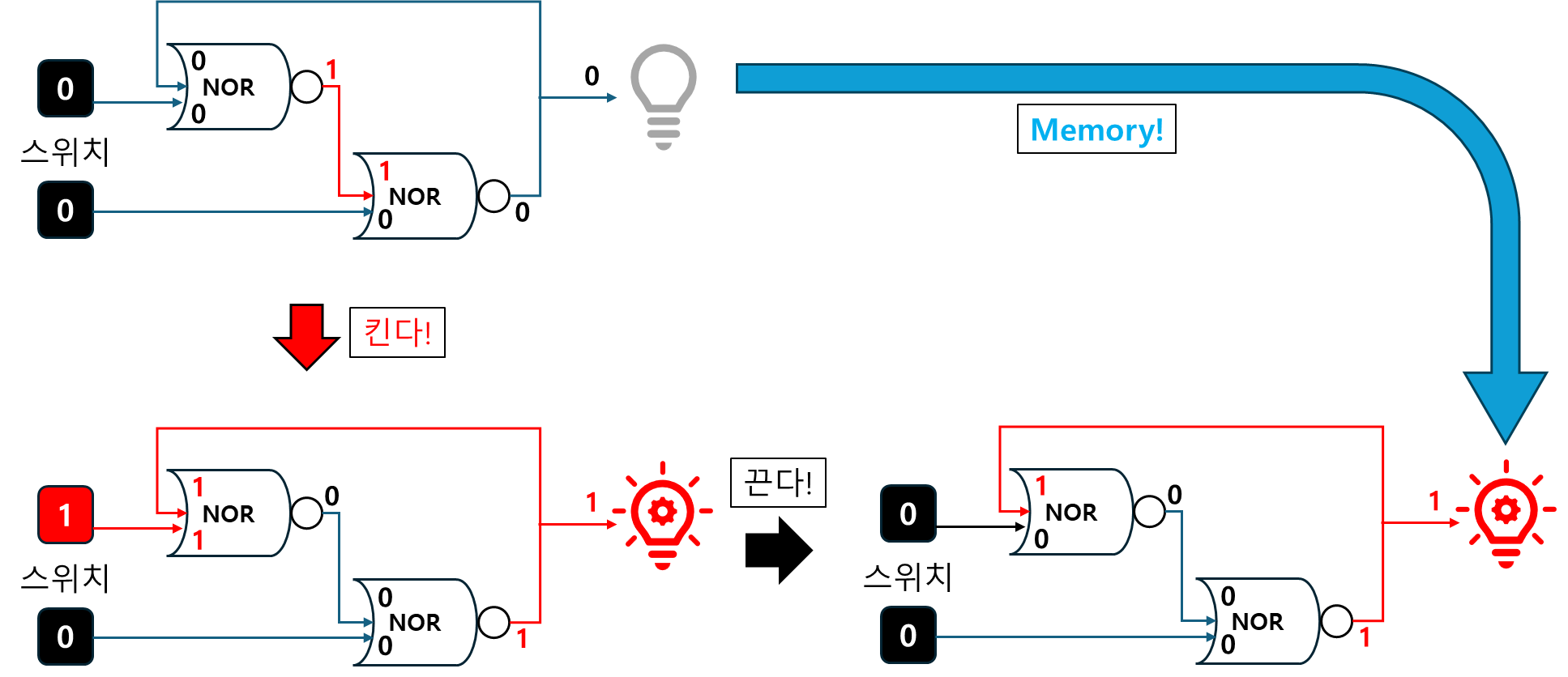

플립플롭(Flip-Flop)은 컴퓨터에서 데이터를 저장하기 위해 사용되는 기본 조합 논리회로입니다. 스위치와 같은 원리로, 특정 신호에 따라 데이터를 저장하거나 삭제할 수 있습니다.

- 기억 기능: 스위치를 켜고 끄는 동작을 저장할 수 있습니다.

- 예를 들어, 스위치를 켜면 불이 켜진 상태가 유지되고, 스위치를 끄면 불이 꺼진 상태가 유지됩니다.- 불 켜짐 = 저장된 데이터

1 - 불 꺼짐 = 저장된 데이터

0

- 불 켜짐 = 저장된 데이터

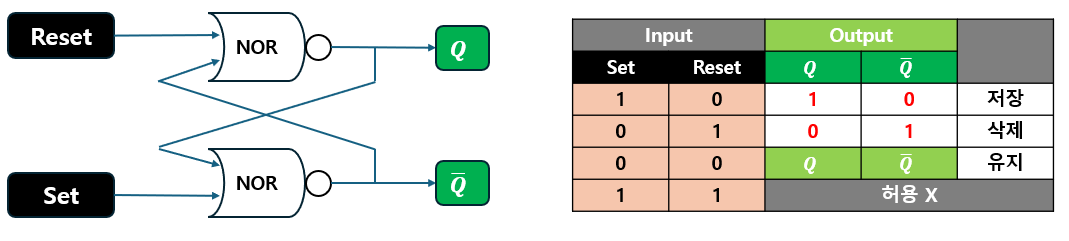

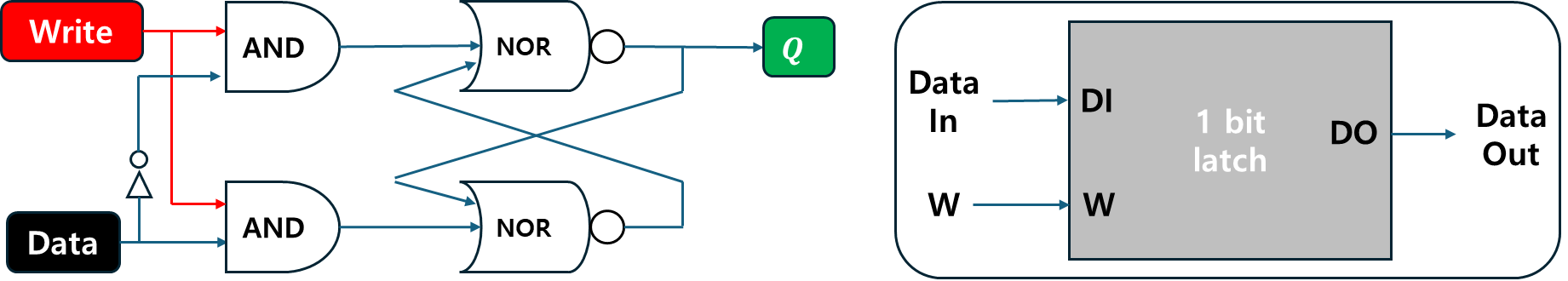

2.2 RS 플립플롭 (Reset-Set Flip-Flop)

RS 플립플롭은 Reset과 Set이라는 두 개의 입력 신호를 사용하여 데이터를 저장합니다.

- R(Reset): 출력(Q)을

0으로 설정 - S(Set): 출력(Q)을

1로 설정

특이사항:

- R과 S가 동시에 1이 되는 경우는 피해야 합니다.

- 이 경우 출력이 정의되지 않는 불안정 상태에 놓일 수 있어, 회로의 예상치 못한 동작을 유발할 수 있습니다.

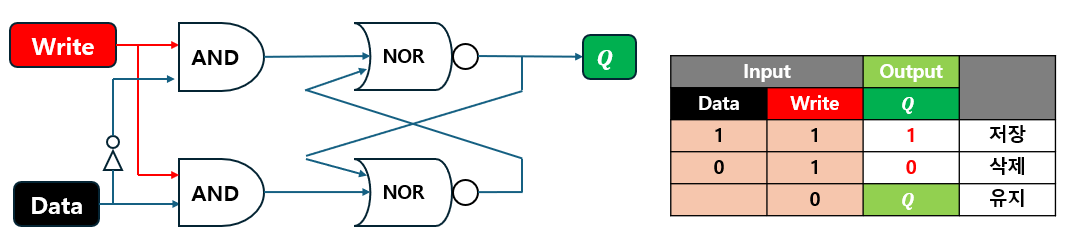

2.3 D 플립플롭 (D-Type Flip-Flop)

D 플립플롭은 단일 입력(Data) 신호로 동작하며, 주로 Level-Triggered 방식으로 작동합니다.

- 클럭 신호를 이용해 데이터가 일정한 타이밍에 저장되도록 제어하여, 데이터 입력이 특정 시점에만 이루어지게 합니다.

- Level-Triggered: 클럭이 특정 레벨(예:

1)에 있는 동안 데이터 입력을 허용하는 방식입니다.- 반면 Edge-Triggered 방식은 클럭이 상승 또는 하강하는 순간에만 데이터를 반영합니다.

- 특징:

D 플립플롭은RS 플립플롭의 불안정 상태를 피하고, 하나의 입력에 따라 출력(Q)이 결정되도록 설계되었습니다.

3. 래치 (Latch)와 셀렉터 (Selector)

3.1 1비트 래치 (1-Bit Latch)

1비트 래치는 단일 비트의 데이터를 임시로 저장할 수 있는 가장 기본적인 저장 장치입니다.

D 플립플롭(D-Type Flip-Flop)을 기반으로 구성되며, 주로 레벨 트리거(Level-Triggered) 방식으로 동작합니다.

- Write 신호가

1일 때 데이터가 래치에 저장되고, Write 신호가0일 때는 데이터가 유지됩니다. - 1비트 래치는 기본적으로 단일 비트 상태(0 또는 1)를 유지하는 용도로 사용됩니다.

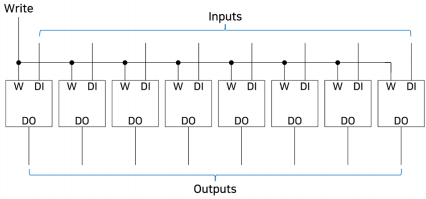

3.2 8비트 래치 (8-Bit Latch)

8비트 래치는 8개의 1비트 래치를 병렬로 연결하여, 8비트(1바이트) 데이터를 동시에 저장할 수 있는 구조입니다. 이는 기본적인 메모리 저장 단위로서 중요한 역할을 합니다.

- Write 신호가 1일 때, 8비트 데이터가 래치에 저장됩니다.

- 각 비트는 별도의 1비트 래치에 저장되며, 클럭이나 Write 신호가 들어올 때만 새로운 데이터로 업데이트됩니다.

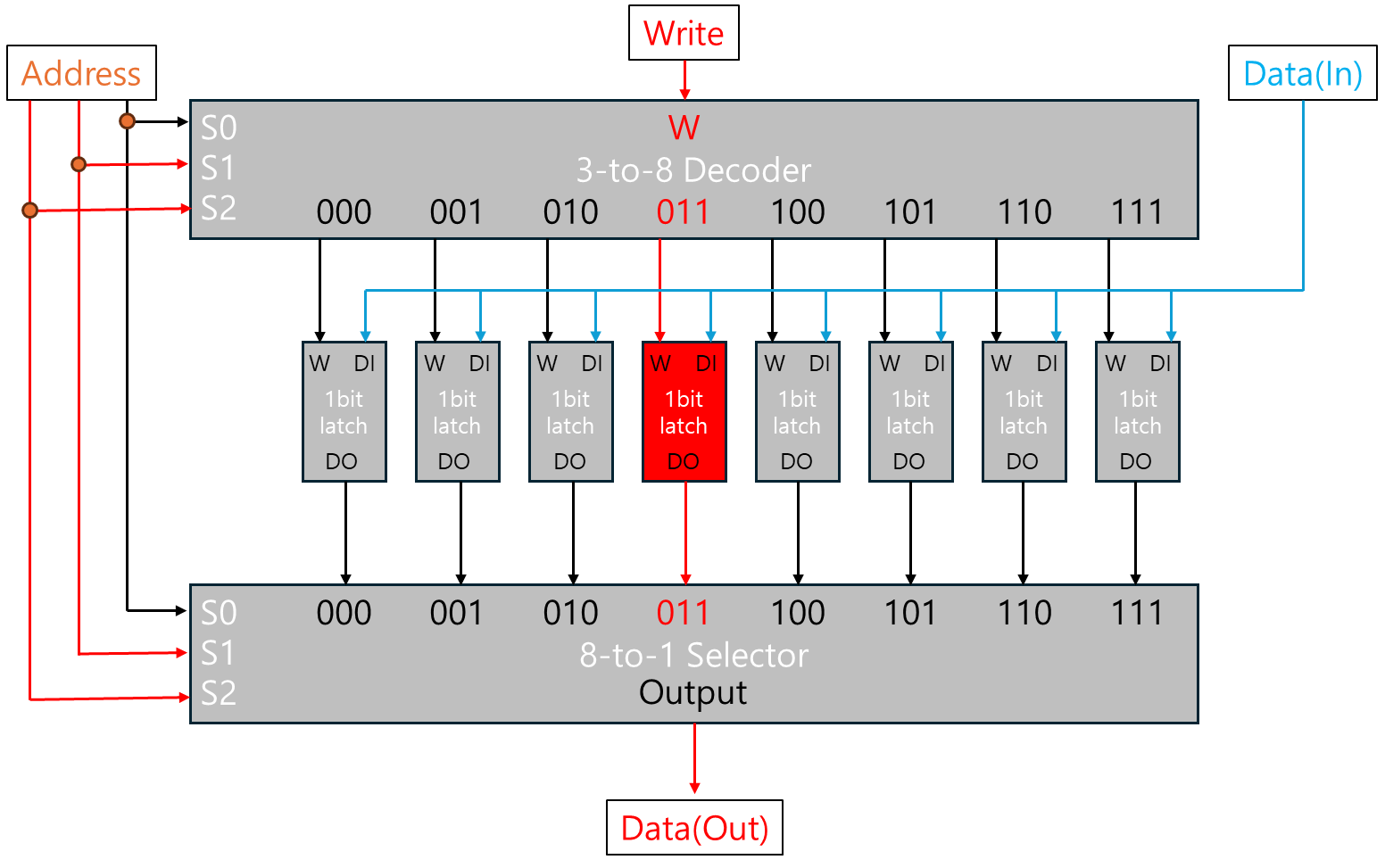

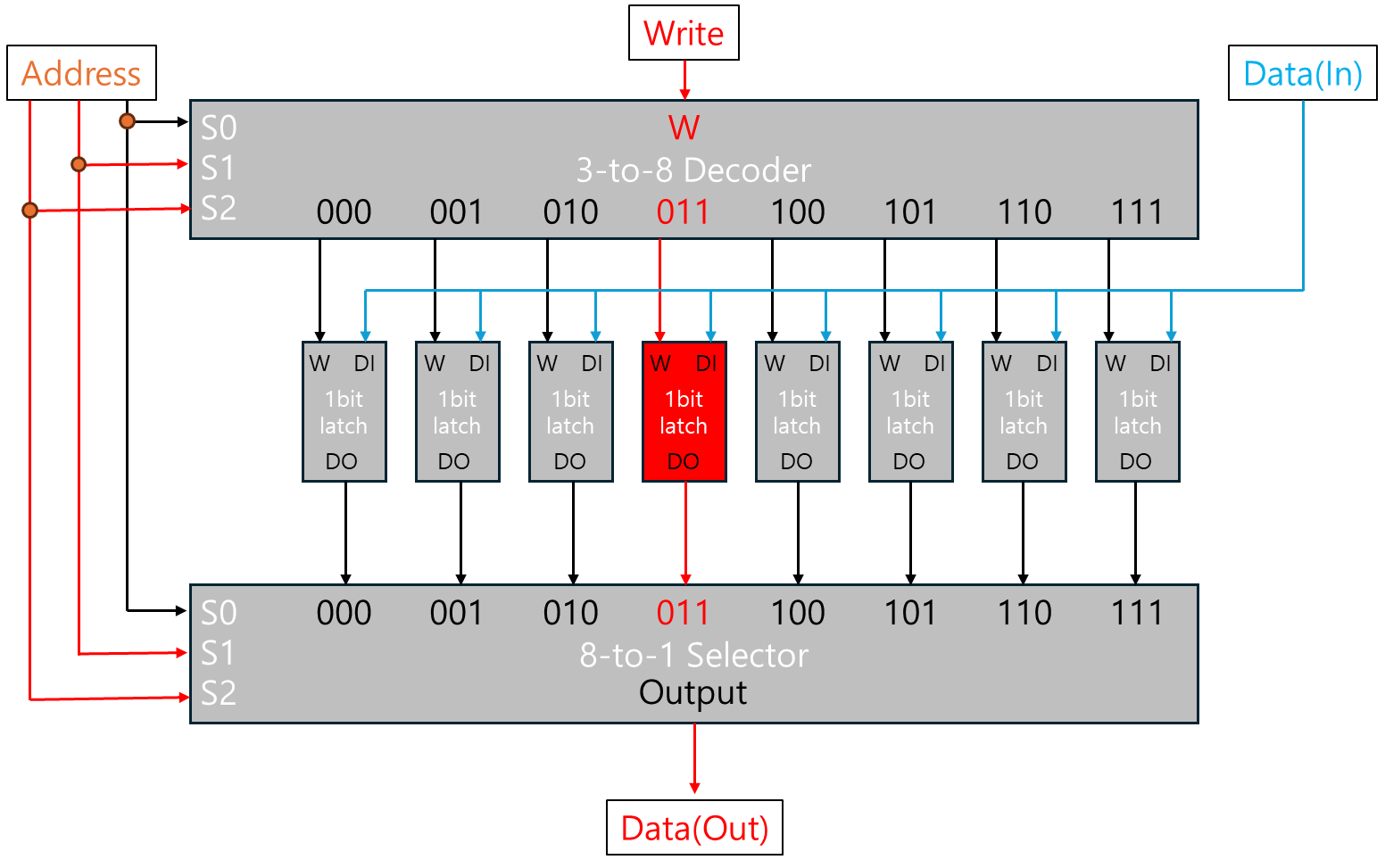

3.3 셀렉터와 디코더

셀렉터(Selector)와 디코더(Decoder)는 메모리와 같은 저장 장치에서 특정 데이터를 선택하거나 관리하는 데 사용됩니다.

- 셀렉터(Selector): 여러 개의 입력 중에서 하나의 입력을 선택하여 출력하는 회로입니다.

- 예를 들어, 8-to-1 셀렉터는 8개의 입력 중 하나를 선택하여 출력할 수 있습니다.

- 디코더(Decoder): 특정 주소나 명령에 따라 활성화할 출력을 결정하는 회로입니다.

- 3-to-8 디코더는 3개의 비트 입력으로 8개의 출력 중 하나를 선택할 수 있습니다.

디코더와 셀렉터는 래치나 RAM 같은 메모리 구조에서 데이터를 읽고 쓰는 데 필수적인 역할을 합니다.

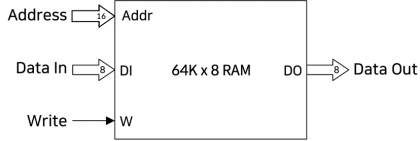

4. RAM (Random Access Memory)과 메모리 Array

4.1 RAM의 구조

RAM (Random Access Memory)은 데이터를 읽고 쓰는 데 사용하는 임시 저장 공간으로, 컴퓨터의 주 기억장치입니다. RAM은 데이터를 자유롭게 읽고 쓸 수 있는 임의 접근(Random Access) 방식을 지원합니다.

- 구성 요소: RAM은 여러 개의 래치와 디코더, 셀렉터로 구성됩니다.

- 작동 방식: 디코더를 통해 주소(Address)가 지정되고, 해당 주소에 해당하는 래치가 활성화되어 데이터를 읽거나 씁니다.

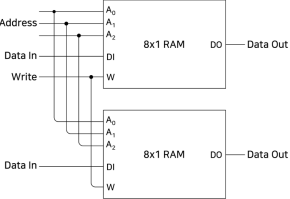

4.2 8 x 1 RAM과 RAM Array

8 x 1 RAM은 8개의 1비트 래치로 구성되어 있어, 8개의 단일 비트를 각각 개별적으로 읽고 쓸 수 있는 구조입니다.

- 데이터 입출력: 8개의 래치에 각각 1비트 데이터를 저장할 수 있으며, 각 비트는 별도의 주소로 접근할 수 있습니다.

- RAM Array: 여러 개의 8 x 1 RAM을 조합하여 더 큰 용량의 메모리를 구성할 수 있습니다.

- 예를 들어, 두 개의 8 x 1 RAM을 연결하여 8 x 2 RAM을 만들면, 각 주소에 2비트를 저장할 수 있습니다.

4.3 m x n RAM 어레이

m x n RAM 어레이는 m개의 주소와 n개의 데이터 비트로 구성된 RAM 구조입니다.

예를 들어, 8 x 8 RAM은 8개의 주소와 8비트 데이터 폭을 가지므로 총

64비트를 저장할 수 있습니다.

- RAM 확장: 더 큰 데이터를 저장하기 위해 RAM 어레이를 확장할 수 있습니다.

- 예를 들어, 1KB RAM은

1024개의 주소와8비트 데이터폭을 가지며, 이는 총 8192비트(1KB)의 데이터를 저장할 수 있음을 의미합니다.

- 예를 들어, 1KB RAM은

- m x n 구성의 유연성: RAM 어레이는 필요한 메모리 용량에 따라 다양한 m x n 구조로 확장할 수 있어, 컴퓨터 시스템의 메모리 요구에 맞춰 설계될 수 있습니다.

예시: 64KB RAM은

65536개의 주소(2^16)와8비트의 데이터를 저장할 수 있어, 총 512KB의 메모리 용량을 제공합니다.

마무리

이번 포스팅에서는 CPU 클럭과 메모리 플립플롭의 기본 개념부터 시작하여 래치, 셀렉터, RAM의 구조와 동작 방식까지 살펴보았습니다. 이러한 기본 개념은 컴퓨터가 데이터를 저장하고 처리하는 방식을 이해하는 데 중요한 기초가 됩니다.

특히, RAM의 구조와 메모리 어레이 확장 방식을 통해 컴퓨터가 어떻게 데이터를 저장하고 접근하는지 살펴보았으며, 디지털 회로에서 클럭 신호와 플립플롭이 시간을 맞추어 데이터의 신뢰성을 유지하는 데 중요한 역할을 한다는 점을 다루었습니다.

다음 포스팅에서는 Accumulator(누산기)와 레지스터의 역할을 중심으로, 컴퓨터의 내부 구조가 프로그래밍과 어떻게 연결되는지 다뤄보겠습니다.