- 곱의합 합의곱 연습 (SOP, POS, 진리표, 회로의 관계)

SOP → and, or logic으로 구현됨

POS→ or, and logic으로 구현됨

부울 덧셈

부울 곱셈

진리표를 통해서 알 수 있는 것

- 카르노 맵 연습 (카르노 맵을 이용한 논리 간소화)

2-변수 카르노 맵

3-변수 카르노 맵 → Gray Code임

4-변수 카르노 맵

직사각형으로 묶는다

직사각형의 크기는 최대로 크게 한다→1, 2, 4, 8, 16

SOP 항들을 합으로 묶어서 출력을 표현

무관 (don’t care) 조건→포함을 해도 좋고 포함하지 않아도 괜찮다

XOR function

5-변수 카르노 맵 → 어렵다..

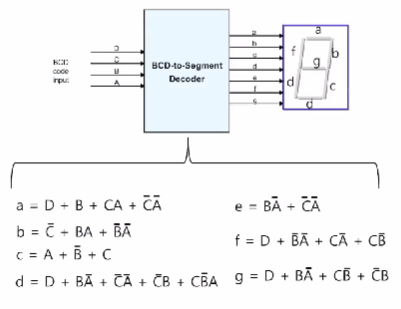

BCD to Segment Decoder → 만드는 방법, 어렵다..

- 조합논리회로 1 (가산기, 비교기, 인코더, 디코더)

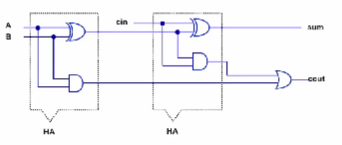

반가산기 (Half adder) → 2개의 1비트 sum = A xor B, carry = AB

전가산기 (Full adder) → 3개의 1비트 sum = A xor B xor cin, carry out = AB + (A xor B) cin

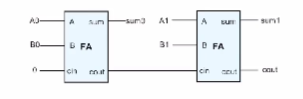

2bit 이진수 가산기 (Binary adder)

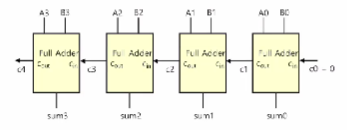

4bit 이진수 가산기 (Binary adder)

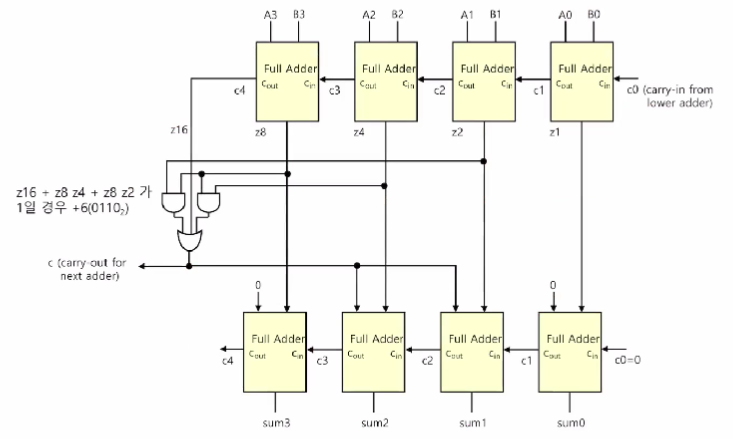

BCD 가산기

두 개의 BCD 수를 더하는 가산기→0-9, 10-19(+6)

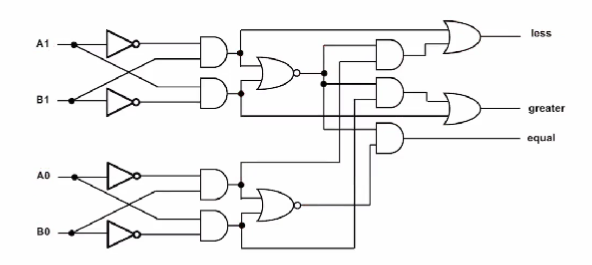

1-bit 비교기

equal = XONR

greater = A~B

less = ~AB

2-bit 비교기

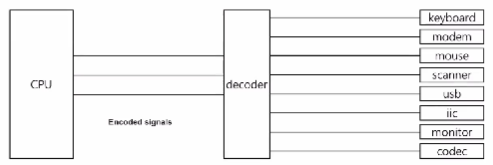

디코더

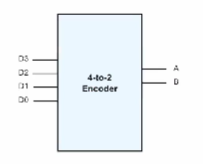

인코더

우선순위 인코더

- 조합논리회로 2 (먹스, 디먹스, 패리티, 코드 변환기)

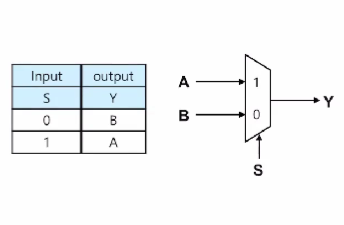

먹스 (Multiplexor)-Data selector

2-to-1 MUX

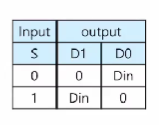

디먹스 (Demultiplexor)-Data distributor

1-to-2 DEMUX

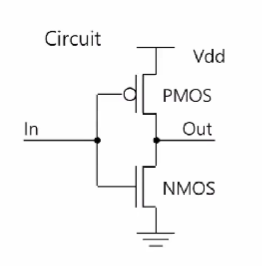

CMOS→NMOS, PMOS

CMOS 인버터→반전

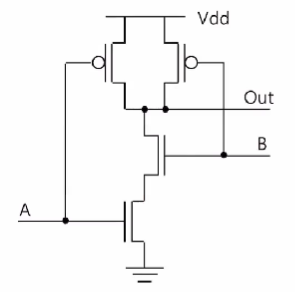

CMOS NAND 게이트

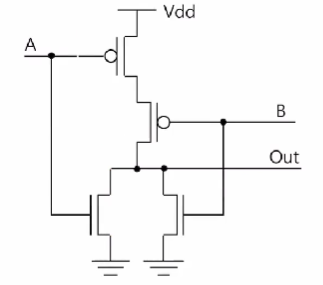

CMOS NOR 게이트

복합 게이트

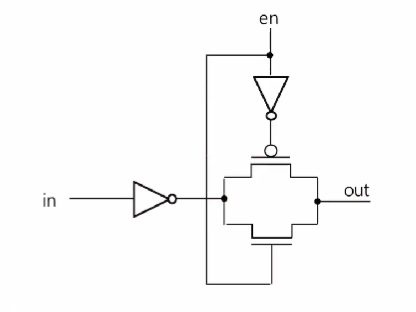

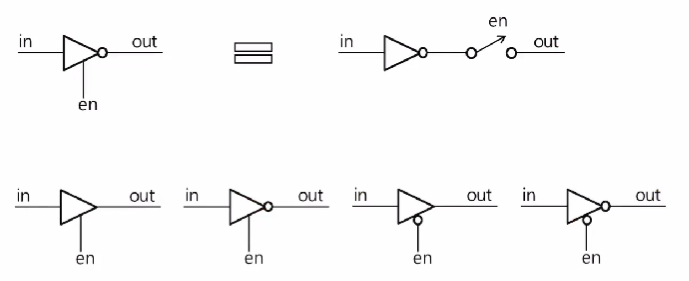

3상태 인버터

3상태 버퍼

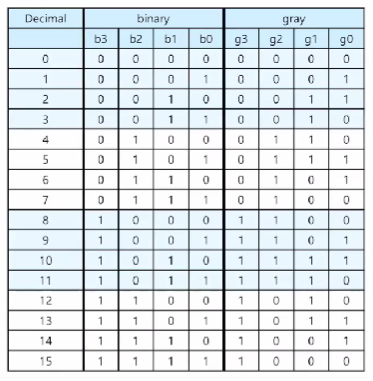

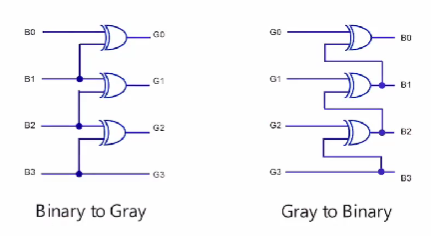

Gray code→하나의 비트만 변경되는 코드

3초과 코드→1의 보수를 쉽게 만들 수 있는 장점, 3을 더함

패리티→디지털 신호 전송 시의 오류를 체크

짝수 패리티, 홀수 패리티

패리티 발생기, 패리티 체크기

- 래치 (SR 래치, Gated 래치, D 래치)

조합회로→값을 저장 못함, adders, multiplexers, decoders, encoders, gates

순차회로→값을 저장, counter, register, clock divider, FSM

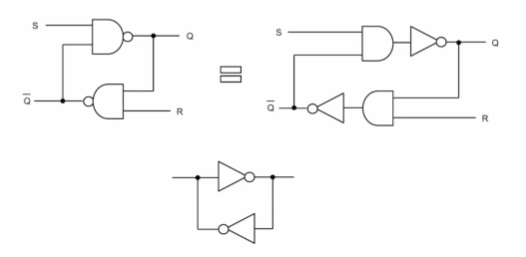

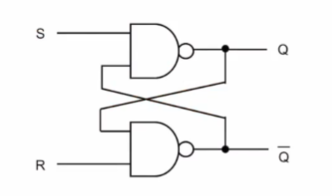

SR Latch

Set→S가 0일 때 1로

Reset→R이 0일 때 0으로

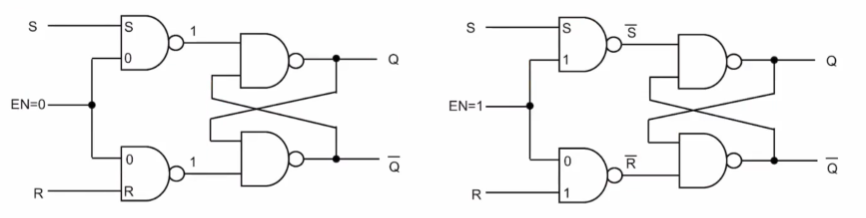

Gated SR Latch

EN=0 유지, EN=1 SR의 반전으로 계산

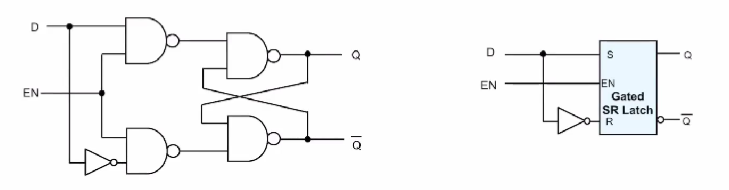

D Latch

허용되지 않는 값이 없다

EN=0 유지, EN=1 D로 계산

Cross-coupled inverter