- 플립플롭 (D 플립플롭, JK 플립플롭, T 플립플롭)

Clock 신호 → 주기적인 Square wave

Flip Flop → Clock 신호가 변화하는 시점인 edge(엣지)에 맞추어 동작

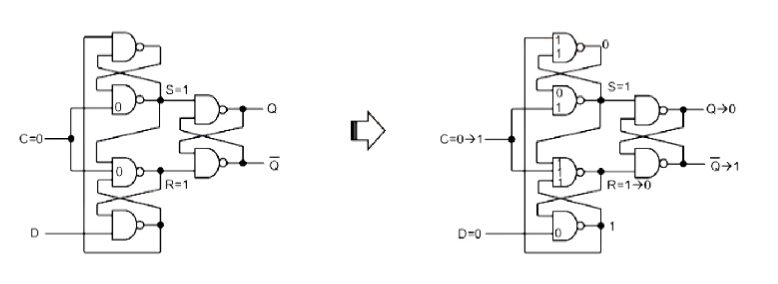

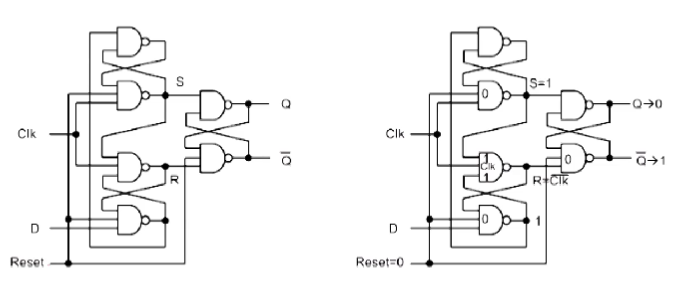

Classical D F/F → C이 0이거나 1일 때⇒유지, C이 0에서 1일 때→ D=0⇒reset, D=1⇒set

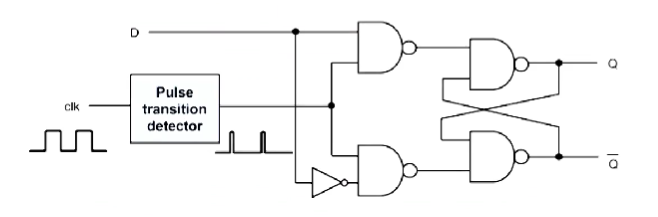

Edge-triggered D F/F → Pulse transition detector + D Latch

SR F/F

Set→S가 0일 때 1로

Reset→R이 0일 때 0으로

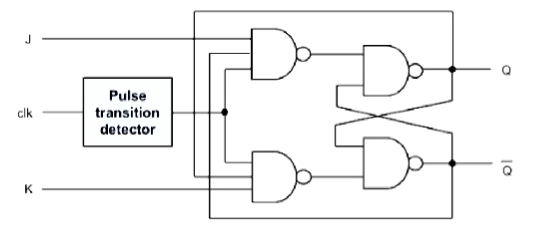

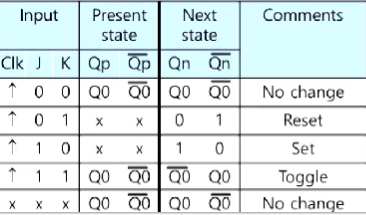

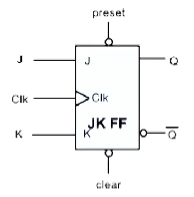

JK F/F

00 유지, 01 0, 10 1, 11 반전

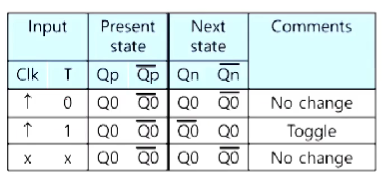

T F/F

1일 때 반전

비동기→클럭 신호와 상관없이 값이 변할 경우

비동기 리셋 D F/F → reset=0이면 무조건 0

비동기 셋 리셋 JK F/F → preset 0→set, clear 0→reset

전달 지연 시간

셋업과 홀드 타임

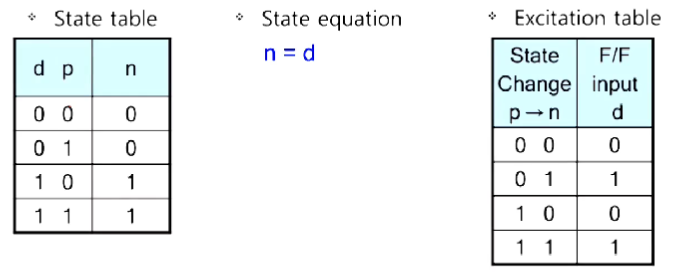

State table(상태표) & Excitation table(여기표)

- FSM 예제 (FSM의 다양한 구현 방법 예제)

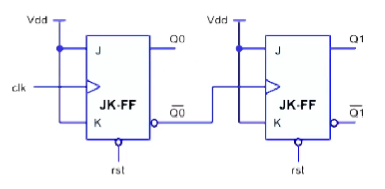

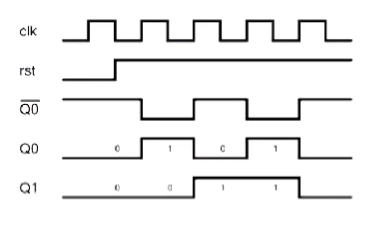

비동기 2비트 카운터→00 01 10 11 00 반복

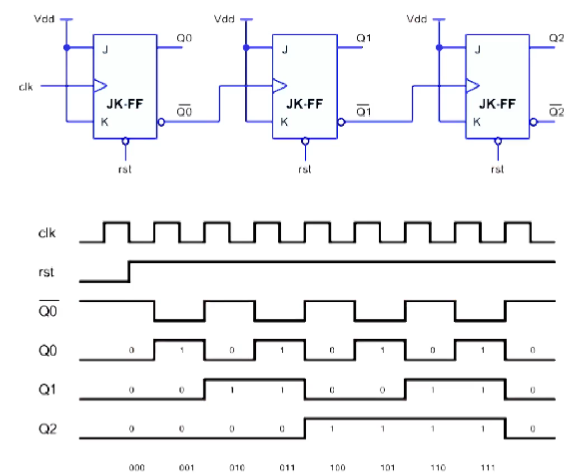

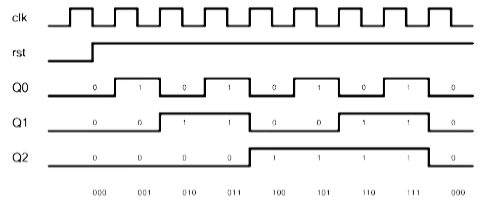

비동기 3비트 카운터→000 001 010 011 100 101 110 111

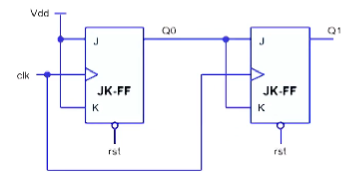

동기 2비트 카운터

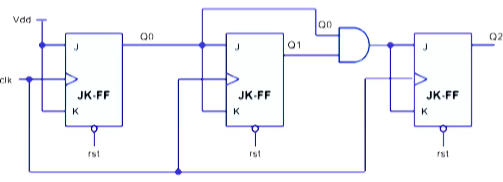

동기 3비트 카운터

순차회로

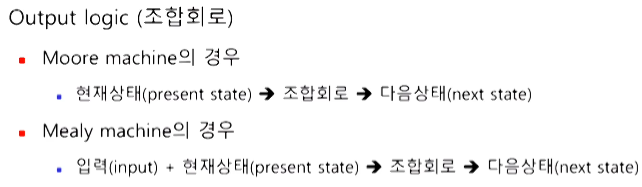

FSM → 한정된 상태를 갖는 머신→Counter, Clock divider, FSM

Register → 플립플롭이 여러개 모인 것→Shift register, Parallel register

- 카운터 예제 (카운터의 다양한 설계 예제)

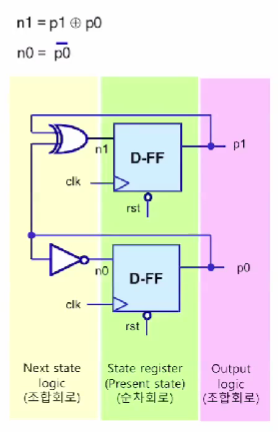

2비트 동기 카운터의 설계 (D F/F)

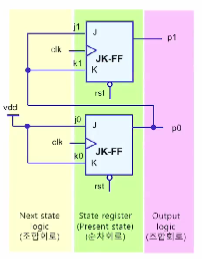

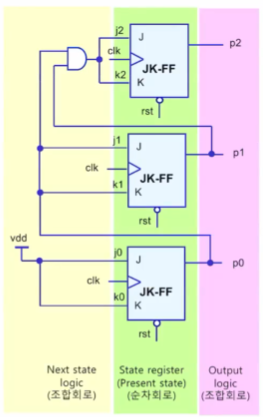

2비트 동기 카운터의 설계 (JK F/F)

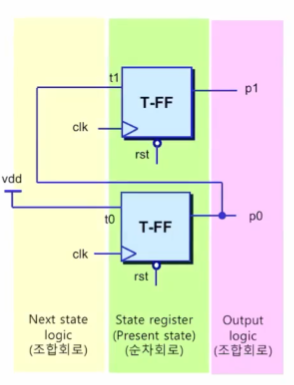

2비트 동기 카운터의 설계 (T F/F)

3비트 동기 카운터의 설계 (D F/F)

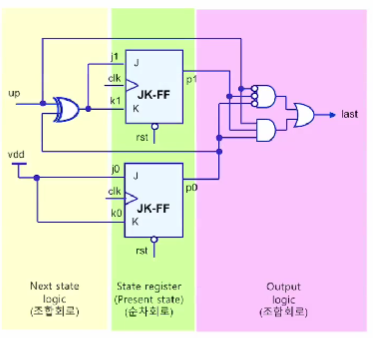

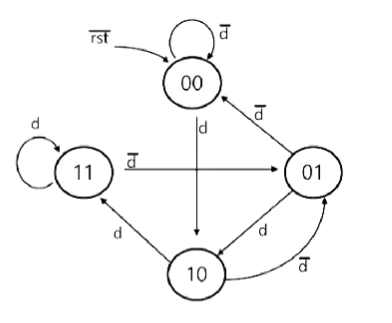

2비트 up/down 카운터의 설계

- FSM 응용 (FSM을 이용한 설계 예제)

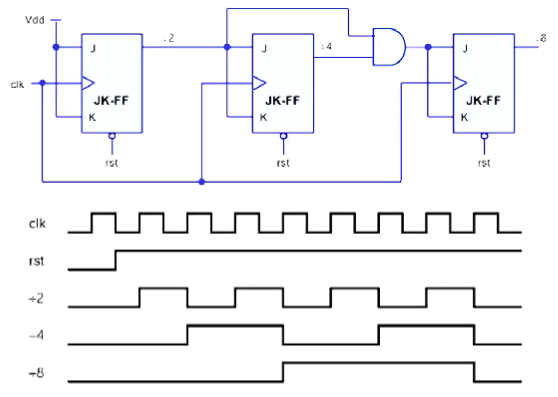

Clock divider, Clock multiplier

Shift register

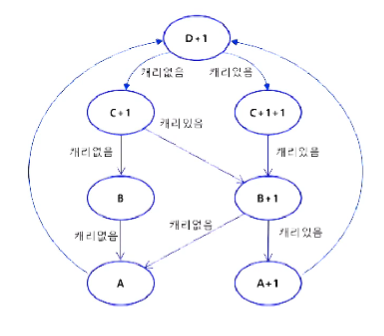

Excess-3 code → BCD에 0011을 더하여 생성

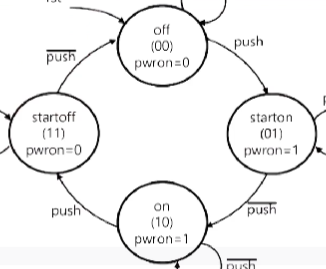

누름 전원 스위치

startoff →off → starton → on