🌱 들어가기

ARM = Advanced RISC Machine = 진보된 RISC의 기기

RISC (Reduced Instruction Set Computer) 프로세서란 ?

- CISC에서 간략화 된 소수의 명령어들만 지원하는 새로운 CPU 구조의 도입

- 고정된 길이의 명령어와 제한된 개수의 명령어를 지원해 단순한 명령어를 빠르게 수행하는 구조

- 많은 수의 레지스터를 사용해 메모리 접근을 줄이고, 주기억장치 접근을 최소화하는 구조

| 구분 | RISC | CISC |

|---|---|---|

| 명령어 형식 | 고정 | 가변 |

| 명령어 종류 | 적음 | 많음 |

| 명령어 길이 | 고정 | 가변 |

| 적재/저장 구조 | 사용 | 미사용 |

| 주소 지정 방식 | 단순하고 소수 | 복잡하고 다수 |

| 회로 구성 | 단순 | 복잡 |

| 장점 | 구현용이, 파이프라이닝에 효율적 적용 | 호환성 양호, 코드 밀도 양호 |

| 예 | ARM, PowerPC, MIPS | Intel x86, DEC VAX 11/780 |

1983년 Arcon사에서 Berkley RISC-I를 변형하여 ARM CPU 개발

성능 보다는 제어 등의 산업용 특성에 맞게 속도와 비용을 중시하는 변형된 RISC 구조 (Exception 처리 강화, 소형화, 집적화, 저전력화에 집중)

ARM은 Core부분만 개발, 생산은 필요로 하는 업체가 자신들이 필요로 하는 주변장치 회로들을 내장시켜 1-chip 형태의 마이크로 컨트롤러를 생산

🫥 특징

-

단순화 설계를 통한 코어 최소화, 저전력용 구조 → Embedded System에 최적화

-

단순성이 강조된 변형된 RISC 구조

-가변 Cycle 명령어 존재(메모리 블록전송), Register Window를 줄인 Shadow Register사용 등

-

하위 명령어 구조를 유지하면서 발전 (ISA)

-

Pipeline

-

주소 공간 (주소 32비트, Memory-mapped I/O, 다양한 Addressing 모드)

-

레지스터 구성 (범용 레지스터 30개, PC 1개, CPSR 1개, SPSR 1개, Load-Store 구조)

-

프로세서 내부에 하드웨어 디버그 기술 포함

ARM 아키텍처, 코어, 프로세서

ARM 아키텍처 : 명령어, 레지스터 구조, 처리되는 데이터 크기 등과 같은 기본구성 및 동작 원리

ARM 코어 : ARM 아키텍처의 기본원리를 이용해 만든 프로세서 코어

ARM 프로세서 : ARM 코어에 주변회로를 포함하는 독립된 형태, 각 반도체 업체마다 생산하는 SoC

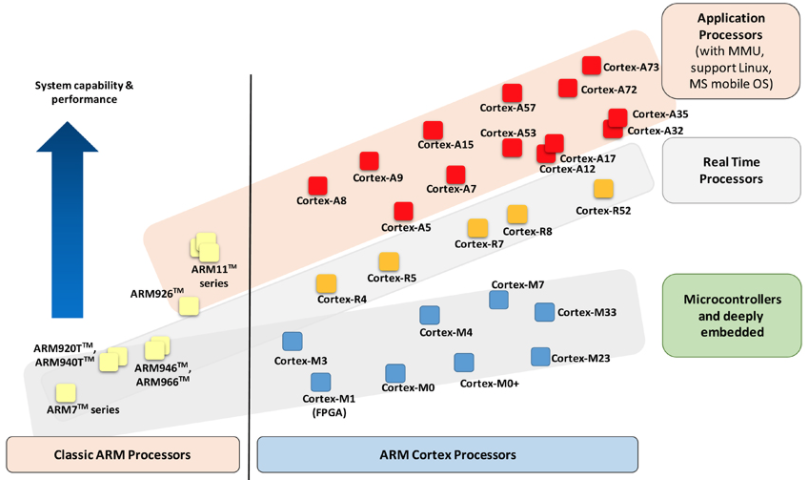

🏆 ARM 버전

⛑️ ARM 명령어 처리

-

ARM 명령어 분류

산술 명령어, 논리 명령어, 시프트 명령어, 비교 명령어, 이동 명령어, Load/Store 명령어, 분기 명령어

-

ARM 명령어 서식

데이터 처리 명령 형태

OP-code Rd,Rn,RxLoad/Store 명령 형태 (LDR, STR 명령어)

OP-code Rd,[Rn,Rx] -

ARM 명령어 처리 과정

FETCH → DECODE(Reg Select, Reg Read) → EXECUTE(Shift, ALU연산) → Memory → Write(Register Write)

-

ARM 모드 (32bit) 상세 명령어 형식

명령어 32비트 구성

→ Condition(4) + Opcode(8) + Destinaiton(4) + Source1(4) + Source2(12)

조건부 실행을 통해 분기 명령을 배제해서 파이프라인 기능을 최대화 한다

~~> 명령어가 줄고, CODE 축소 효과와 파이프라인 기능을 최대화 시킬 수 있다.