CPU의 언어,

CPU가 이해할 수 있는 명령어들의 모음,ISA(Instruction Set Architecture)

ISA가 다르다 -> 각 CPU마다 쓰이는 명령어가 다르다 -> 어셈블리어도 다르다

"아! 같은 소스코드로 만들어진 프로그램이라 할지라도 ISA가 다르면 명령어도, 어셈블리어도 달라지는구나!"

- CPU별 명령어들이 다르다

: 가장 대표적인 CPU 아키텍쳐인 x86, ARM, MIPS, RISC-V

(학교에선 RISC-V 구조만 오지게 판다...) - RISC-V Instruction Set은 다른 CPU들(x86, ARM, MIPS)에 비해서 효율적으로 설계되어 있다

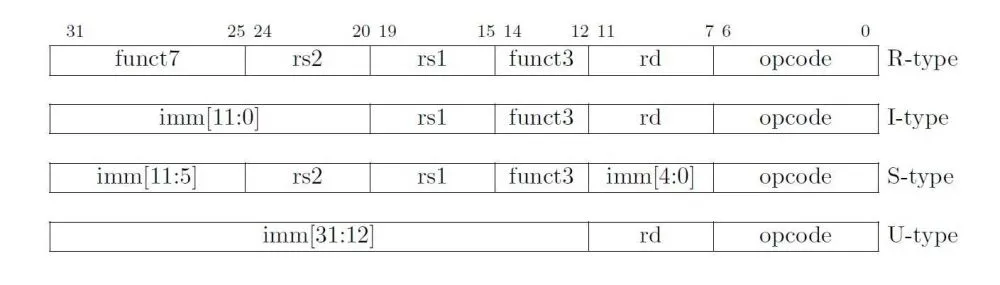

- opcode의 위치 : RISC-V는 최하위 비트에 배치됨 (MIPS는 최상위 비트에 배치)

-> 장점은?

: operand의 가변성과 호환성이 좋아짐.

(명령어 크기가 32비트에서 64비트, 128비트.. 증가해도 opcode의 위치는 변함이 없어서 Instruction Set 설계의 일관성을 유지)

RISC-V 의 ISA를 이해하기 위해서는 다음과 같은 개념들이 워밍업?!이 되시겠다..

Instruction set을 design 할 때 고려할 사항

- Operands를 어디에 저장할 것인가? - register, memory, stack, acc …

- Operands 몇 개까지 허용할 것인가? - 0, 1, 2 or 3

- Operands의 위치를 어떻게 나타낼 것인가? - Direct, Immediate, Indirect …

- Operands의 종류와 크기를 어디까지 지원할 것인가? - byte, int, float, double …

- 어떤 operation을 지원할 것인가? - add, sub, mul, div, mov, comp …

참고블로그

ISA Classification

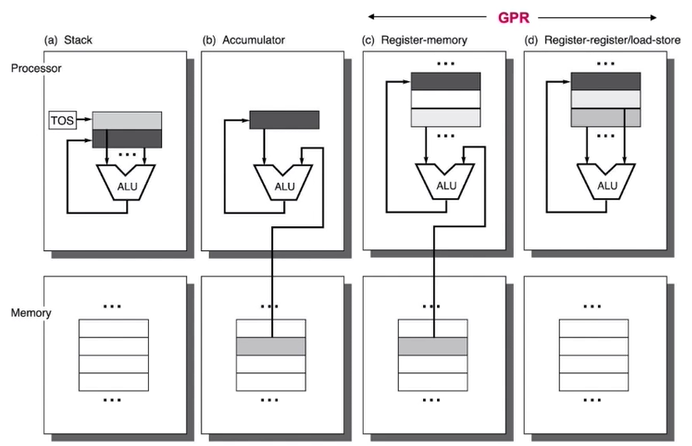

(1) Storing Operand

-

Stack Architecture

-

Accumulator Architecture

-

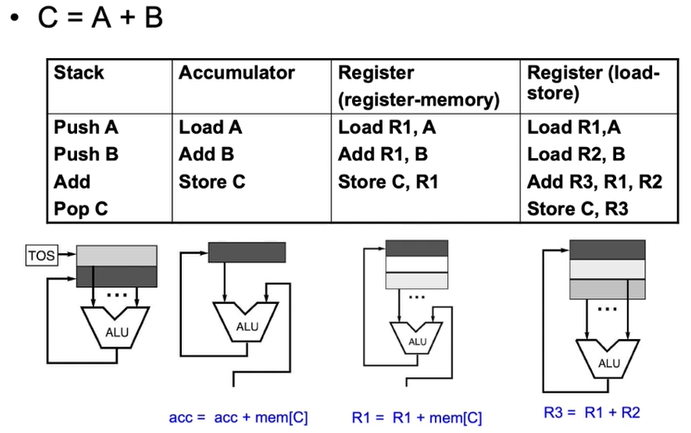

General-purpose register architecture

: only explict operands either registers or memory

- CPU 내부에 여러개의 register 를 둬서 저장공간 확보하겠다.

- 요즘은 전부 이거 사용

- 줄여서 GPR

add A, B

add A, B, C

load Ra Rb (Ra <- mem[Rb]) //레지스터에 저장! Ra는 rd

store Ra Rb (mem[Rb] <- Ra) //메모리에 저장! Ra는 src -

Memory-Memory Architectures

#of Registers -> ARM, MIPS 등 각 다른 종류의 CPU들마다 두는 레지스터들의 개수가 다르네.. 16,8,32...(ppt27 이미지)

(2) # of Operhands

- ALU : 실제 연산을 담당, 논리연산과 산술연산이 있음

-> 2 or 3 operands

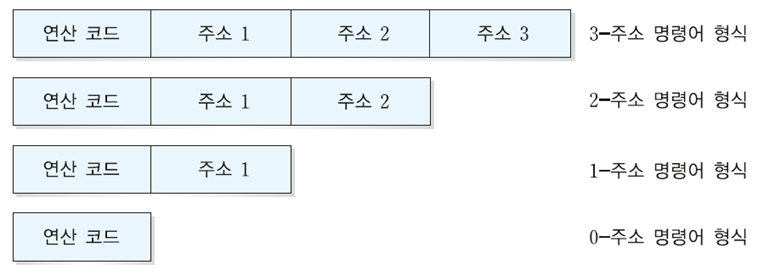

- 명령어 구조 = 연산 코드 + operands

여기서 operands 에는 주소, 수, 아스키코드, bit이나 flag같은 논리데이터가 저장될 수 있다. 이때, Operands가 주소를 나타내는 경우

-> operand의 개수에 따라 3,2,1,0 주소방식이 있다.

(3) Addressing Mode

Unit of Data

"1byte = 8bit"

1kB = 1000byte

1MB = 1000kB

1GB = 1000MB

1TB - 1000GB

"KB" 는 2^10byte일까? 10^3byte 일까?

여기서 혼동하지 말아야할것이 1024씩 묶어서 표현되는 단위는 KiB, MiB, GiB, TiB 으로 해야한다

"Word"

-프로세서가 한번에 처리할 수 있는 데이터의 크기

-The size of register in a processor(워드 크기 = 레지스터 크기)

-The largest possibe address size

-대부분 32bit 또는 64bit (근데 난 음.. 4byte(32bit)로 주로 봄,,, 컴망에서도 그렇고,,)

Byte Order (Endianness)

Little Endian 알아두자 : 큰 byte 일수록 큰 주소

"Little end goes first"

-> Intel, ARM, RISC-V

Type of Addressing Mode

여기에 그림이랑 설명잘되어있음

여러가지 있지만, 중요한 것만 정리(ppt 40 이미지 꼭 보기)

-

Register direct addressing mode

-

Immediate addresssing mode : 오퍼랜드에 필드에 연산에 사용할 데이터를 직접!

-

Displacement addressing mode

-

Register indirect addressing mode

(4) Type & Size of Operhands

Common operand types: (imply their sizes)

• Character (8 bits or 1 byte)Characters are almost always in ASCII

• Half word (16 bits or 2 bytes)

• Word (32 bits or 4 bytes)

• Double word (64 bits or 8 bytes)

• Single precision floating point (4 bytes or 1 word)

• Double precision floating point (8 bytes or 2 words)

(5) Type of Operations

1) Data transfer

: 데이터를 source에서 destination으로 옮기거나 복사

Load : 레지스터에 가져와

Store : 메모리에 저장

Move

2) Arithmetic and Logic (ALU)

: Operands 사이에서 특정 연산을 수행하고 destination에 저장

ADD

SUB

Shift

등등

3) Branch (or Control flow)

: 순차적인 흐름에서 벗어나서 다른 곳으로 분기할 때 사용다.

BEQ

…