RISC-V란, The Free and Open RISC Instruction Set Architecture - 나무위키

RISC-V 를 중점으로 컴퓨터구조를 한번 살펴봅시당!

RISC-V 특징

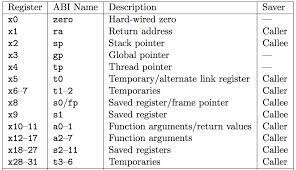

- 32개의 64-bit (2 WORD) register를 가지고 있다.

- 32 General Purpose Registers

- Register Size = 64bit

- 메모리랑 직접 연산 X

- Instruction Size = 32bit (기계어를 바꾸지 않겠다! 는 의지..)

Register

-

33개의 레지스터 : general purpose register(GPR) 32개 + special register인 PC 1개

-

0번 register는 항상 0으로 고정돼있다. (0이라는 상수를 만드는 데에 비효율적인 과정 필요)

-

Load-store architecture이다 -> register를 적극 활용해서 빠른 연산을 수행

Load-store architecture 란, 모든 연산을 최대한 register에서 해결하는 아키텍처

-

레지스터 직접 지정 가능하지만, 몇개의 레지스터들은 이미 규약으로 정해져있음

Operation

- ALU

- Data transfer

- Control (or Branch)

바로 전 블로그에서 이미 공부한 내용!!

[부록] : 2의 보수

모든 0과 1을 뒤집고, 1을 더해서 구한다.

(Negate all bits and add 1)

혹시 모르면 여기 참고

왜 알아야 하냐... 나중에 shift 명령어 이런거 할라면, 2의 보수를 알아야 이해함

음수를 어떻게 표현하냐? 2의 보수를 이용해 표현

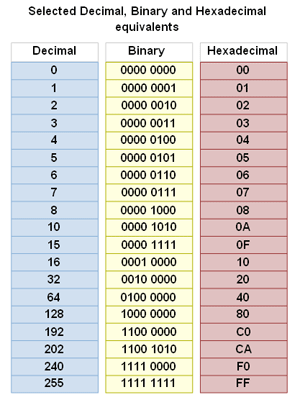

[추가] : 16진수 -> 2진수, 2진수 -> 16진수

이거 기본이다!

- 2진수로 변환 : 16진수 1글자 -> 4bit 간주

- 16진수로 변환 : 2진수를 4개씩 끊어서

16진수로

아래 표 외워야 한다

1~9 까지 + 그냥 A부터 10 이구나!! F는 15구나!! 기준