RISC vs CISC

Reduced Instruction Set Computer (RISC)

- Minimalism: Break down instructions into their fundamental/minimal pieces -> instruction 갯수 증가

- Load-store ISA: Easy to implement (빠른 클럭 속도)

- ARM, RISC-V, MIPS 등

Complex Instruction Set Computer (CISC)

- A movement to reduce 'sementic-gap' betwn 기계어와 고급언어

- (belief) space-efficiency 향상 (명령어 갯수가 적으니까)

- (belief) faster program (얘도 명령어 갯수가 적어서)

- x86, AMD64 등

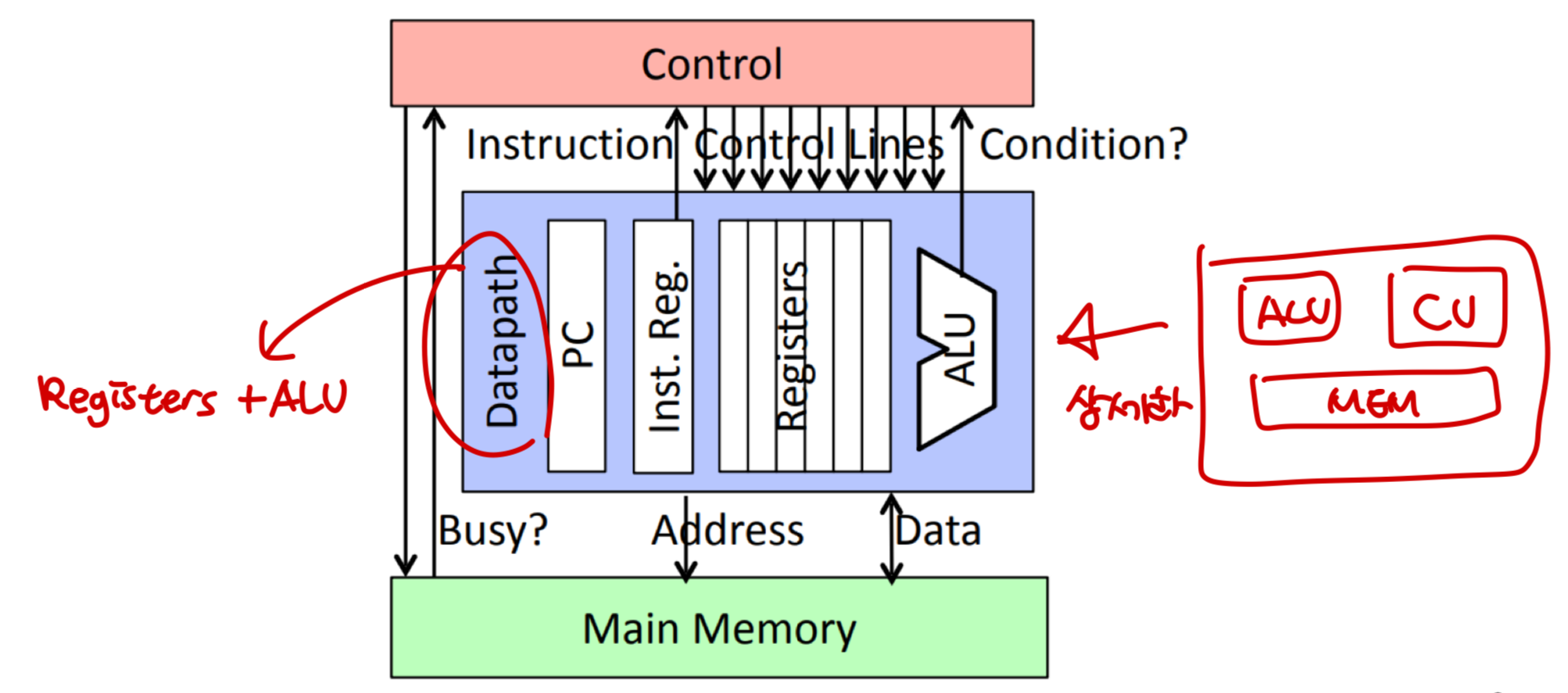

Control vs Datapath

- Datapath: 값이 (레지스터)에 저장되고 ALU에서 연산이 일어나는 곳

- Control: Datapath에서 일어나는 연산의 순서를 결정하는 곳

여기서 R-type register랑 I-type register이 무엇인가?!

바로 아래를 보장

Registers: Assembly Variables

다른 고오급 언어들과 비교하면, Assembly는 변수라는 개념보다는 조금 더 원시적이고 하드웨어에 가까운 Assembly operand, 즉 레지스터가 있다.

Registers

- 저장 가능한 데이터의 수와 용량이 제한되지만 하드웨어에 직접 저장하고, 속도가 메모리와 캐시에 비해서 정말정말 빠름

- 명령어에 x1, x2, x3 등 임시 레지스터는 변수 역할을 함.

- 고급 언어의 변수와 달리 데이터의 자료형이 따로 없다

결국 연산 수행 시 operator가 결정한다.

RISC-V의 경우, 32개의 레지스터 (128B)가 있다.

- x0: 0 고정, x0-31: 실제로 채워넣을 수 있는 4B의 공간

- 근데 왜 4B??!?! : RISC-V의 1 word는 4B이기 때문!

- 결국 Register size = Word length = 32 bits (4 Byte)가 됨

RISC-V Instruction Assembly Syntax

Instructions have opcode and operands!

e.g. add x1, x2, x3 (x1 = x2 + x3 와 동일)

- add: Operation code (opcode)

- x1: Destination register (저장 위치)

- x2, x3: First & Second operand register (피연산자)

Immediates

Immediates: 정수형 상수값

꽤나 자주 사용돼서, 상수값을 이용하기 위한 특별한 opcode가 있다.

e.g. Add immediate:

addi x3, x4, -10

이 I-type instruction의 역할은 add (R-type instruction)와 거의 동일한데, 유일한 차이점은 last argument가 레지스터가 아닌 상수라는 점이다. (add x3, x4, x0)

또 등장하는 바어메..

Byte-Addressable Memory

각각의 바이트가 자기만의 주소를 가지고 있다는 뜻.

RISC-V도 사실 byte-addressable이다. 바이트 단위로 접근이 가능하니까!

다만 한 번 불러들일 때는 word (RISC-V: 4B) 단위로 불러들인다.

그럼 여기에 문제가 생길 여지가 생긴다.. 바로

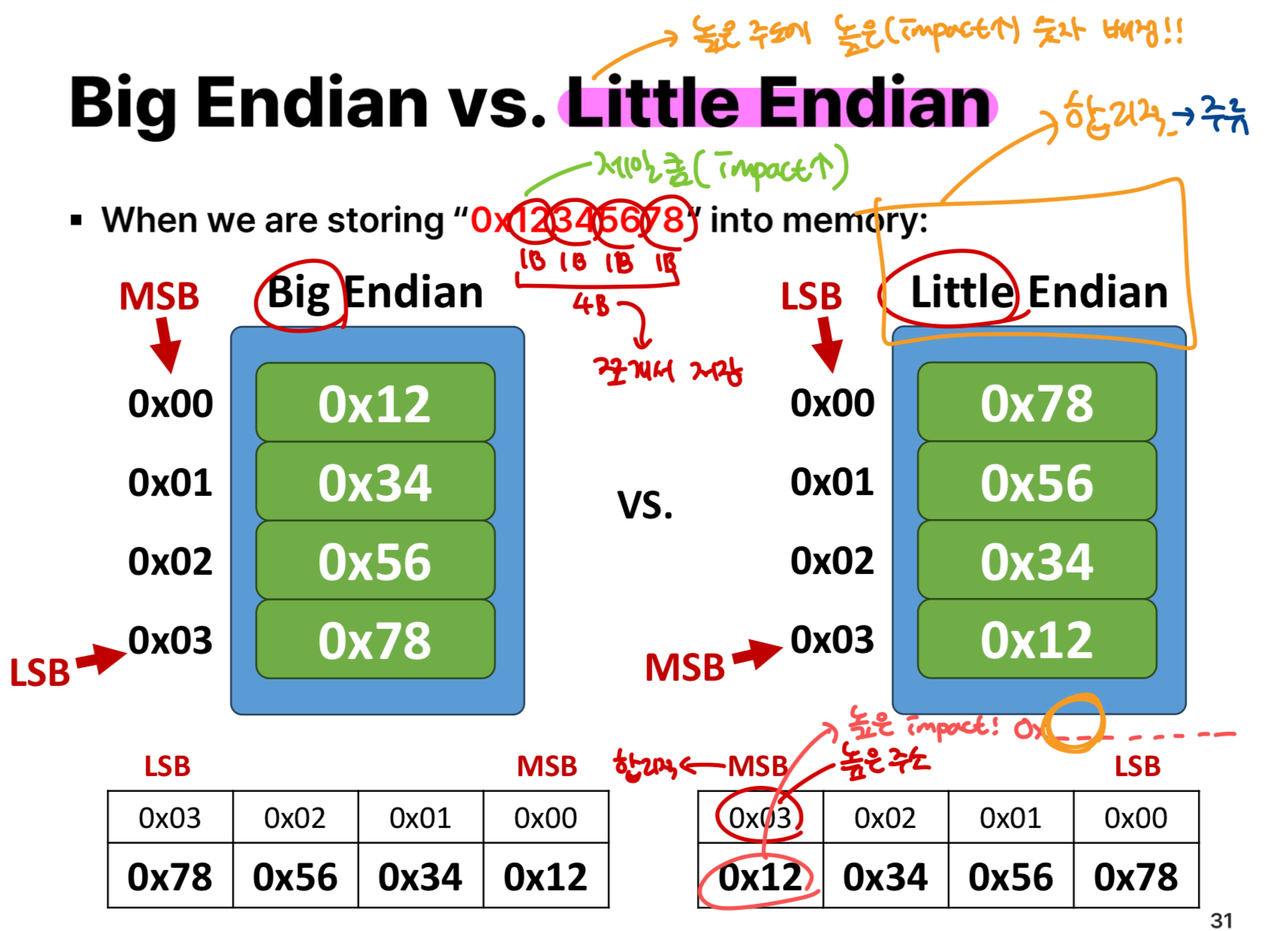

Big Endian vs Little Endian

걸리버 여행기 소설에서 비롯된 용어라고 하는데 별로 관심 없고

예를 들어 받아온 데이터가 0x12345678이라고 할 때 (스샷과 같이),

MSB (Most Significant Byte)는 0x12이고,

LSB (Least Significant Byte)는 0x78이다.

이때 MSB -> LSB 순으로 각각의 데이터를 저장하는 방식이 Little Endian,

반대로 LSB -> MSB 순으로 각각의 데이터를 저장하는 방식이 Big Endian이다.

사실 더 중요한(?)(MSB)의 데이터를 더 큰 주소의 저장공간에 저장하는 것이 조금 더 합리적으로 느껴지는데, 이 방식인 리틀 엔디언이 실제로 지금 아키텍쳐들이 주로 채택한 방식이다.

만약 서로 다른 방식을 채택한 기기끼리 통신을 해야한다면?! 당연히 변환 과정을 거쳐야 한다. 그렇지 않으면 상대방은 0x78563412로 값을 읽어서 대참사가 일어날 테니!

이걸 Decoding이라고 부르고, 행동의 주체(?)를 Decoder라고 부른다.

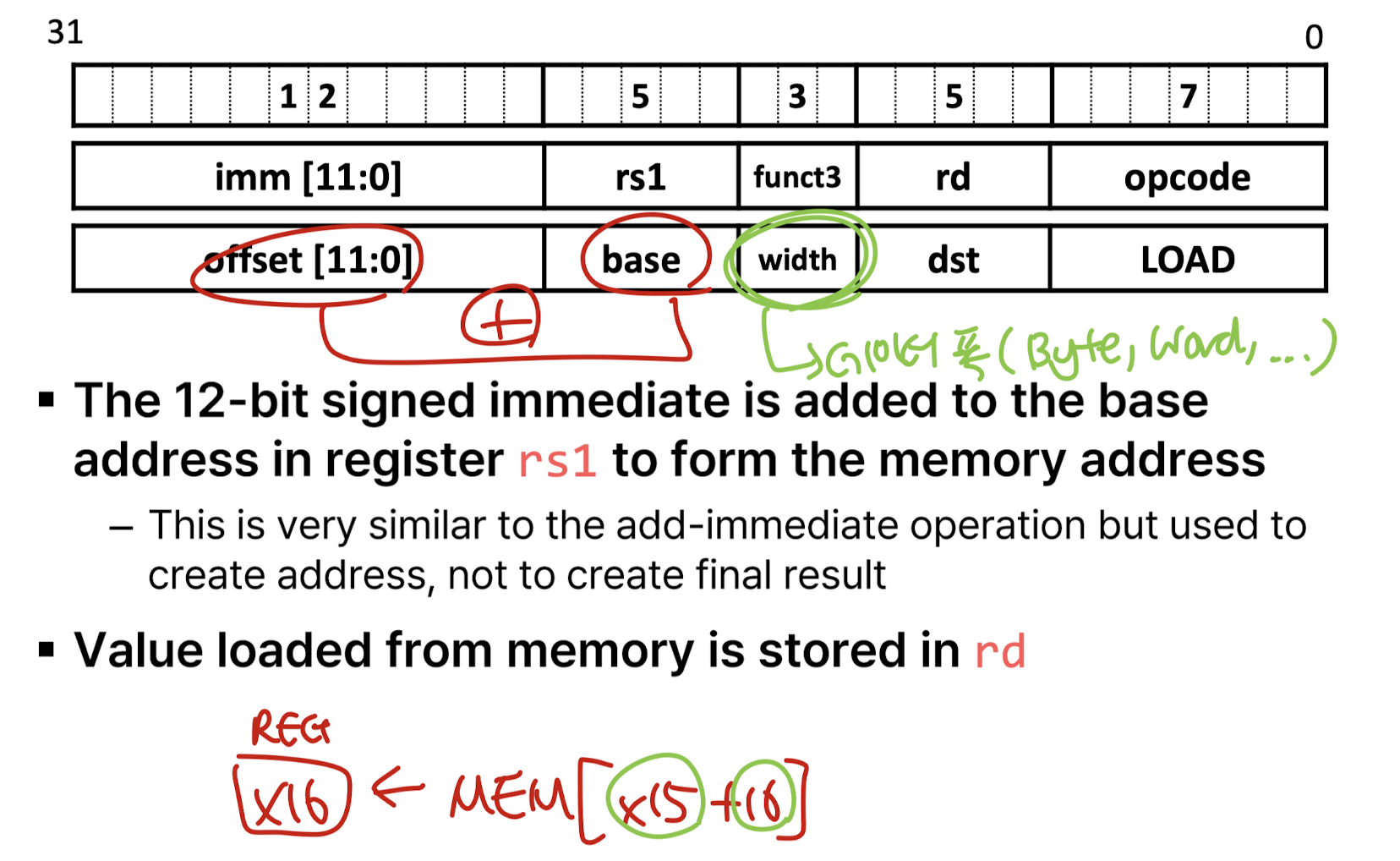

Transfer from Memory to Register

lw x10, 12(x13)

Reg x10 gets A[3] (int (4byte))

-> x10 from 12(x13)

lw: load word

- x13: base register (pointer to A[0])

- 12: offset in bytes : x13번지의 12(4x3)번째 칸,

즉 3번째 주소값을 뜻함!

lb x10, 3(x11)

Reg x10 gets A[3] (char (1byte))

-> x10 from 3(x11)

lb: load byte

- x11: base register (pointer to A[0])

- 3: offset in bytes : x11번지의 3번째 칸,

즉 3번째 바이트값을 뜻함!

Transfer from Register to Memory

sw x10, 40(x13)

A[10] = h + A[3]

-> x10 to 40(x13)

sw: store byte

- x13: base register

- 40: offset in bytes : 40번째 바이트값부터 1바이트 크기만큼!

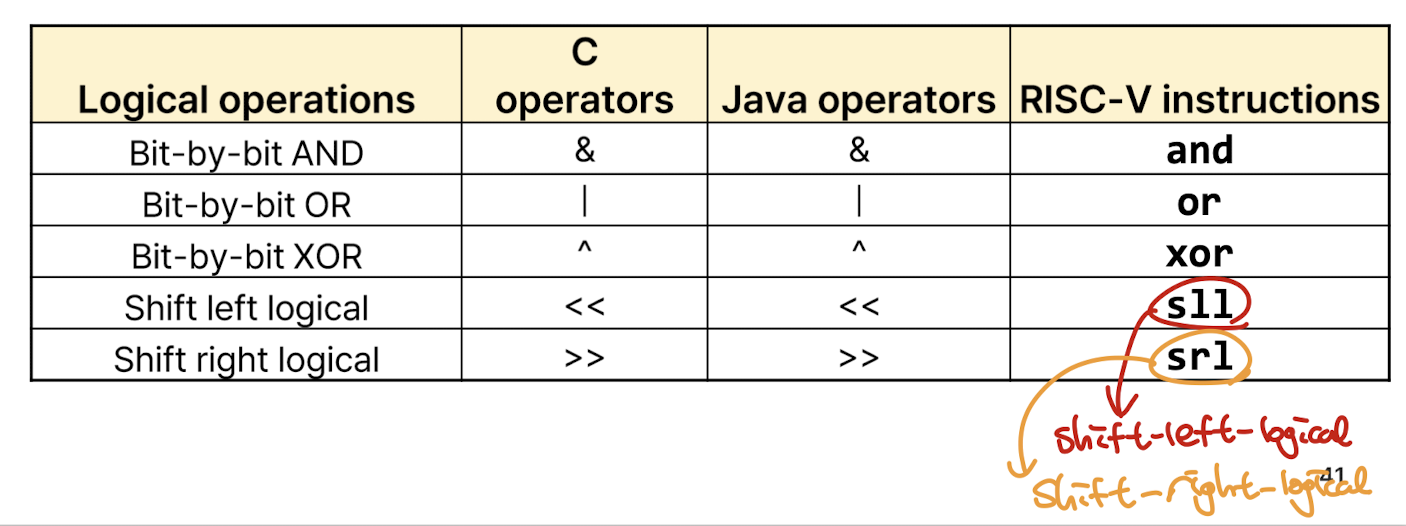

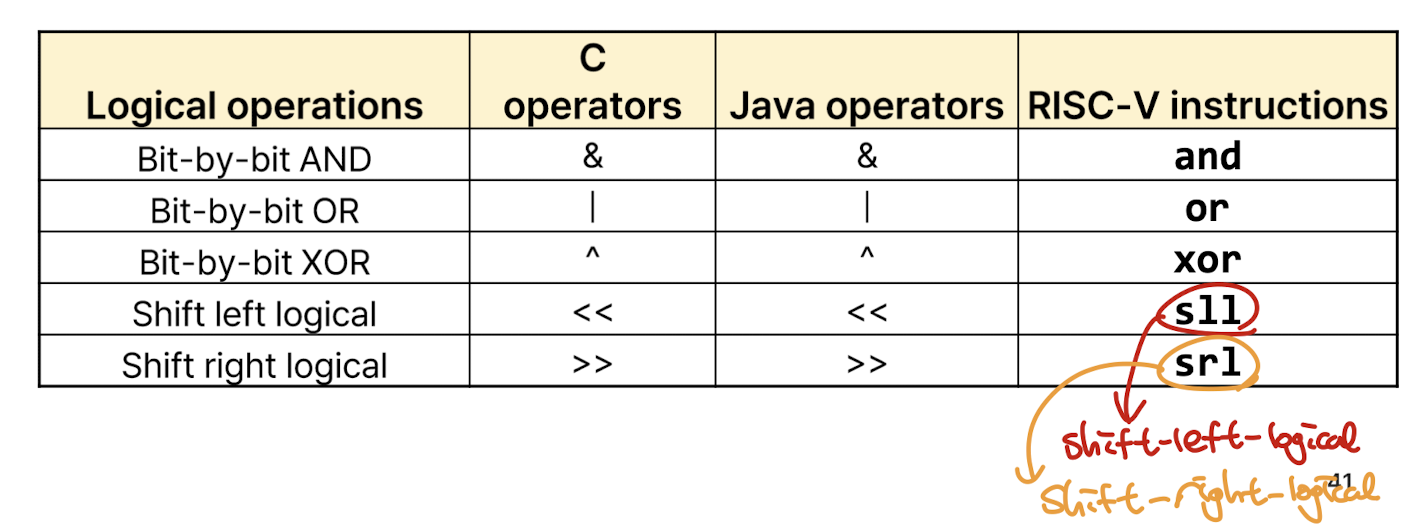

RISC-V Logical Instructions

Shift Left Logical (Immediate)

slli x11, x12, 2

x11 = x12 << 2

- Before: 0x0000 0002

0000 0000 0000 0000 0000 0000 0000 0010 - After: 0x0000 0008

0000 0000 0000 0000 0000 0000 0000 1000

Shift Right Logical (srli)는 완전히 반대!

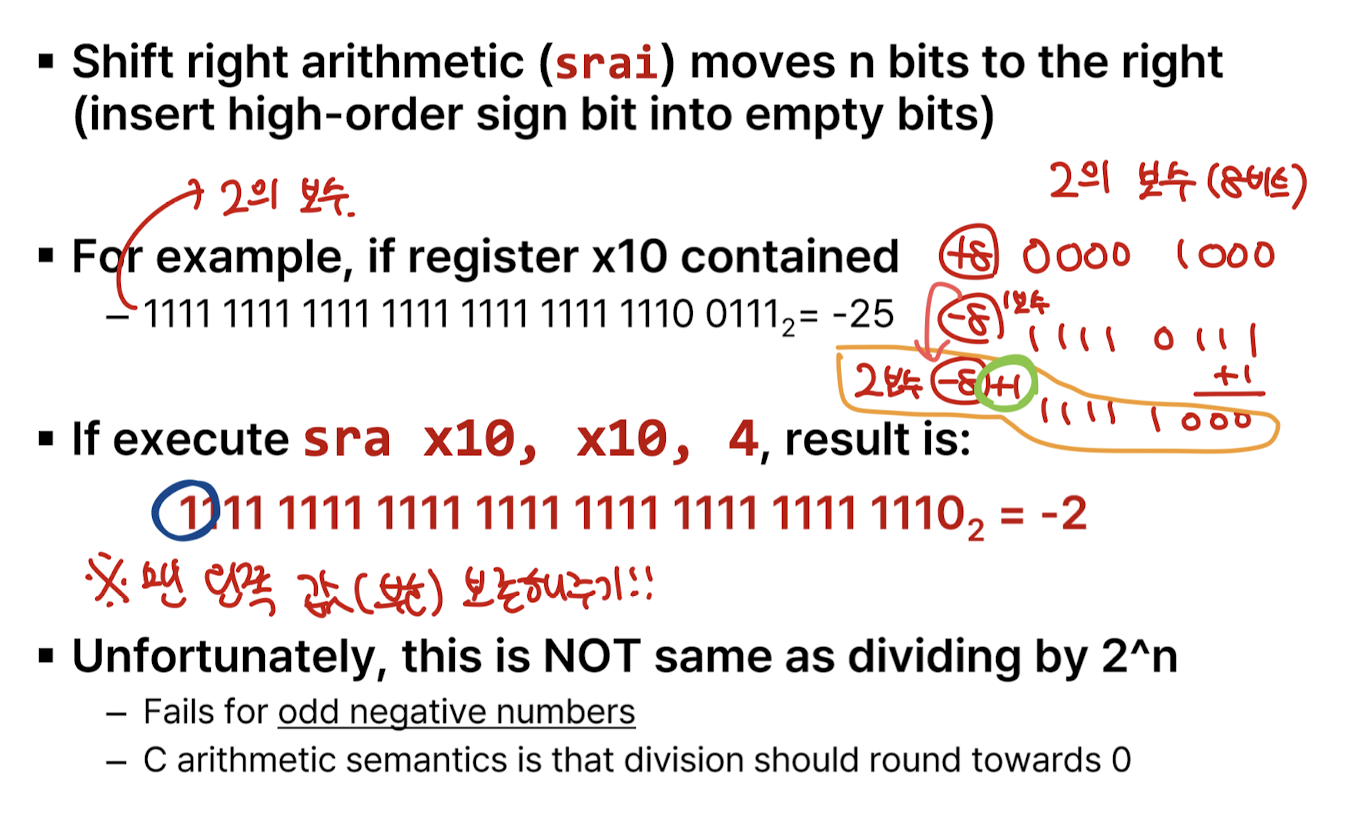

Arithmetic Shifting

2의 보수: 양수일 때 뒤집고 1 더하기!

Program Execution!

Computer Decision Making

Conditional Branch (BEQ, BNEQ 등)

비교의 결과 (equal or not equal)에 따라 프로그램 진행 흐름이 달라짐!

- BEQ: Branch if EQual (같으면)

- BENQ: Branch if Not EQual (다르면)

- BLT: Branch if Less Than (작으면)

- BGE: Brange if Greater than or Equal (크거나 같으면)

Unconditional Branch (JUMP)

무조건 Branch함 (C언어에서의 goto문)

- JUMP (J)

Instructions as Numbers

Most data we work with is in words (32-bit chunks)

-> RISC-V의 instructions들도 모두 1word 크기

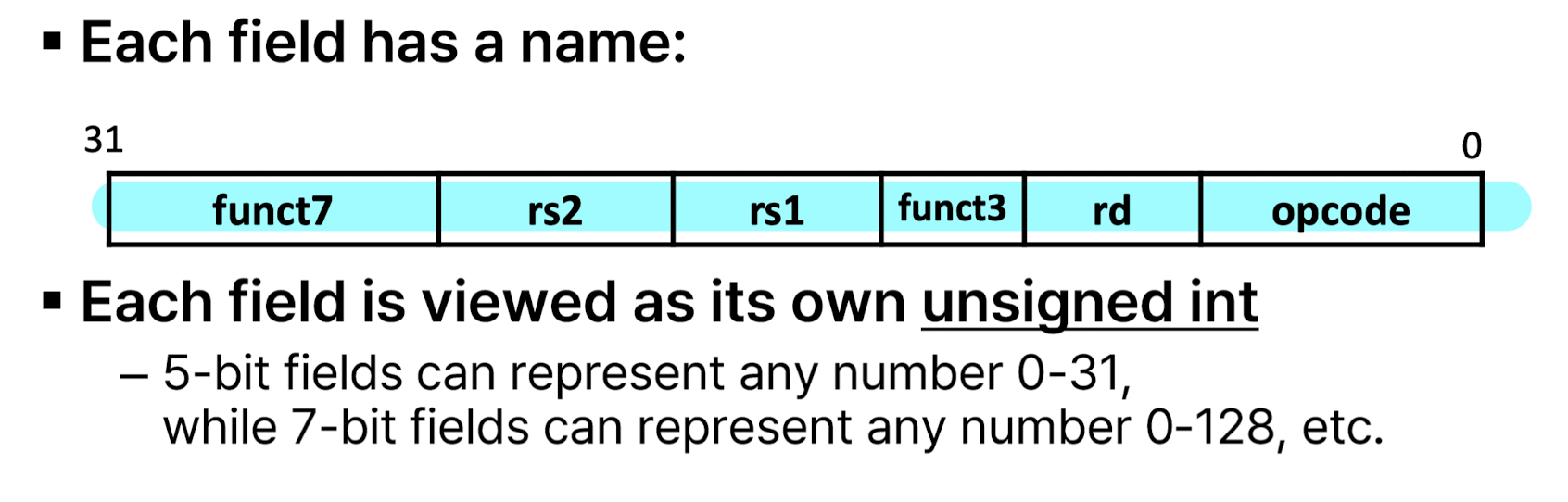

R-Format Instruction Layout

-

opcode (7-bits): 부분적으로 operation을 나타냄

ex) R-types opcode: 0b0110011, SB-types opcode: 0b1100011 -

funct7 + funct3 (10-bits): opcode와 함께 operation 정보를 담고 있음

ex) opcode가 동일한 add와 sub operation을 funct7 값으로 구분

예를 들어, R-format instructions들은 모두 opcode가 동일하므로, funct7와 funct3만을 이용해 2^7 * 2^3 = 2^10 (1024)개의 instruction 종류를 만들 수 있다.

- rs1 (5-bits): 1st operand (source register #1)

- rs2 (5-bits): 2nd operand (source register #2)

- rd (5-bits): designation register

왜 5-bits?: RISC-V는 32개의 레지스터가 있으니까!

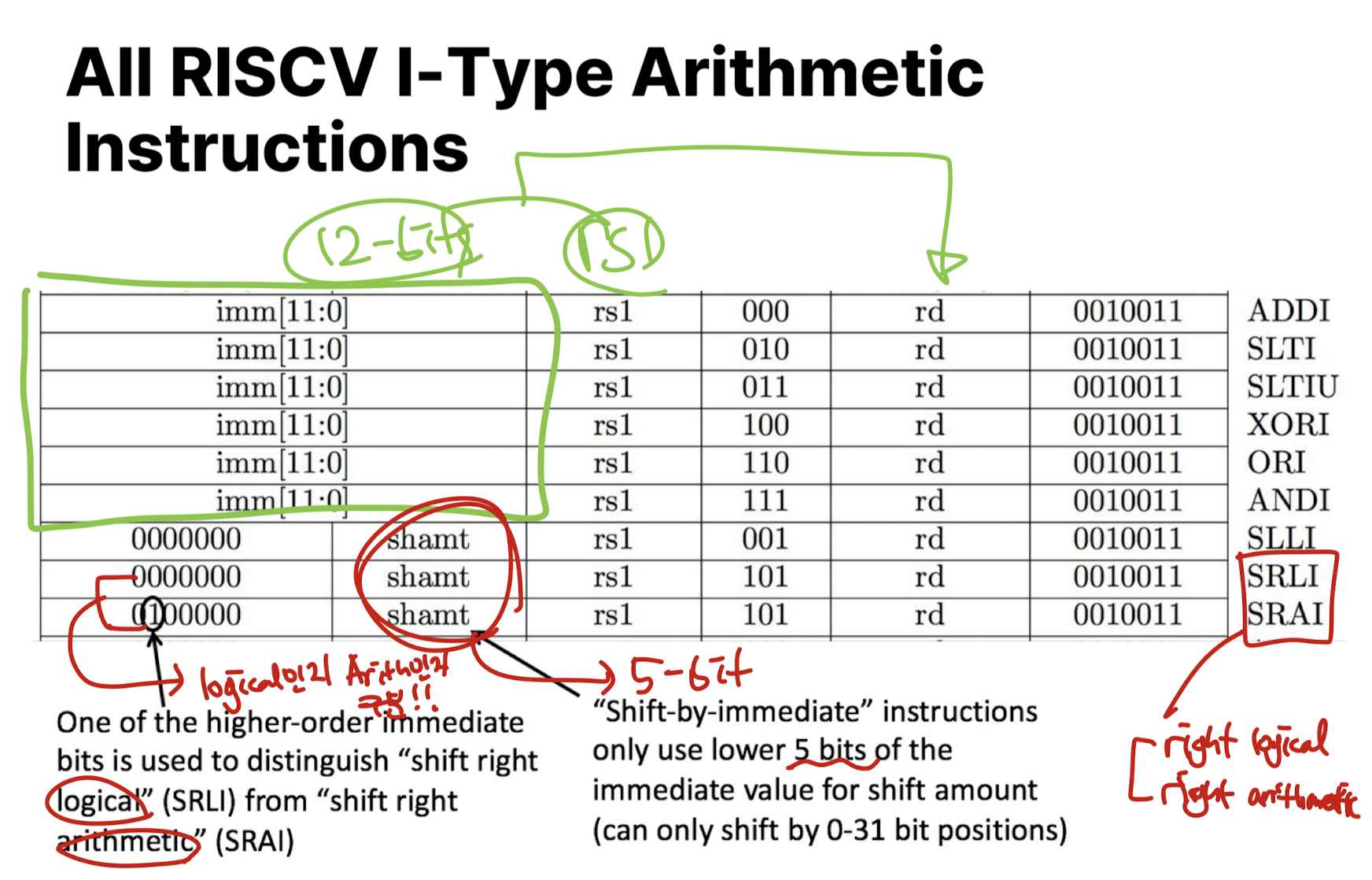

I-Format Instruction Layout

R-Format과 비교해, rs 하나가 불필요하다. 근데 남는 그 5-bit는 막상 상수를 표기하기에 부족해서, funct7도 하나 빼앗아온다.

-> funct7 + Reg(s2) 자리 (7+5 bits)를 immidiates 장소로 사용!

- opcode (7-bits): 부분적으로 operation을 나타냄

-

funct3 (3-bits): opcode와 함께 operation 정보를 담고 있음

-

rs1 (5-bits): 1st operand (source register #1, #2는 없음!)

-

rd (5-bits): designation register

-

immi (12-bits, former funct7 + rs2): 상수값 저장

모든 계산은 word 단위로 이루어지므로, 12-bit 상수도 32bits로 확장이 필요하다.

이때 부호 처리에 문제가 생길 수 있어서, 무조건 sign extension이 필요!!!

여기서 왜 shift instructions들의 immi 부분은 다른 instr들과 차이를 보일까?

왜냐면 shift는 최대 5번이면 충분하기 때문! 그 왼쪽 (more significant bit)에 있는 부분은 logical인지 arithmetic인지 구분하는 용도로 쓰인다.

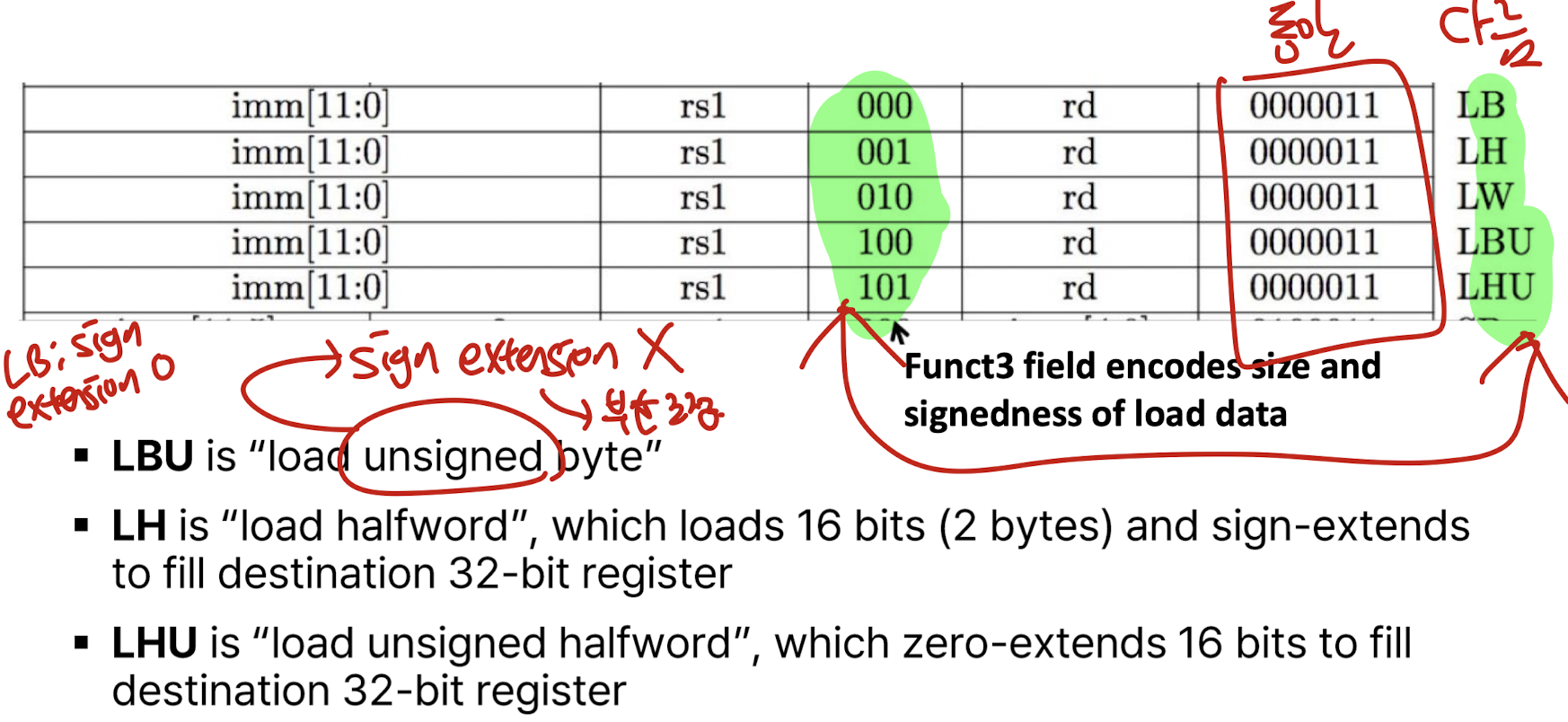

Load Instructions are also I-Type!

LBU vs LB, what does 'U' mean?

U for unsigned!!

Sign-extension 유무를 판단한다.