UART Serial 통신 프로토콜 FPGA Verilog HDL 설계 #1 Top module, Rx module

UART verilog HDL 설계와 FPGA 통신

UART Serial 통신 프로토콜이란?

UART 통신은 주변 장치와 컴퓨터 간의 데이터를 비동기적으로 직렬(serial)로 전송하는 통신 방식입니다. UART는 송신(Tx)하고 수신(Rx)하는 모듈과 주파수를 맞춰주는 Baud Rate 모듈로 구성됩니다.

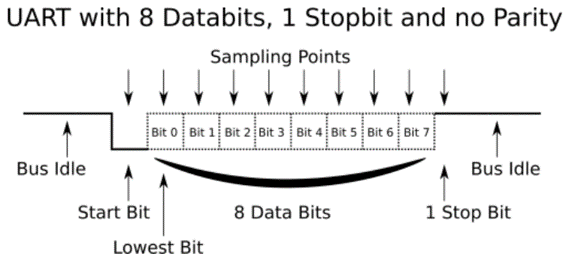

UART 통신 방법

UART는 시작(start)과 데이터(data) 비트, 패리티(parity) 비트와 정지(stop) 비트로 데이터를 전달합니다. 가장 먼저 start bit를 0으로 보내면 데이터 전송 상태가 되고 8개의 비트가 차례로 수신됩니다. (Parity bit는 추가 사항)

8 bit 입력이 수신부에 모두 저장되면 stop bit를 출력하고 송신부로 저장된 데이터를 전달합니다.

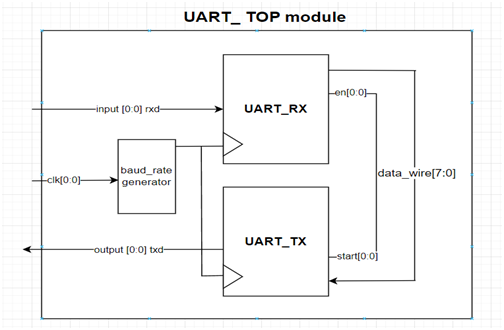

UART Top Module

Top module에는 Rx, Tx, Baud Rate generator 모듈을 각각 instance 하였습니다. 키보드로 문자나 숫자를 입력하면 ASCII 코드로 변환되어 0과 1로 이루어진 데이터로 전송됩니다.

Rx에 먼저 start bit가 들어오고 8 data bit가 모두 저장되면 done 신호를 출력합니다. Rx의 done 신호는 Tx에 start 신호로 들어가고 Tx 모듈이 동작하면서 그대로 데이터가 PC(컴퓨터)로 전송되게 했습니다.

Baud Rate generator 모듈은 외부에서 FPGA 동작 주파수 40mhz가 입력되면 115200hz로 변환하여 Rx, Tx 모듈에 들어갑니다.

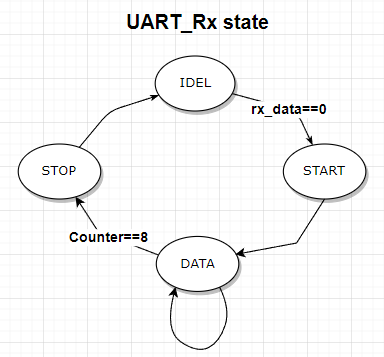

UART Rx Module (수신부)

Rx 모듈은 4개의 상태(state)로 나눠 동작하게 했습니다. 초기 IDEL 상태에서 start bit가 입력되면 START 상태로 전환됩니다.

START와 DATA 상태에서는 counter가 세어지면서 8 data bit를 out_data[7:0]에 저장하고 모든 값이 저장되면 STOP 상태로 전환됩니다.

STOP 상태가 되면 done 신호를 출력하고 이는 Tx의 start 신호로 들어갑니다.

localparam IDEL=0, START=1, DATA=2, STOP=3;

(*keep="true"*) reg [1:0] state; // 상태(state) 레지스터 선언

always @(posedge clk) begin // state always 문

case (state)

IDEL : if(rx_data==0) state <= START; // IDEL state

else state <= IDEL; // START state

START : state <= DATA;

DATA : if(counter==8) state <= STOP; // DATA state

else state <= DATA;

STOP : state <= IDEL; // STOP state

default: state <= IDEL;

endcase

end (*keep="true"*) reg [7:0] out_data; // 8 bit rx_data를 저장하는 레지스터 선언

always @(posedge clk) begin

case (state)

START : out_data[counter] <= rx_data; // 입력으로 들어오는 rx_data[0:0] 값 out_data에 저장

DATA : out_data[counter] <= rx_data;

default: out_data <= out_data;

endcase

end

always @(posedge clk) begin

case (state)

STOP : dout <= out_data; // STOP 상태에서 저장된 out_data 8 bit data 출력

default: dout <= dout;

endcase

end

자세한 코드는 github에 있습니다😊

Rx module Wave Form

저는 testbench에서 start 비트(1'b0)를 주고 1000_1100(2)=49(10)의 data 숫자와 stop 비트(1'b1)를 차례로 입력하였습니다. 마지막 stop 비트까지 모두 입력되면 done 신호가 출력되는 것을 확인할 수 있습니다.