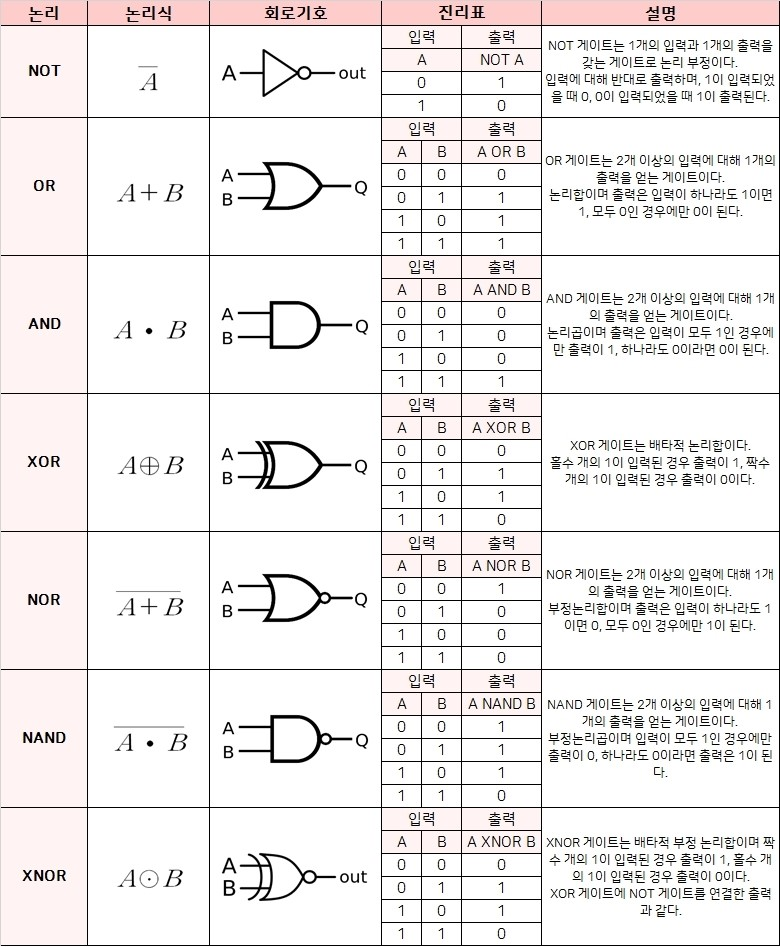

1. 논리회로

- 논리회로란, 디지털 신호를 input으로 넣었을 때 원하는 output을 만들어 내기 위해 논리적 순서에 의해 데이터를 manipulation하는 회로를 의미한다.

-

논리회로는 지난 챕터에서 배운 트랜지스터의 조합으로 만들어진다. (대표적으로 AND는 TR 2개를 직렬로, OR은 TR 2개 병렬로, NOT은 TR 1개로 만들 수 있다.)

-

‘카르노맵’ 같은 도구를 사용해서 원하는 output을 만들기 위해 어떤 논리회로가 필요한지 구할 수 있다.

-

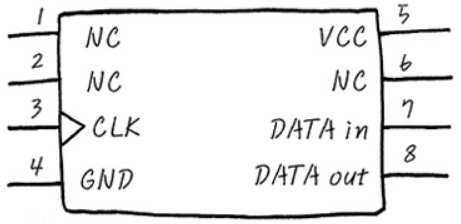

IC(Integrated Circuit)

- 수많은 논리회로가 합쳐져 하나의 package로 만든 chip을 IC라고 부른다.

- 우리는 IC의 datasheet를 읽고 pin 번호를 이해할 수 있어야 한다.

- NC는 ‘No connection’의 약자로 사용하지 않는 pin을 의미한다. ([※] 물론 핀도 돈이 들기 때문에 NC로 두면 낭비겠지만, 위 예시로 든 칩이 만일 DIP 패키지라면 어쩔 수 없이 다리를 만들었을 것 같네요.)

- CLK는 삼각형과 함께 그려지며 clock trigger pin을 의미한다.

- GND는 앞서 배웠듯이 ground, VCC는 전원

- DATA in/out은 이름 그대로 I/O를 위한 pin이다.

2. 레지스터(Register)

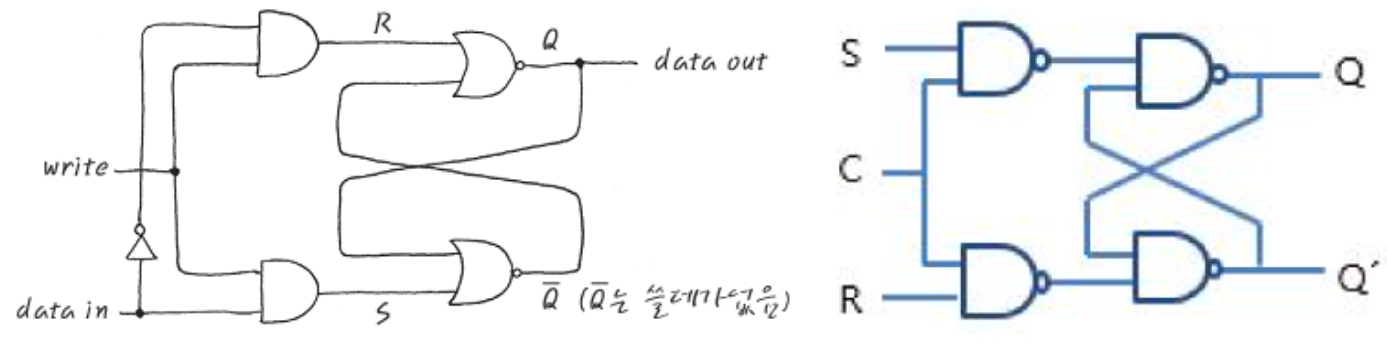

2.1. 레지스터의 정의와 플립플롭(Flip-flop)

- 레지스터는 CPU가 데이터를 처리하는 동안의 중간 결과를 일시적으로 저장하기 위해 사용하는 고속의 저장공간이며 플립플롭의 집합이다.

- 플립플롭(Flip flop, F/F’)이란, 1-bit의 정보를 저장할 수 있는 기억소자를 말한다.

- 플립플롭 중 하나인 RS(Reset-Set) 플립플롭은 NOR gate 2개의 output을 서로의 input으로 교차해 feedback하는 구조로 돼있다. ([※] 원문에서는 AND와 NOR의 조합으로 나타냈는데, 오른쪽 그림처럼 NAND 4개로 나타내는게 좀 더 일반적입니다.)

- R = 1이고 S = 0이면 Q는 무조건 0이 된다. (Reset)

- R = 0이고 S = 1이면 Q는 무조건 1이 된다. (Set)

- R = 0이고 S = 0이면 Q는 저장된 값을 그대로 유지한다. (No change)

- 만일 Q가 0이었다면, 밑쪽 gate에서 1이 나와 R쪽 gate로 들어가니 Q는 0. 유지.

- 만일 Q가 1이었다면, 밑쪽 gate에서 0이 나와 R쪽 gate로 들어가니 Q는 1. 유지.

- 위 경우의 수의 핵심은 플립플롭이 1-bit의 정보를 ‘저장할 수 있는 능력’이 있다는 점이다.

- 좌측 그림처럼 write 신호를 인가해서 플립플롭을 제어하는 걸 ‘level trigger flip flop’ 또는 ‘latch’라고 부르고 우측 그림처럼 clock 신호를 인가해서 CPU 동작 타이밍에 맞춰 제어하는 걸 ‘edge trigger flip flop’ 또는 ‘flip flop’이라고 부른다.

- 따라서 16-bit 레지스터는 위와 같은 플립플롭이 16개가 엮인 것을 말한다.

2.2. 레지스터의 종류

- CPU에는 많은 레지스터가 종류별로 구분돼 있는데, 대표적인 종류를 알아보자.

- General purpose register

- Address register - 메모리에 R/W할 때 데이터가 들어 있는 주소를 임시 저장하는 레지스터.

- Data register - 메모리에 R/W할 때 쓰려는 값 또는 읽은 값을 임시 저장하는 레지스터.

- Instruction register - 메모리에서 읽어온 명령어를 저장하는 레지스터.

- Special purpose register

- Program counter(PC) - 현재 실행되고 있는 주소를 가리키는 레지스터.

- Stack pointer(SP) - 사용중인 stack의 최상단 주소를 가리키는 레지스터.

- Linked register(LR) - 복귀할 주소를 가리키는 레지스터.

- Status register(SR) - 시스템/서브시스템의 현재 상태를 저장하고 알려주는 레지스터.

- I/O register

- General purpose register

3. Clock과 Timing diagram

- 디지털 회로는 논리회로들의 집합인 ‘conbinational 회로’와 플립플롭 같은 기억소자들의 집합인 ‘sequential 회로’으로 구성된다. 어느 하나만 사용해서는 너무 비효율적이다.

- 예를 들어, 5를 20번 더하고 싶을 때 adder 논리회로를 20개 연달아서 쓰는 것보다 adder 논리회로 1개와 레지스터 1개로 20번 feedback하면서 loop 돌리는게 더 효율적이다.

- 이때 레지스터에 값을 저장하고 다시 adder에 넣어주는 과정은 순서가 맞아야 한다.

- 동기화(Synchronization)는 1) 박자를 맞추다, 2) 순서를 맞추다 두 가지 뜻이 있다.

- Clock은 디지털 시스템 속 심장박동과 같으며 모든 것이 CPU의 clock에 맞춰 박자도 맞추고 순서도 맞춰 진행된다.

- 물론 clock은 빠르면 좋겠지만, 물성 상 input이 들어와 output으로 나가기까지 아주 약간의 delay가 있다.

- 신호가 0에서 1로 변하거나, 1에서 0으로 변할 때는 한 번에 변하는게 아니다.

- 신호가 switching 될 때 완전한 low 또는 high 신호가 되기까지의 10~90%까지 소요되는 시간을 전달소요시간(delay)라고 하며 이에 관한 전기적 특성을 스위칭 특성이라고 한다.

- 따라서 신호가 변하기까지 시간이 소요되므로 clock 속도는 무작정 빨라질 수 없다. 또한, 회로로 연결돼있는 이상, 전체 시스템의 속도는 가장 느린 소자의 속도에 맞춰야 전체 시스템이 오작동없이 동작한다.

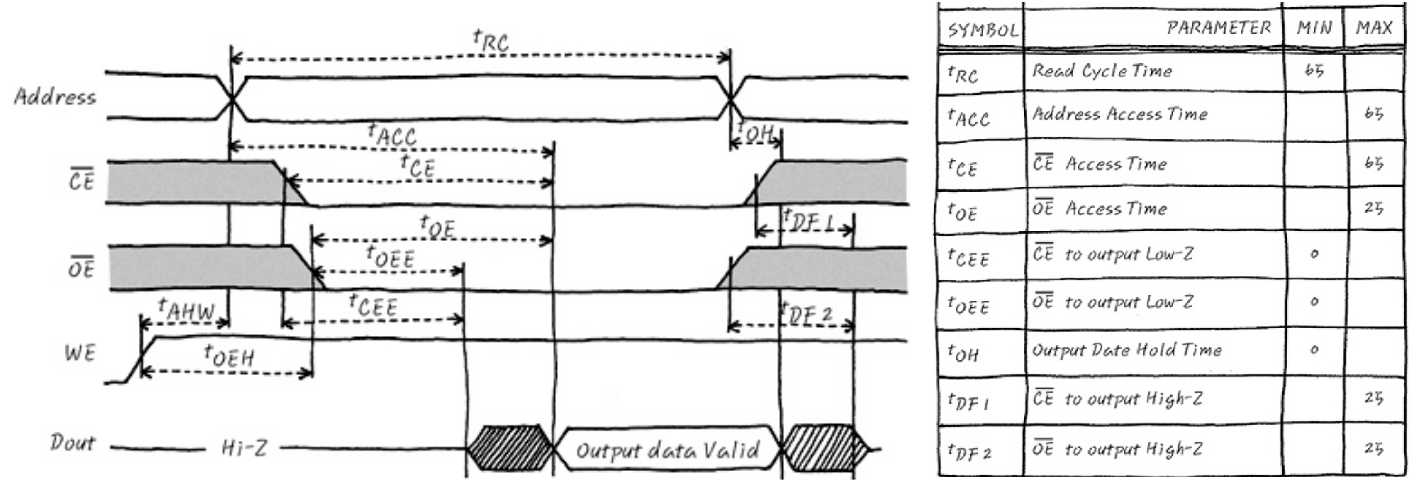

- Datasheet를 읽다보면 위와 같은 타이밍도를 만날 수 있는데, 해석하는 법은 다음과 같다.

- 색깔이 어두운 부분은 undetermistic한 부분이며 어떤 값이든 가질 수 있고 시스템 동작에 영향을 미치지 않는 부분을 의미한다.

- High impedance(Hi-Z)는 아무 유효한 신호가 없는 상태를 말한다.

- 예를 들어,

t_CE는 CE(Chip Enable) pin에 low active 신호가 인가된 뒤 유효한 output data가 나오기까지의 시간을 의미한다. 우측 표를 보니t_CE는 최대 65ns를 넘어서는 안된다고 알려주고 있다. t_RC는 read cycle time의 약자로 최소 저만큼의 시간동안 address line에 주소값을 대고 있어야 제대로 된 data를 얻을 수 있다는 뜻이다. 우측 표를 보니t_RC는 최소 65ns동안 대고 있어야 한다고 알려주고 있다.

4. Bus

- Bus란 장치들이 정보 공유를 위해서 공유하는 선들의 집합이다.

- 디지털 신호들이 bus를 통해서 ‘이동한다’라고 생각하기 보다는, 어떤 특정 시점에서 bus를 바라봤을 때 그 시점에서 bus를 ‘점유하고 있는 어떤 장치’의 신호만이 보인다고 이해하는게 더 정확하다.

- 위 정의에 따라, 하나의 bus에는 여러 장치가 연결돼 어떤 시점에 bus를 점유해 사용한다.

- 이 bus 점유권을 중재하며 bus 사용권을 결정하는 것이 CPU의 CU(Control Unit) 또는 아비터(Arbiter)이다.

5. Memory

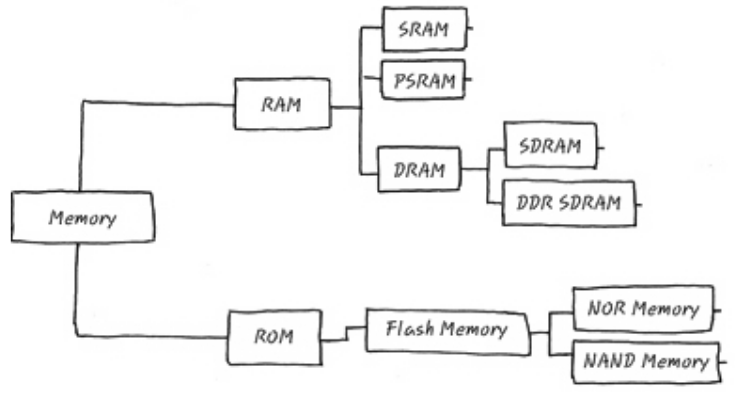

5.1. Memory 종류와 XIP

- 메모리는 크게 RAM(휘발성)과 ROM(비휘발성)으로 나눌 수 있다. 예전에는 ROM에 EPROM, EEPROM 등 여러가지 있었지만, 점점 발전하면서 임베디드 시스템에 탑재되는 MCP(Multi-chip Package)도 그냥 PSRAM + NOR 조합 또는 SDRAM + NAND 조합으로 가고 있다.

- SRAM(Static RAM)은 1개 cell이 트렌지스터 6개로 구성된 가장 비싼 RAM이다.

- DRAM(Dynamic RAM)은 1개 cell이 트렌지스터 1개에 캐패시터 1개로 구성된 값싼 RAM이다. SRAM에 비해 회로가 단순해 집적도가 높아 용량 뻥튀기가 가능하다. 하지만, 캐패시터에서 전하가 방전(누설)되며 PL172 규격에 따라 일정 시간마다 refresh가 필요하고 read 할 때마다 precharge도 필요하다. 안 그러면 데이터가 사라진다.

- DDR SDRAM(Double Data Rate Synchronous DRAM)은 CPU 동작에 박자와 순서를 맞춰가며 동작해 CPU 성능을 최대한으로 활용하는 DRAM을 말한다. 특히 DDR은 clock의 rising edge와 falling edge 둘 다 사용해서 data를 2배로 빨리 전송할 수 있는 메모리다.

- PSRAM(Pseudo SRAM)은 SRAM + DRAM 같은 느낌의 RAM인데 구조적으로는 DRAM이지만, HW적으로 refresh + precharge 해주는 회로가 내장돼있어서 따로 charge control 할 필요없이 SRAM처럼 쓸 수 있는 RAM이다.

- NOR Flash는 cell이 병렬로 연결돼있고 address line과 data line을 모두 갖고 있어 byte 단위로 random access가 가능한 메모리다. NOR은 read가 빠르지만, write/erase는 느리다.

- NAND Flash는 cell이 string이라 부르는 직렬로 연결돼있고 address line과 data line이 없어 집적도가 높고 page 단위로만 read/write이 가능한 메모리다. NAND는 read는 느리지만, write/erase가 빠르다.

- XIP(Execute In-place)는 메모리 상에서 직접 프로그램을 실행할 수 있는 기술을 의미하며 byte/ word 등의 크기를random access가 가능해야 한다. 모든 RAM과 NOR flash는 이를 충족한다.

5.2. RAM의 물리적 동작

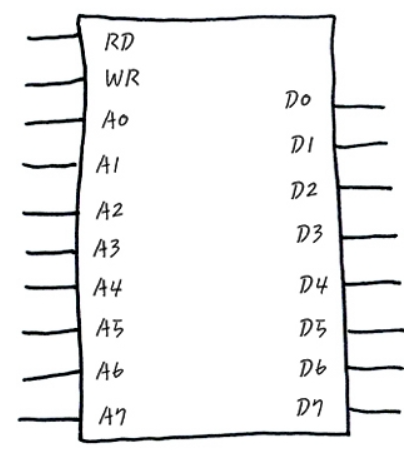

- RAM은 address pin(A0~A7)과 data pin(D0~D7) 그리고 control pin(RD, WR)으로 이뤄져 있다.

- Data pin이 8개니까 한 번에 8-bit씩 읽을 수 있다.

- Address pin이 8개니까 0x00부터 0xFF까지를 나타낼 수 있고 한 주소가 8-bit의 데이터를 가지고 있으니 이 메모리는 256-Byte 크기다.

- 이 RAM에 데이터를 써보자. 0xAB번지에 0x7C를 쓴다고 가정한다면,

- WR pin에 high 신호를 주고 RD pin에 low 신호를 준다.

- A[7:0] = 0xAB = 10101011, D[7:0] = 0x7C = 01111100 신호를 주면 된다.

- 반대로 읽을 때는 어떻게 할까? WR pin에 low, RD pin에 high 신호를 준 뒤 주소 지정해주면 D[7:0]에 data가 나온다.

6. CPU

6.1. CPU 구조 및 동작원리

- CPU는 논리회로의 집합체이며 약속된 신호를 주면 약속된 동작을 수행하는 단순한 원리로 동작한다.

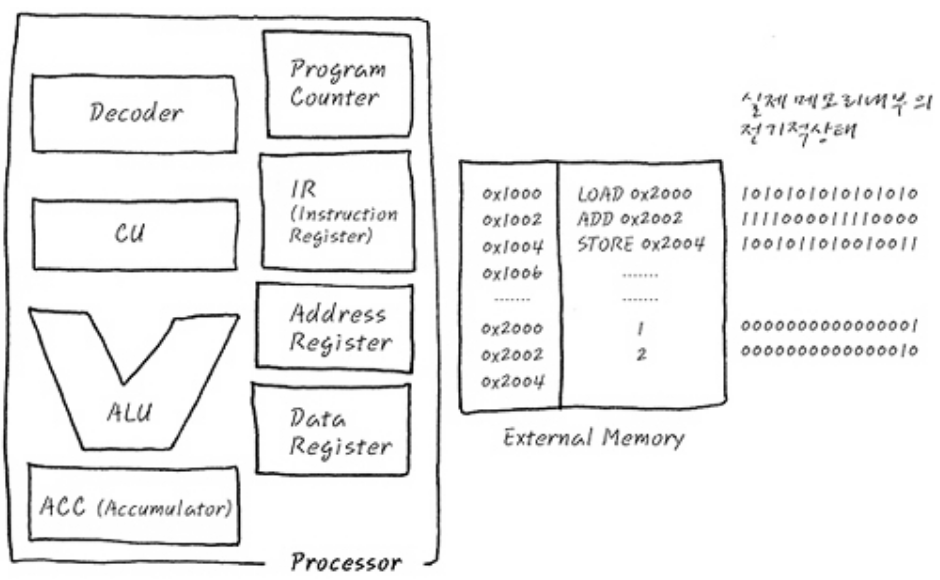

- CPU 내부는 CU(Control Unit), Decoder, ALU(Arithmetic & Logical Unit), Register set 등으로 구성된다.

- CPU의 동작원리는 decoder에서 명령어를 읽고 해석한 뒤 CU로 각정 제어 신호를 발생시켜 ALU 등에게 동작을 명령하는 것으로 이뤄진다. 동작하는 과정에서 임시로 빠르게 결과를 저장하고 참조하는 용도로 레지스터를 활용한다.

- CPU 이외에 여러 가지 기능(Flash, UART, I/O 등)이 한 개의 chip에 내장된 것을 MCU(Micro Controller Unit)이라고 부른다.

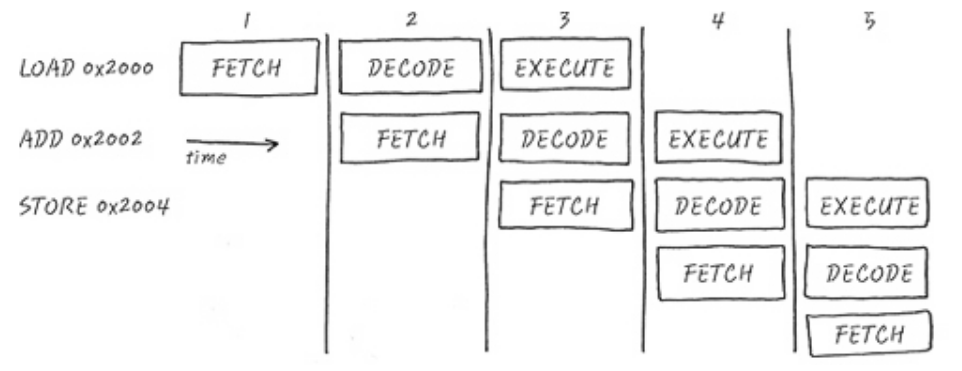

6.2. Pipeline

- ARM core CPU의 동작 구조를 단순하게 표현하면 fetch → decode → execute의 cycle로 돼있다.

- 예시를 통해 이게 사실인지 확인해보자.

word a = 1;

word b = 2;

word c;

void add() {

c = a + b;

return;

}- 위와 같은 C 프로그램을 컴파일 한 뒤 어셈블리를 생성했다. 이때 CPU는 16-bit processor이며 전역변수

a = 0x2000,b = 0x2002,c = 0x2004번지에 저장됐다고 가정하자.

주소 어셈블리

0x1000 LOAD 0x2000 ; a를 data register에 load

0x1002 ADD 0x2002 ; Data register에 저장된 값(a)과 b를 더해 data register에 저장.

0x1004 STORE 0x2004 ; Data register에 저장된 값(a + b)를 c에 저장. - 위 세 가지 명령어가 CPU 내부에서 수행되는 과정을 지켜보자.

LOAD 0x2000- PC(Program counter)는

0x1000번지를 가리킨다. - PC값이 ‘address register’에 저장된 뒤 해당 주소에 접근한다.

- 해당 주소에서 명령어를 읽어와 ‘instruction register’에 저장한다. (Fetch)

- Decoder가 명령어를 해석함과 동시에 PC는 증가해

0x1002번지를 가리킨다. (Decode) - CU는

0x2000번지에 있는 데이터를 읽어오라고 제어신호를 발생시킴 0x2000번지에 있는 전역변수 a의 값1이 ‘data register’에 저장됨. (Execute)- 이 값은 ALU를 통해 연산할지도 모르니 ACC(Accumulator)에 임시저장함.

- PC(Program counter)는

ADD 0x2002- ‘address register’에 저장된 PC가 가리키는 주소에서 명령어를 읽어와 ‘instrunction register’에 저장한다.

- Decoder가 명령어를 해석함과 동시에 PC는 증가해

0x1004번지를 가리킨다. 0x2002번지의 데이터를 ‘data register’에 저장한 뒤 ACC값과 덧셈한 뒤 ACC에 저장함.

STORE 0x2004- ‘address register’에 저장된 PC가 가리키는 주소에서 명령어를 읽어와 ‘instrunction register’에 저장한다.

- Decoder가 명령어를 해석함과 동시에 PC는 증가해

0x1006번지를 가리킨다. - CU는 ACC값을

0x2004번지에 저장하라고 제어신호를 날려 결과값을 저장함.

- 결국 CPU는 항상 Fetch → Decode → Execute를 반복하고 있다.

- 이때 각 단계를 담당하는 소자가 다른 것을 알 수 있다. Fetch는 PC, address register, instrunction register이고, Decode는 decoder, Execute는 CU, data register, ALU, ACC가 사용된다.

- 파이프라인은 각 단계를 중첩시켜서 하나의 시간에 여러 단계를 수행하도록 하는 기법을 말한다.

- 파이프라인의 단계가 많아지면 성능이 좋아질거라 예상할 수 있지만, 정도를 지나치게 될 경우 되려 성능이 떨어진다. (throughput이 낮아지고, branch prediction fail 때 패널티가 증가하고 등등)

- PC값은 execute 단계의 2개 명령어 밑을 가리키는데, 이 개념이 나중에 디버깅 때 굉장히 유용하게 쓰이니 기억해두자.