12.1. SoC 예시

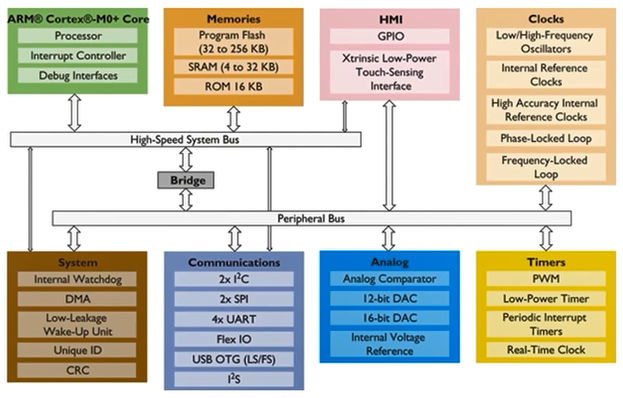

NXP에서 만든 MCU인 FRDM-KL25Z를 예시로 SoC의 구조에 대해서 알아보자.

FRDM-KL25Z는 ARM의 M0+ core가 탑재돼있다.- 프로세서만으로는 프로그램을 실행할 수 없으니까 인접한 곳에 메모리(SRAM)이 있는 것을 확인할 수 있다.

- Bus를 통해 memory로부터 instruction과 data를 받아와서 수행한다.

- Core와 memory는 high-speed bus로 연결돼있다. ARM은 bus에 대한 표준으로 AHB, AXI 프로토콜을 만들었다. (AHB와 AXI 프로토콜에 대해서는 다른 포스팅에서 훨씬 더 자세하게 다루기로 한다.)

- Low-speed bus인 peripheral bus와 high-speed bus가 bridge로 연결돼있는 2단 구조에 주목하자.

12.2. ARM Cortex-M0+

12.2.1. 구조와 구성

-

ARM Cortex-M0+ 프로세서는 ARMv6 아키텍처를 적용했다. ARMv6는 이전에 배웠던 RISC-V처럼 register를 operand로operation을 수행하는 load & store 아키텍처다.

-

총

R0부터R12까지 13개 register를 범용(general purpose) register로 정의했다.R13은 stack pointer,R14는 flow 변경 시 돌아올 주소를 저장할 link register,R15는 PC로 할당돼있다. -

특수 목적으로 사용하는 register도 있다.

PSR은 프로그램의 상태를 저장하고,PRIMASK는 인터럽트를 어떻게 마스킹할지 결정해주고,CONTROL은 내부적으로 control bit 같은 것을 관리한다.-

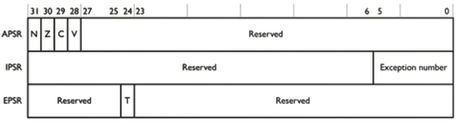

PSR

- Application PSR (

APSR): 수행중인 instruction의 상태 (N(Negative), Z(Zero), C(Carry), V(Overflow))를 알려준다. - Interrupt PSR (

IPSR): 수행 중 예외나 오류로 인터럽트가 발생했을 때, 발생한 예외에 대한 정보를Exception Numberbits로 알려준다. - Execution PSR (

EPSR): 수행하는 instruction의 종류를Tbit를 통해 알려준다. ARM은 평범한 길이의 instruction도 있지만, 짧고 빠른 Thumb 이라는 instruction도 있다.

- Application PSR (

-

PRIMASK- 발생한 인터럽트 또는 예외를 CPU가 handling할지 안할지 여부를 결정한다.

- 현재 CPU가 처리할 수 있는 인터럽트 종류를

PRIMASK의 정해진 bit마다 set해두면, 발생한 인터럽트에 해당하는 자리 bit가 set 돼있다면 handler를 수행하고, reset 돼있다면 wait 하는 방식이다.

-

CONTROL- Stack pointer로 활용하는

SP는 두 가지가 있다고 한다.CONTROL의SPSELbit로 둘 중 어떤 register를SP로 사용할지 결정한다.

- Stack pointer로 활용하는

-

-

모든 register는 32-bit로 구성돼있다.

-

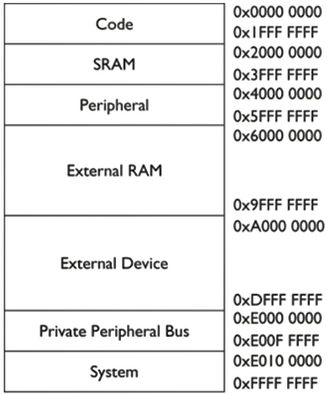

12.2.2. Memory map

-

Memory의 모든 공간을 자유롭게 활용할 수 있는 것은 아니다. 특정 영역을 특정 용도로 사용하기 위해 mapping 돼있다. 이런 특성을 Memory mapped 라고 부른다.

-

모든 프로세서는 저마다 개별적인 memory map을 가지고 있으므로 datasheet를 반드시 확인해야 한다.

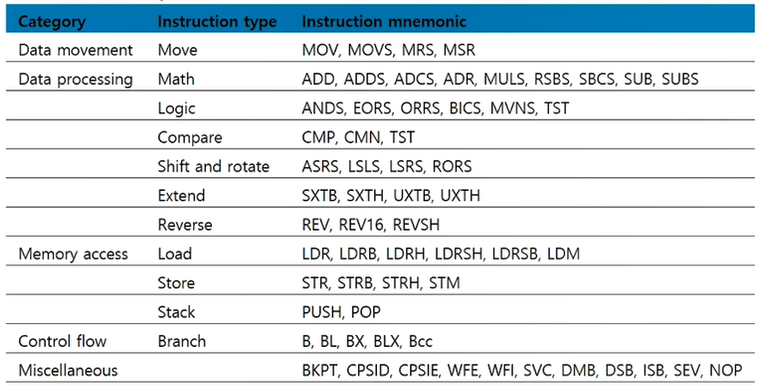

12.2.3. Instructions

- Instruction의 종류와 형태는 일전에 공부했던 RISC-V와 별로 다른점이 없다.

MOV/MOVS: Data를 target register로 옮기는 명령.-S는APSR의N,Zbit를 update까지 한다.MRS/MSR: Special register와 general purpose register 사이의 data movement 명령어다.

이후로 instruction에 대한 설명이 이어지는데 RISC-V와 거의 비슷하기도 하고, 필요할 때 검색해서 자세한 사용법을 알아보는 것이 더 효과적이라고 생각한다. 컴퓨터 구조/SoC를 공부하는 데 있어서 instruction의 종류 하나하나 상세히 공부하는 것은 비효율적이므로 요약 정리에서는 생략한다.