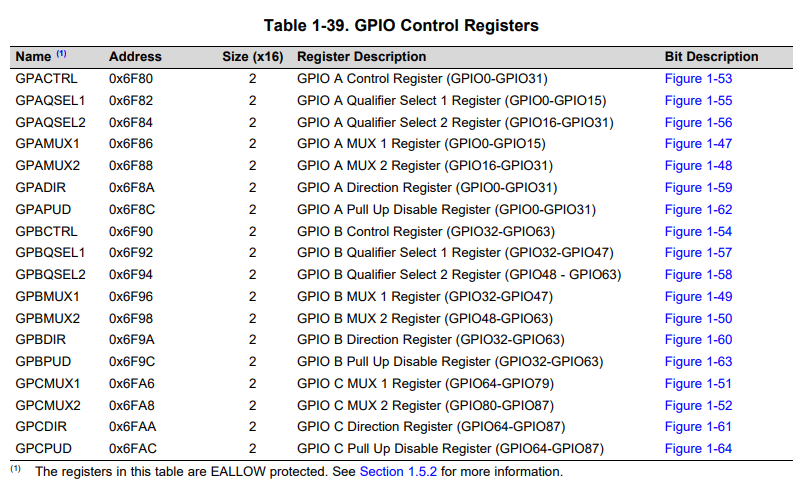

GPIO Control 레지스터

GPxDAT 레지스터

각각의 I/O 포트들은 하나의 데이터 레지스터를 가진다. 데이터 레지스터 안의 각 비트는 하나의 GPIO 핀에 상응한다. 각 비트는 Qualification 후의 상태를 반영한다.이 레지스터의 해당 비트는 0이면 LOW로 0V, 1이면 HIGH로 3.3V가 감지된다.

Ex) GpioDataRegs.GPADAT.all=0x000000FF; //해당 비트를 1로 설정

Ex) GpioDataRegs.GPADAT.bit.GPIO0=1 or 0;

GPxSET 레지스터

레지스터 핀이 출력 상태로 정의 되어 있을때, 출력값을 HIGH로 만들어 주는 기능이다. 0 입력을 하는것은 아무일도 안하지만 1을 입력할 경우 해당 신의 상태를 set 즉 1로 만든다.Ex) GpioDataRegs.GPASET.all=0x0000000F; // 해당 비트를 1로 set

Ex) GpioDataRegs.GPASET.bit.GPIO0=1;

이 레지스터는 쓰기 전용이다 따라서 Watch Window로 읽으면 무조건 0으로 읽힌다.

GPxCLEAR 레지스터

GPxSET와 반대로 1을 입력해줬을겨우 해당비트를 LOW 즉 0으로 clear 해준다. 마찬가지로 0을 입력할 경우는 아무일도 안한다.Ex) GpioDataRegs.GPxCLEAR.all=0x0000000F; // 해당 비트를 0으로 clear

Ex) GpioDataRegs.GPxCLEAR.bit.GPIO0=1;

이 레지스터 또한 쓰기 전용이다. 따라서 마찬가지로 watch window로 읽으면 무조건 0으로 읽힌다.

GPxTOGGLE 레지스터

이 레지스터는 GPIO의 출력 상태를 반전시키는 레지스터이다. 해당 비트 영역에 1을 입력하면 GPIO의 상태를 반전시킨다.Ex) LOW 일 때 GpioDataRegs.GPATOGGLE.bit.GPIO0=1 이라고 할 경우 GPIO 0번 핀의 상태를 HIGH로 바꾼다. 그리고 다시 이 상태에서 Toggle 할경우 LOW로 바뀐다.

이 레지스터도 0을 입력하는 것은 무의미하다.

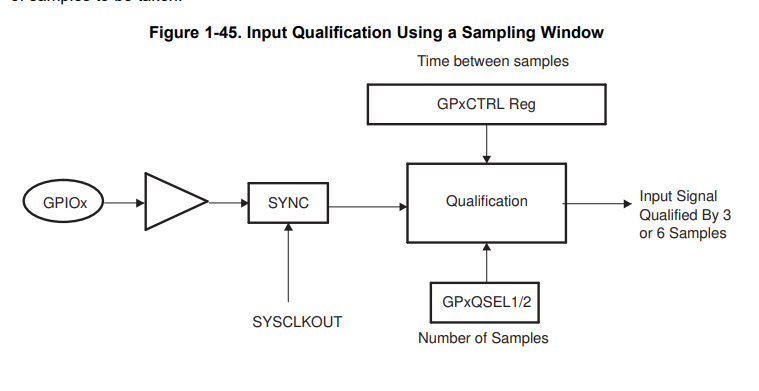

Input Qualification

실제 하드웨어는 작동시 여러요인으로 인해 노이즈가 포함된다. 대부분의 노이즈는 높은 주파수를 갖기 때문에 저역 통과 필터 (low-pass fillter.LPF)를 사용하여 차단이 가능하다. 저역 통과 필터는 RC 필터와 같은 하드웨어 또는 소프트웨어 필터로 구현 가능하다. 하지만 극심한 노이즈발생시에는 신호를 잘못 인식할 수 있다.극심한 노이즈의 경우에도 필터링이 가능하지만 이에 따른 시간지연과 연산 증가로 실시간 시스템에 영향을 줄 수 있다.

이 경우에 Input Qualifier 회로가 유용하다.

Qualifier은 자격심사라는 의미로 입력되는 신호의 유효성을 판단하는 것이 Input Qualifier이다.

위 그림은 Input Qualifier의 구조를 나타낸다. 외부에서 GPIO 입력 핀에 신호가 전달되면 버퍼를 거쳐 SYCN 회로에 입력된다. 외부에서 인가되는 신호는 DSP 내부 시스템 클러과 동기가 되어 있지 않기 때문에 SYNC회로를 거쳐 DSP와 동기화가 이루어진다. 동기화된 신호는 Qualification 회로 전달되어 Qualify를 수행한다. 이 Qualify 과정은 동기가 맞춰진 신호를 일정한 주기로 샘플링 하면서 시작된다. 이 때의 샘플링 주기가 바로GPxCTRL 레지스터와 관련있다.

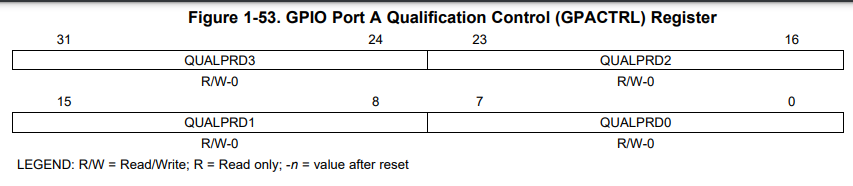

GPACTRL의 레지스터 구조이다.

총 4개의 QUALPRDx라는 영역이 있다. 이 영역은 0x00~0xFF까지 입력이 가능하고, 각각의 영역인

QUALPRD 1/2/3/4는 Qualifier 회로의 적용이 가능한 GPIO를 분할하여 담당한다.

- GPACTRL 레지스터

- QUALPRD0 -> GPIO 0 ~ GPIO 7

- QUALPRD1 -> GPIO 8 ~ GPIO 15

- QUALPRD2 -> GPIO 16 ~ GPIO 23

- QUALPRD3 -> GPIO 24 ~ GPIO 31

- GPBCTRL 레지스터

- QUALPRD0 -> GPIO 32 ~ GPIO 39

- QUALPRD1 -> GPIO 40 ~ GPIO 47

- QUALPRD2 -> GPIO 48 ~ GPIO 55

- QUALPRD3 -> GPIO 56 ~ GPIO 63

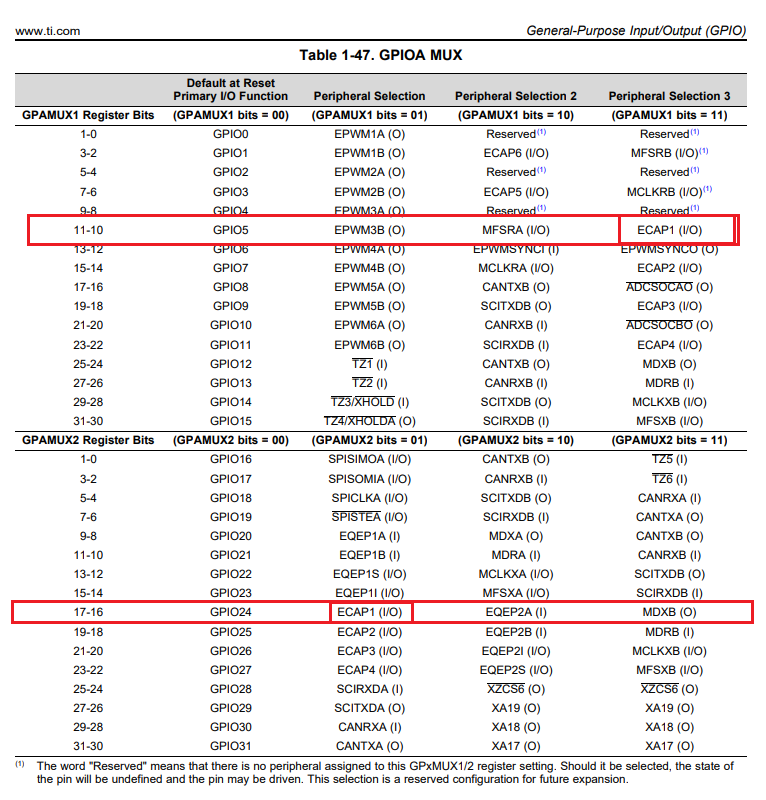

GPIO Peripheral Multiplexing(MUX)

GPIO 핀에는 최대 3개까지의 서로 다른 기능이 내재되어 있다. 필요에 따라 기능을 선택 할 수 있다.00 : I/O 기능

01 : EPWM 기능

10 : MCLKRA 기능

11 : ECAP 기능

간혹 같은 역할 (Ex. ECAP1은 GPAMUX1 레지스터 11-10, 17-16에 동시 할당)을 핀이 있다.

이때 서로다른 기능 수행시 오류 발생이므로 겹치는 핀이 존재할경우 다른 핀은 사용을 피해야한다.