PIE

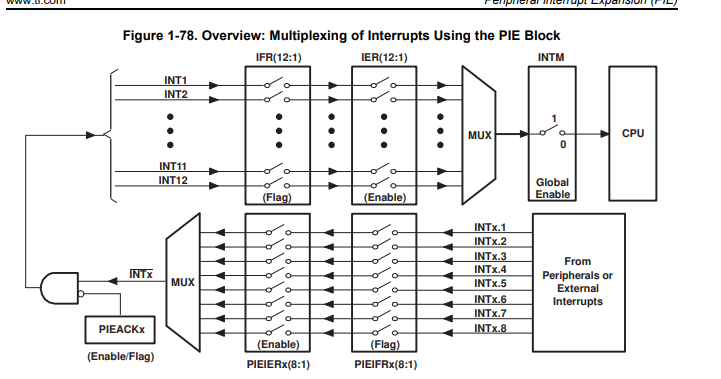

Peripheral Interrupt Expansion 의 약자로 28335에 있어서 여러 작은 인터럽트들의 집합이다.

PIE는 8개의 그룹화된 96개의 개별적인 인터럽트를 제공한다. 96개의 인터럽트들은 전용 RAM 블록 안에 있는 각각의 벡터에 의해 제공된다.

Interrupt Operation 순서

Peripheral Level

Peripheral Level에서 인터럽트 이벤트가 발생하면, 그 이벤트에 상응하는 Interrupt Flag(IF) bit 가 set 된다. 그 다음 IF에 해당하는 Interrupt Enable(IE) bit가 set 된다. 그 후 Peripheral은 PIE controller에 인터럽트의 요청신호를 발생한다.만약 Enable이 되지 않는다면, IF는 소프트웨어에 의해 clear 될때까지 그 상태를 유지한다.

인터럽트가 Enable 되면 IF 여전히 set 상태이며, 인터럽트의 요청이 PIE로 넘어간다. 이때 IF는 반드시 수동으로 clear 시켜줘야 한다.

PIE Level

PIE 블럭은 8개의 peripheral과 external pin interrupt를 하나의 CPU 인터럽트로 멀티 플랙싱(Multiplexing)한다. 이런 인터럽트들은 12개의 그룹(PIE group 1 ~ PIE group 12)으로 나눠 진다.Ex) PIE group1은 CPU 인터럽트 1(INT 1)으로 PIE group12가 CPU 인터럽트 12 (INT12)로 멀티 플랙싱된다.

한 그룹에서 8개의 INTx.y는 합쳐지기전에 우선순위가 하드웨어 적으로 정해진다.

예를 들어 INTx.1과 INTx.3이 동시에 걸리면 우선순위에 따라 INTx.1이 먼저 PIE Level를 통과한다.

하지만 소프트웨어적으로 무시할 수도 있다.

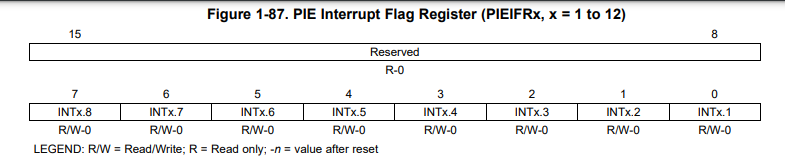

위의 그림은 PIEIFRx 레지스터의 구조이다.

PIEIFRx는 PIE Interrupt Flag Register이다.

인터럽트가 DSP에 도달하여 CPU가 ISR로 분기할 때 0으로 자동 clear 된다.

또한 PIEACKx가 set이 되면 PIEIERx도 set가 되어 DSP에 도달하지 못하도록 한다.

즉. PIEAKx가 0으로 clear 될떄까지 인터럽트가 통과하지 못하고 대기상태로 남게된다.

PIEACKx는 PIE Acknowledge bit로 한 그룹 전체의 인터럽트를 Eable/Disable할 수 있다.

DSP가 해당 그룹으로부터 인터럽트를 받을 수 있는지 없는지 알려주는 레지스터이다.

즉, PIEACx가 0으로 clear되어 있어야 PIE Level로 인터럽트 요청를 보낼 수 있다.

이때 인터럽트 요청이 1로 set되기 때문에 Acknowledge 역할을 할 수 있다.

PIEACKx는 한번 set되면 수동으로 clear 전까지 set 상태라는 점을 주의해야한다.

CPU Level

PIE Level에서 인터럽트 요청을 받아 들여 DSP까지 도달하는 부분이 CPU Level이다.

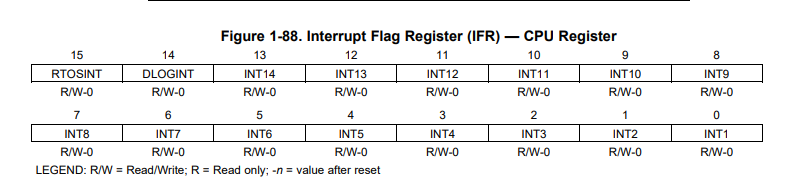

PIE Level의 PIE group x가 INTx와 연결된다. IFR과 IER 역할은 PIEIER과 PIEIFR과 같다

위는 IFR과 IER 레지스터의 구조이다.

INT12, INT13, DLOGINT, RTOSINT 들은 PIE Level을 통과하지 않고 바로 CPU Level로 들어온다.

RTOSINT는 Real-Time Operationg System Interrupt(Flag/Enable)인데 RTOS에서 사용허눈 인터럽트이다.

DLOGINTs는 Data Logging Interrupt(Flag/Enable)이다. 인터럽트가 INTM을 통과하여 DSP가 응답하면 IFR은 0으로 clear된다.

INTM은 Global Interrupt Mask로 PIEACKx처럼 인터럽트를 Enable/Disable할 수 있다.

INTM은 C코드로 직접 접근할 수 없고 엄셈블리로만 가능하다.

따라서 다음과 같이 접근한다.

asm("clrc INTM") // 0으로 clear

asm("setc INTM") // 1로 set인터럽트 요청의 흐름

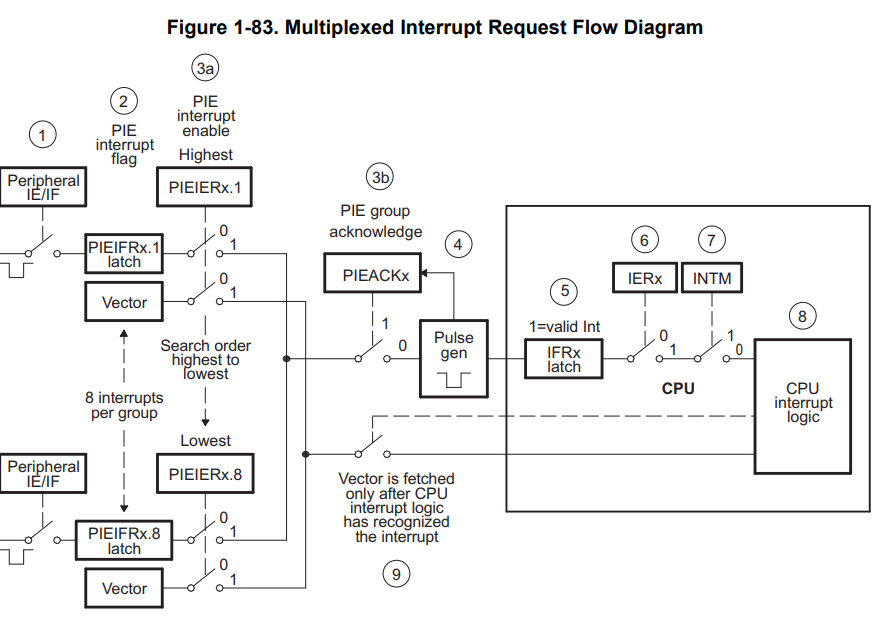

- PIE group내의 Peripheral이나 external interrupt에서 인터럽트가 발생한다.

이 인터럽트가 Peripheral module에서 Enable되면, 인터럽트 요청을 PIE 모듈로 전송한다. - PIE module은 PIE group x안의 y인터럽트의 요청을 인지하고 PIE interrupt Flag 비트를 레치(Latch) 시킨다. PIEIFRx.y=1

- 인터럽트 요청신호가 PIE Level에서 CPU Level로 전달되기 위해선 다음 두 조건을 만족해야한다.

3.1 PIEIERx.y 비트가 1로 Enable되어야 한다.

3.2 PIEACKx비트가 clear되어야 한다. - 위 두 조건이 모두 참일경우 인터럽트 요청이 CPU와 acknowledge bit가 다시 설정된다.(PIEACKx=1) 이 비트는 사용자가 초기화 시키기 전까지 이 상태를 유지한다.

- CPU Interrupt Flag bit가 set된다.

- CPU 인터럽트기 Enable( CPU IER bit x = 1, DBGIERbit x = 1)되고, Global Interrupt Mask가 clear되면, CPU는 INTx를 제공한다.

- CPU가 인터럽트를 인지하고 자동적으로 context save를 수행하며, IER bit를 clear하고, INTM을 set 시키고 EALLOW를 clear한다.

- 그러면 CPU는 PIE를 위한 적절한 벡터를 요청한다.

- PIE module은 PIEIERx와 PIEIFRx 레지스터를 이용하여 해당 인터럽트의 벡터주소를 해독한다. 이때 우선순위를 한번더 고려한다.