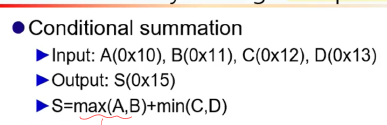

MU0 - a simple processor

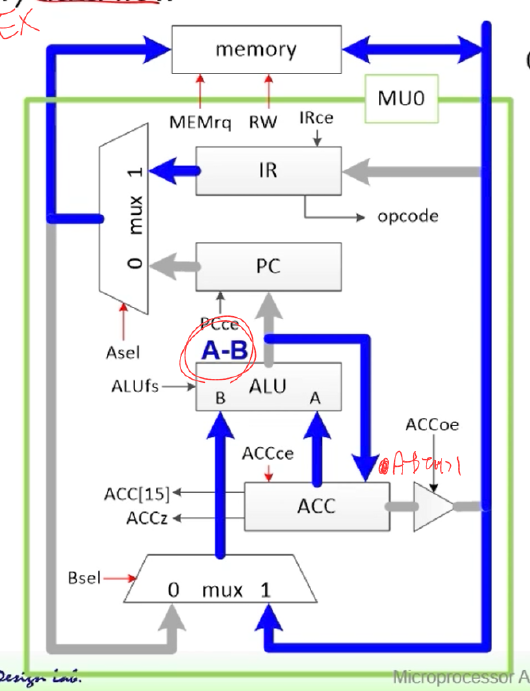

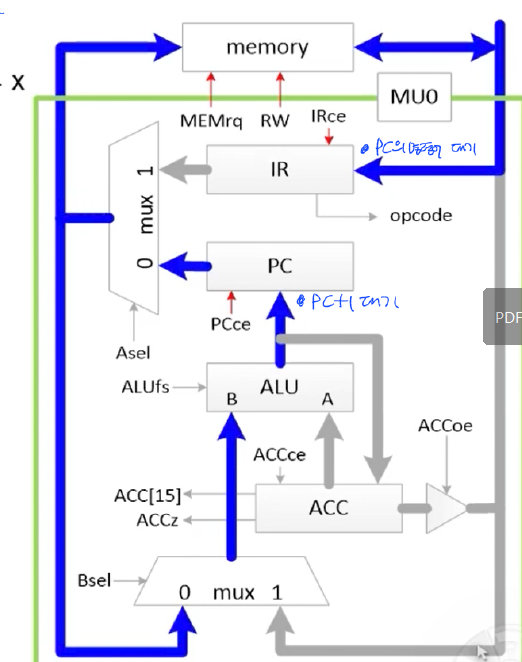

MU0 architecture

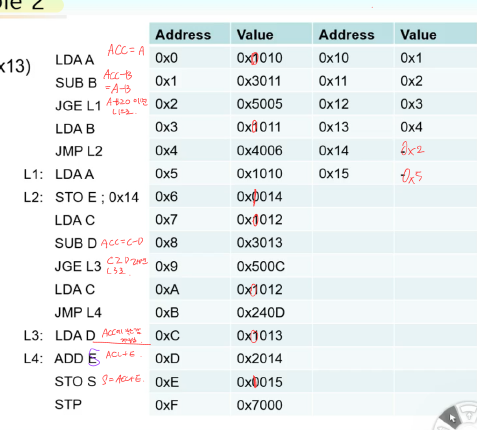

- 명령어 16bit & 레지스터 16bit

- 12bit address space

- 메모리 주소가 2^12 = 4K개 → 하나의 주소가 가리키는 메모리 크기는 2byte!!!

⇒ 메모리 크기는 8K bytes

Components

- program counter(PC)

- 다음에 실행할 명령어의 주소를 가지고 있음

- Accumulator(ACC)

- data를 가지고 있는 것(일종의 레지스터)

- Arithmetic-logic unit(ALU)

- binary 연산을 하는 곳 (add, subtract, increment...)

- Instruction register(IR)

- 현재 실행 중인 명령어를 저장하는 레지스터

- Instruction decode and control logic

- 명령어를 해석하고 필요한 제어신호를 생성하는 부분

- Instruction set assembly(ISA)에 따라 결정됨

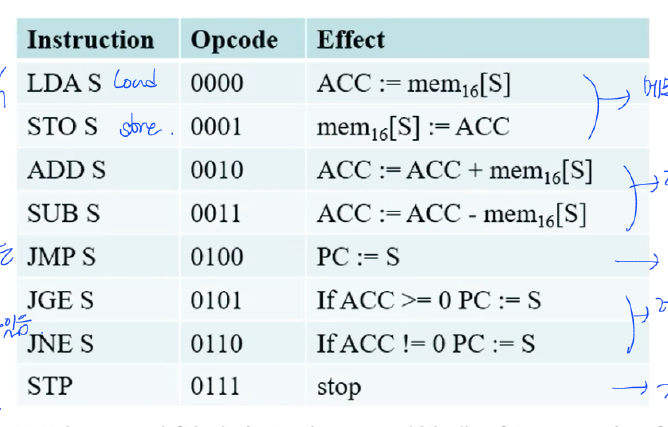

Instruction set

- 프로세서 설계할 때 가장 먼저 이걸 확인해야해

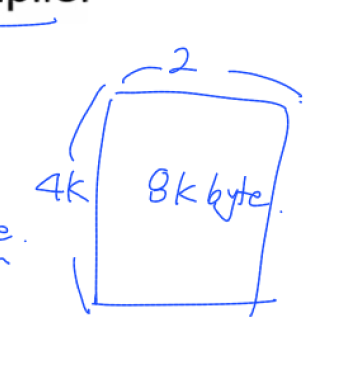

Instruction format

- opcode : 4bit ⇒ 2^4 = 16 ⇒ 16개의 명령어를 가질 수 있음

- opcode는 instruction 종류를 결정하는 부분

- address : 12bit ⇒ 2^12 = 4K개

Instructions

- basic instruction은 8개 ⇒ 나머지 8개는 사용자가 확장 가능

- LDA, STO : 메모리에서 데이터를 읽어오거나 저장하는 곳

- ADD, SUB : ACC의 값과 메모리의 값을 더하거나 빼고 다시 레지스터에 저장하는 명령어

- JMP : S가 가리키는 주소로 jump

- JGE, JNE : ACC에 있는 값에 따라 다음 명령어의 주소를 S로 할지 말지 결정

- STP : 계속 다음 명령어를 자기 자신으로 유지 ⇒ stop

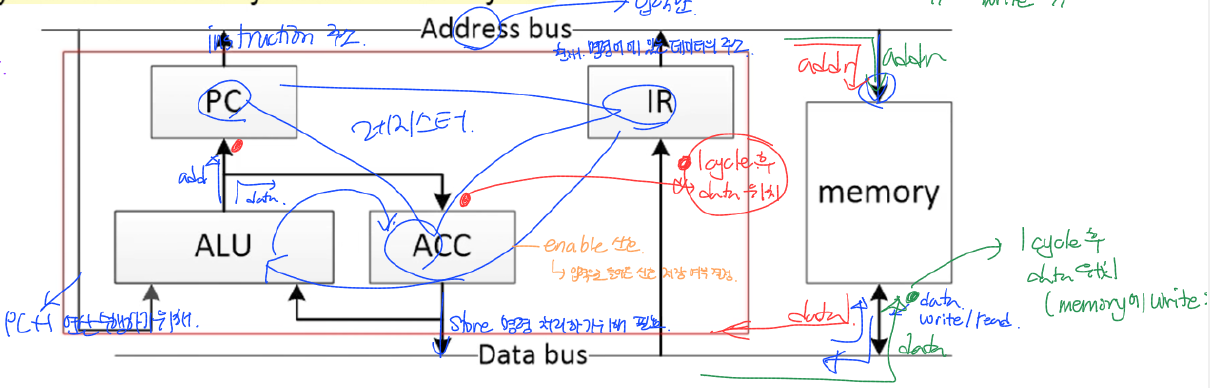

Logic design

Data path

- 데이터를 저장하고 계산하는 구성 요소들이 있음 (ACC, PC, ALU, IR)

- memory와 레지스터에 접근할 때는 1cycle이 소모됨

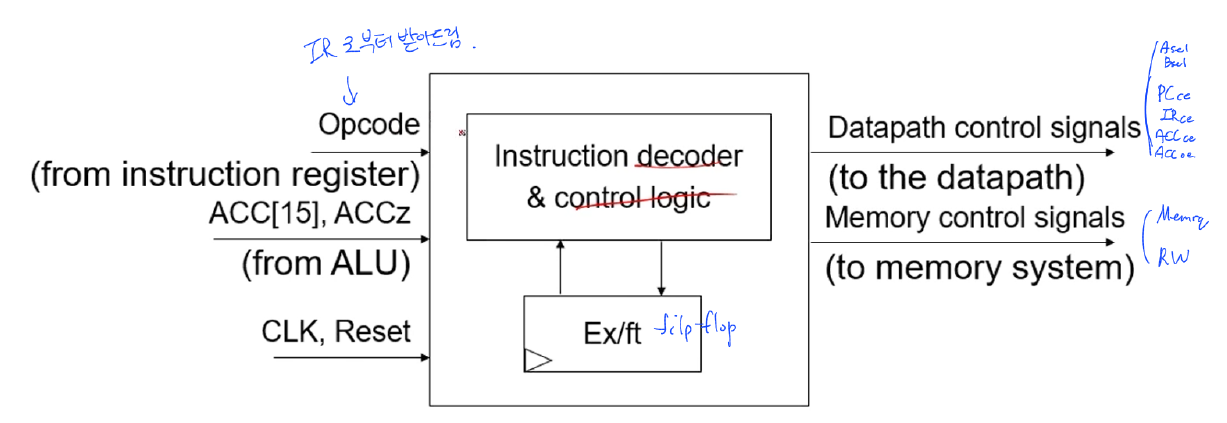

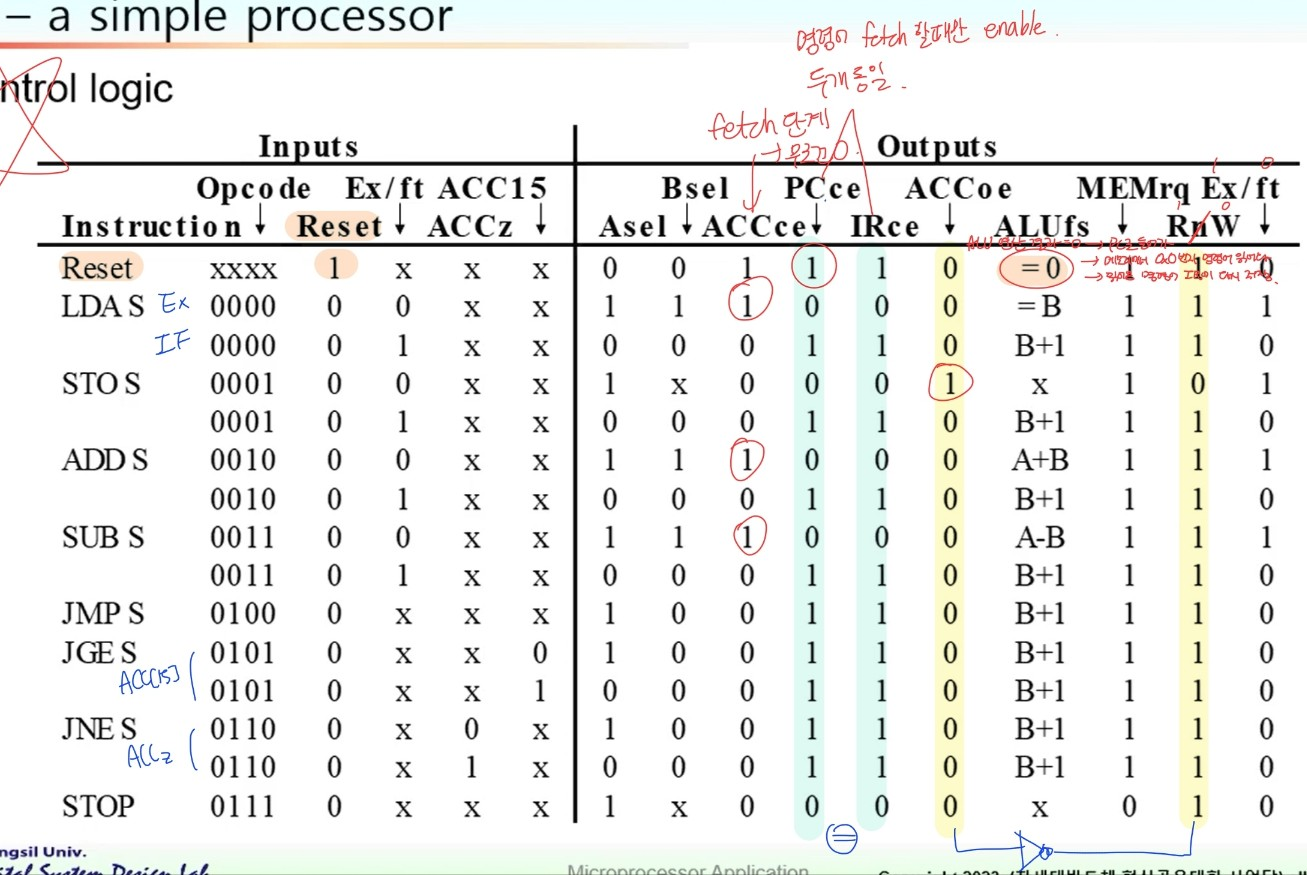

Control logic

- data path의 제어 신호를 input으로 받아 연산을 해서 data path에 또다른 제어 신호를 보내

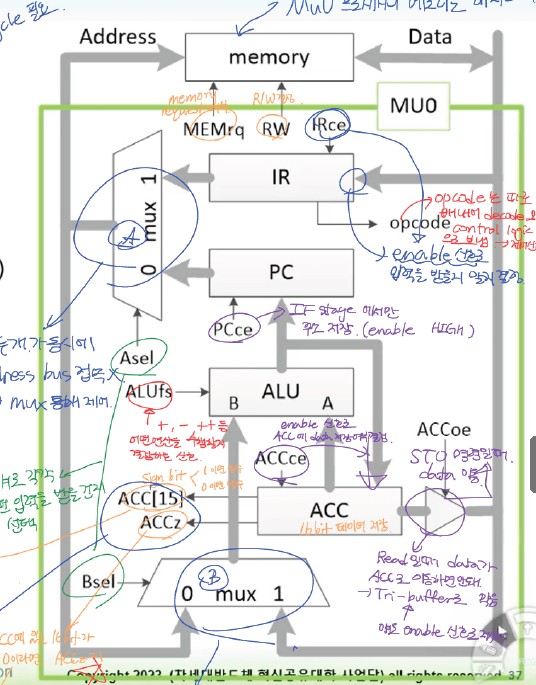

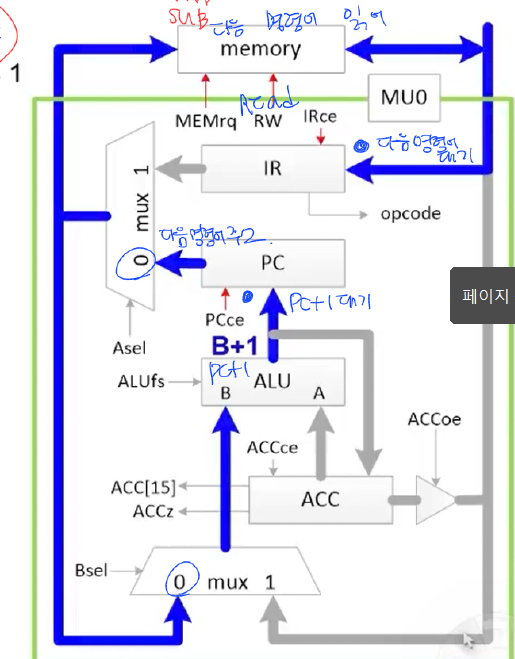

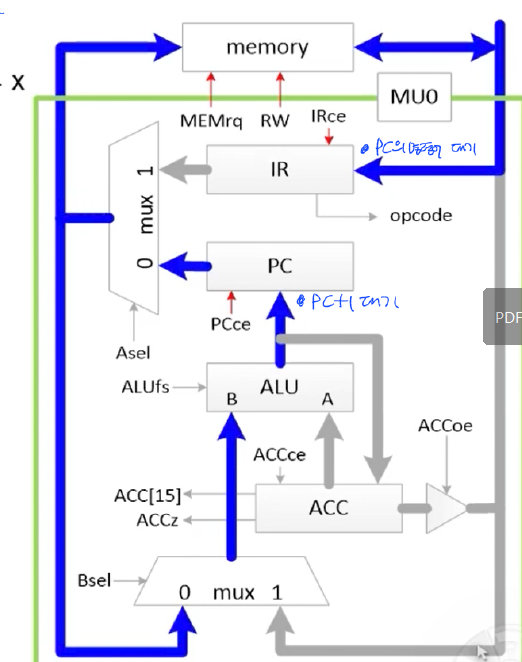

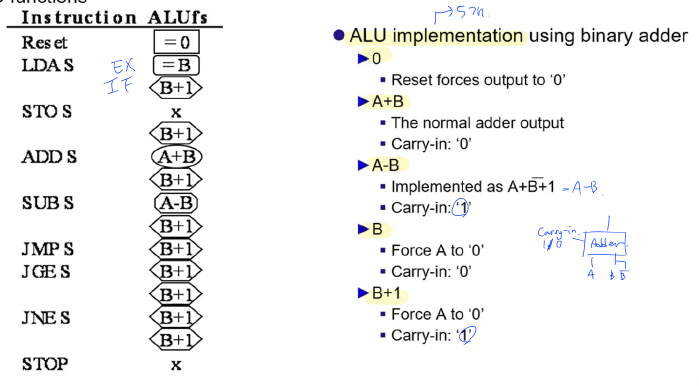

Datapath operation

- EX : Execute

- 실제로 동작을 수행하는 단계

- IR의 주소가 다뤄짐(data의 주소가 address bus 이용함)

- ADD, SUB, LDA, STO

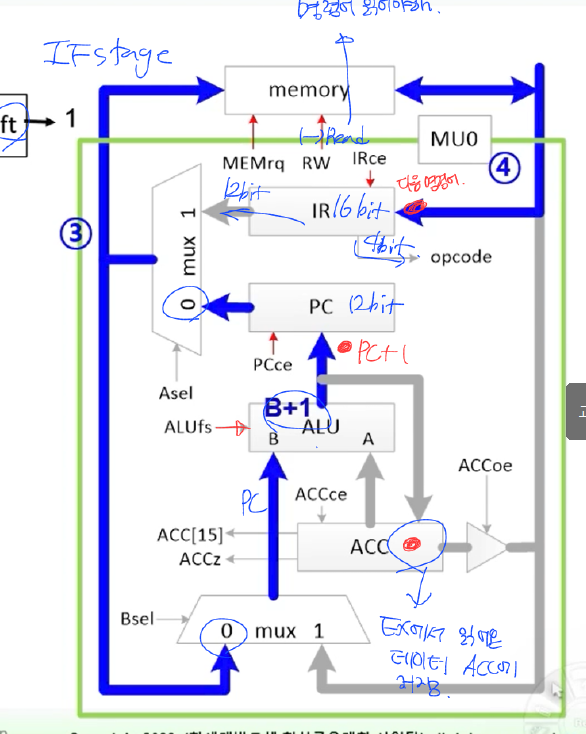

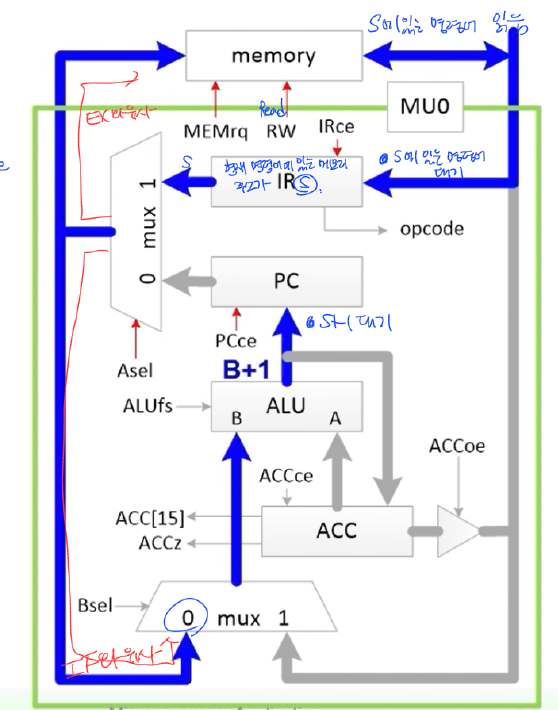

- IF : 명령어 fetch 단계

- JMP 등에 있는 S나 PC를 읽어오는 단계 (명령어의 주소가 address bus 이용)

- 명령어를 읽어오면서 다음 명령어의 주소 연산을 동시에 함(ALU에서)

- JMP, JGE, JNE, STP는 IF 단계만 있어

- IF단계에서 명령어를 읽어올 때, 바로 IR에 저장되는게 아님

- IF단계가 끝나면 IR 바로 앞에 명령어가 오는데 EX단계가 실행될 때 IR의 enable 신호가 켜지면서 명령어가 IR에 들어가고 그때부터 명령어 처리가 시작됨

Initialization

- 프로세서는 반드시 알고 있는 상태부터 실행되어야해

- Reset input → 0x000 번지에서부터 명령어를 시작하게 함.

- ALU 출력이 0 → 0을 PC에 넣음으로서 수행할 수 있음

MU0 Control signals

Datapath control signals

- Asel : IR과 PC 중 하나 선택

- Bsel : PC나 data 둘 중 하나 선택

- ACCce : ACC enable 신호 → ACC에 데이터 저장 여부 결정

- PCce : IF 단계에서만 주소 저장 (IF 단계에서만 enable HIGH)

- IRce : IR에 정보 받을지 말지 결정

- ACCoe : ACC에서 메모리로 정보 보낼지 말지 결정

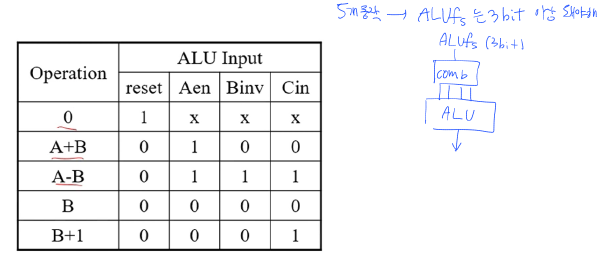

- ALUfs : ALU에서 어떤 연산할지 결정

Memory interface signals

- MEMrq : 메모리 접근 여부

- RW : R/W 결정

control logic state

EX/ft : execute(0)/fetch(1)

datapath로부터 받은 control logic의 입력

- opcode : operation code (4bit)

- ACC[15] : ACC의 양/음

- ACCz : ACC 0 여부

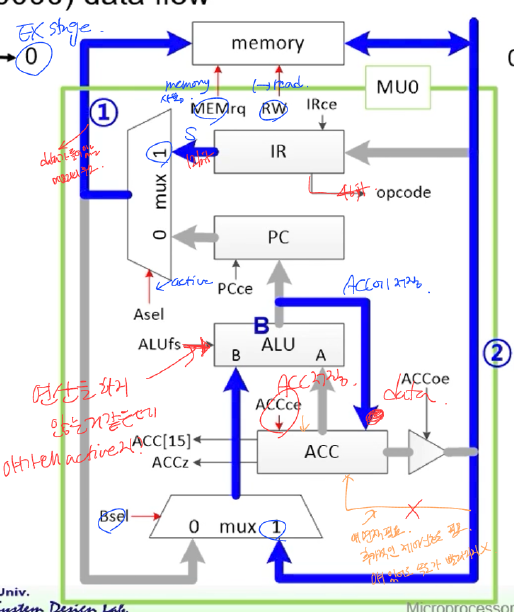

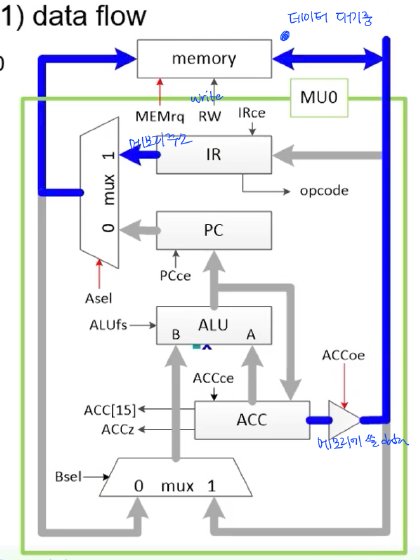

LDA(0000) data flow

★ 레지스터나 메모리에 data가 저장되기 직전에 stage 종료

★ IF stage는 LDA, STO, ADD, SUB 모두 동일 동작

1. ex stage

- 다음 명령어 IR에 들어감

- loaded data가 ACC 앞에서 머물러

- ft stage

- 다음 명령어 IR 앞에서 머물러

- 연산된 PC+1이 PC 앞에서 머물러

- loaded data가 ACC에 들어감

STO(0001) data flow

- ex stage

- IF stage

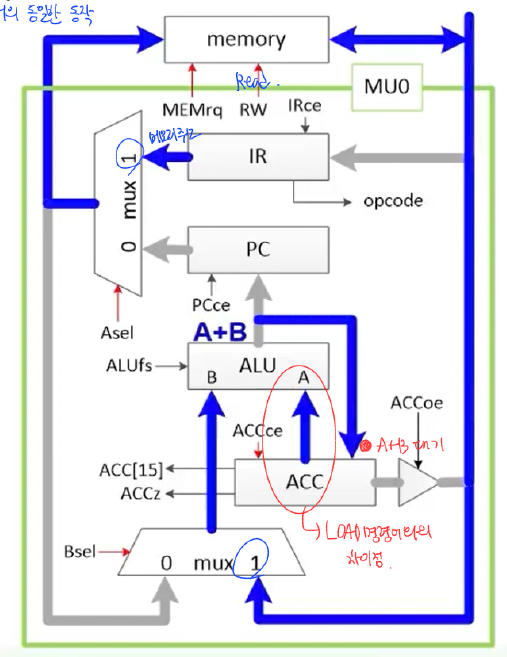

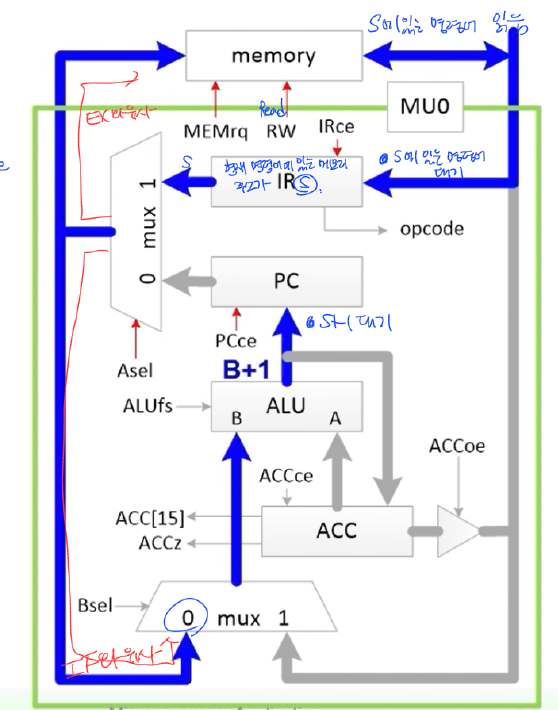

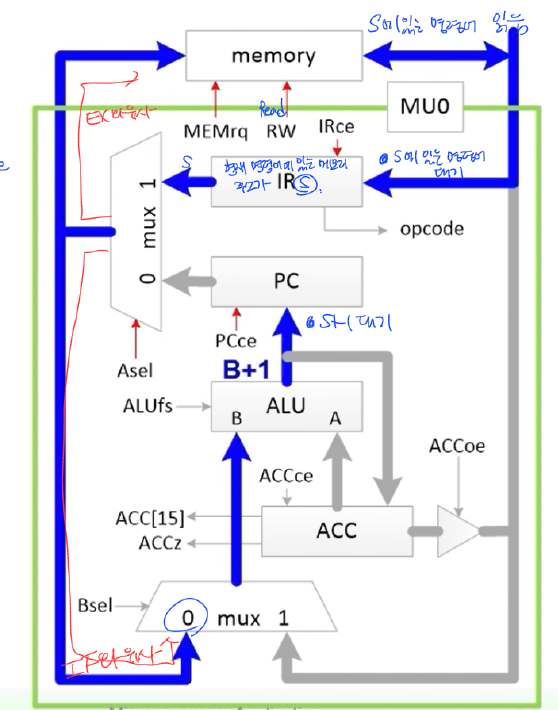

ADD(0010) data flow

- LDA와 거의 동일한 동작

- 메모리에서 불러온 값과 ACC에 있던 값을 더함

- ex stage

- LDA 명령어와의 차이점 : ALU에 ACC에 있던 값이 들어감

- if stage

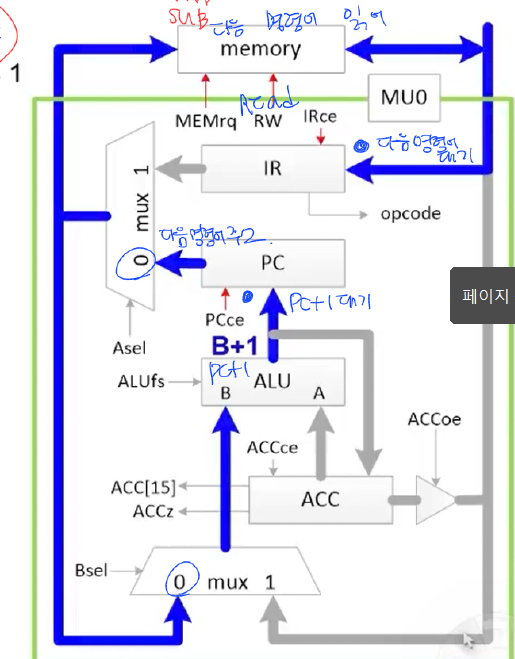

SUB(0011) data flow

- ex stage

- if stage

JMP(0100) data flow

- jump 계열과 stop 명령어는 1 사이클

- S 주소에서 명령어를 읽어옴과 동시에 S+1 주소 계산

JGE(0101) data flow

- 두 조건에서의 동작의 차이는 그저 주소가 S인지 PC인지 밖에 없음

- ACC[15] = 0 → Jump

- ACC[15] = 1 → 다음 명령어 fetch

JNE(0110) data flow

- ACCz = 0 → Jump

- ACCz = 1 → 다음 명령어 fetch

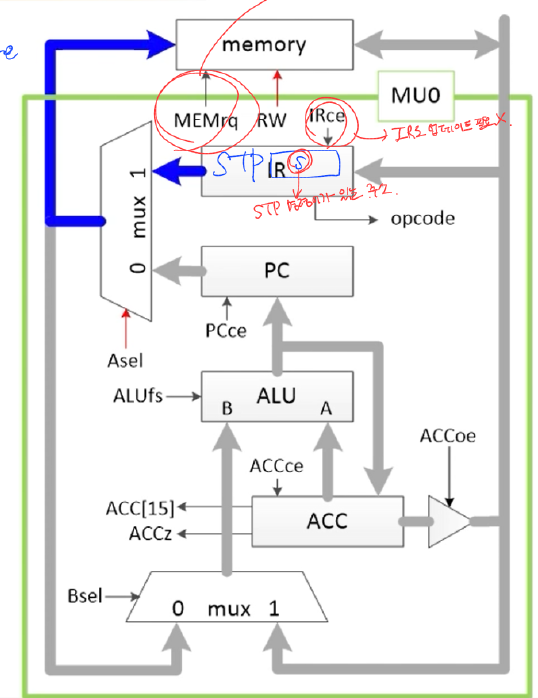

STP(0111) data flow

- MEMrq를 꺼줘 → STP 명령어 계속 읽어줄 필요 없음

Control logic

- opcode, ACC[15], ACCz, CLK, Reset 신호를 받아 연산한 후

- Datapath contril signals와 memory control signals 생성

ALU functions

ALU design

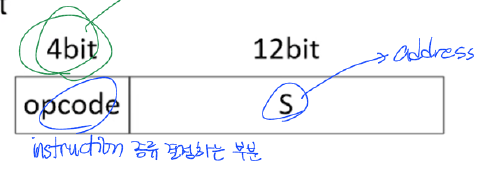

MU0 - assembly coding example1

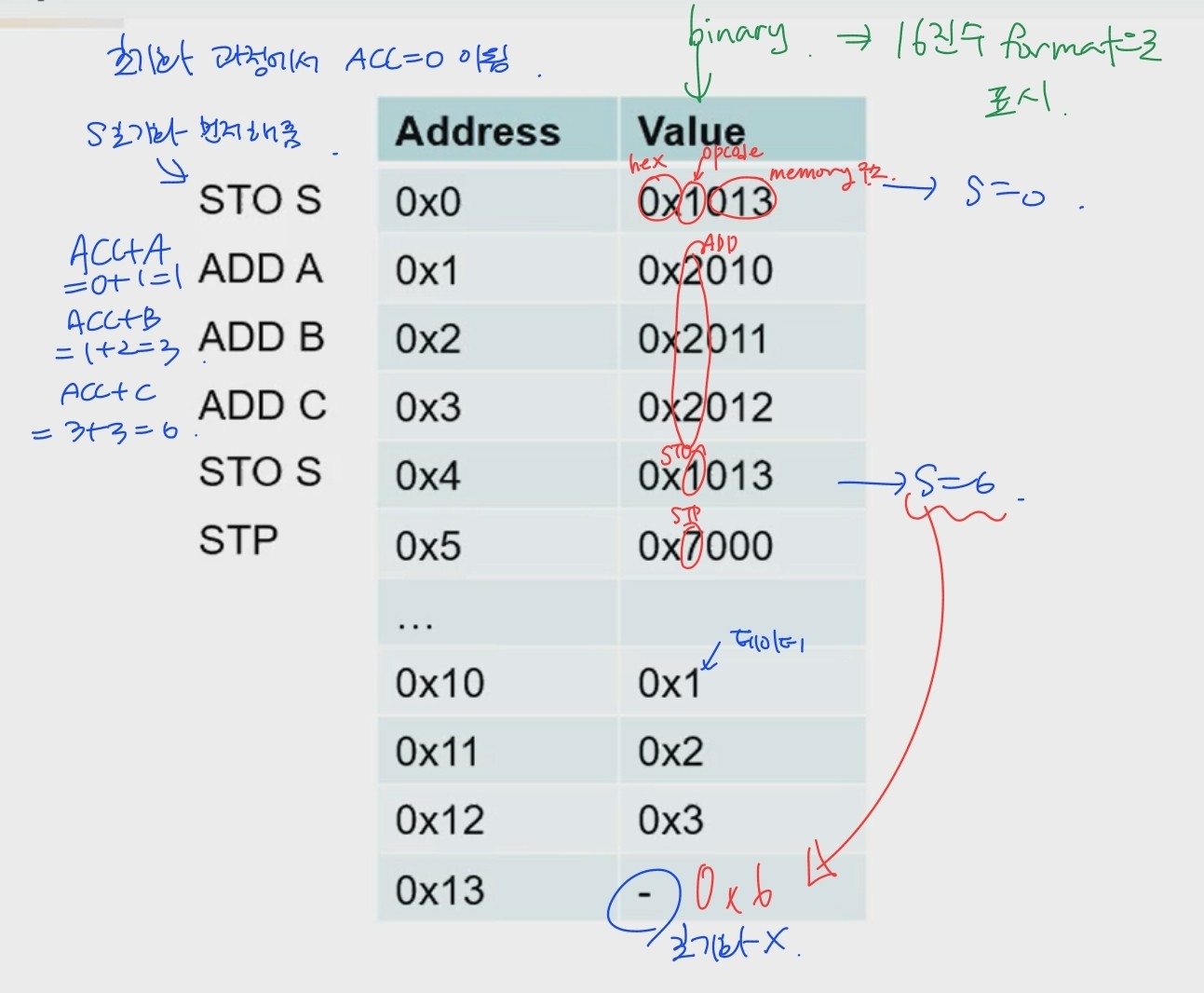

Summation

MU0 - assembly coding example2