1. Computer Systems Architecture

Stored-Program Concept

- code와 데이터는 모두 memory에 저장되어있어 Fetch-Decode-Execute(FDE) cycle을 통해 instruction을 memory에서 읽어오고 수행한다.

- von Neumann Architectrure (1945)

- Hardware-Defined (ENIAC) vs Software-Defined (EDVAC)

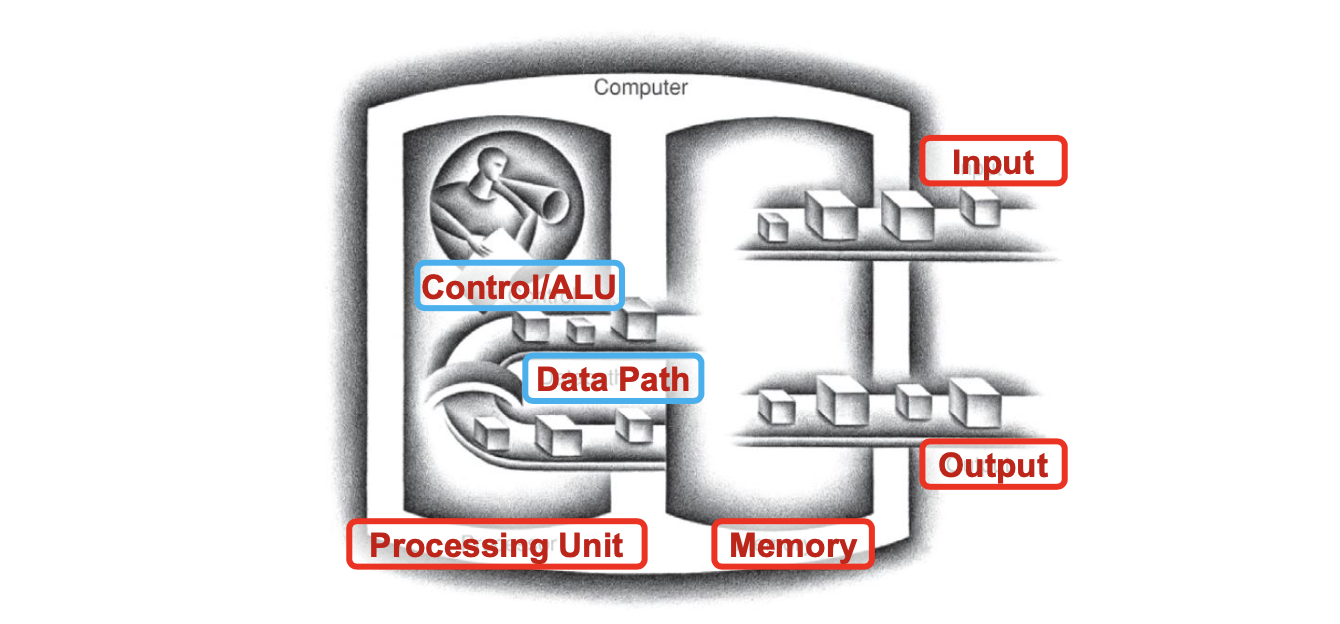

Components inside Computer

- Processing Unit (Control/ALU)

Instruction에 따라 data path, memory, I/O device를 control한다. Instruction Register, Program Counter(PC)와 같은 register들을 포함한다. - Memory

수행중인 프로그램과 필요한 데이터들을 저장하는 storage area - Input/Output

User-interface devices, Storage devices, Network adapters

cf) I/O device controller - Data path

각 component들 사이에 data, instruction을 주고 받는 pathway

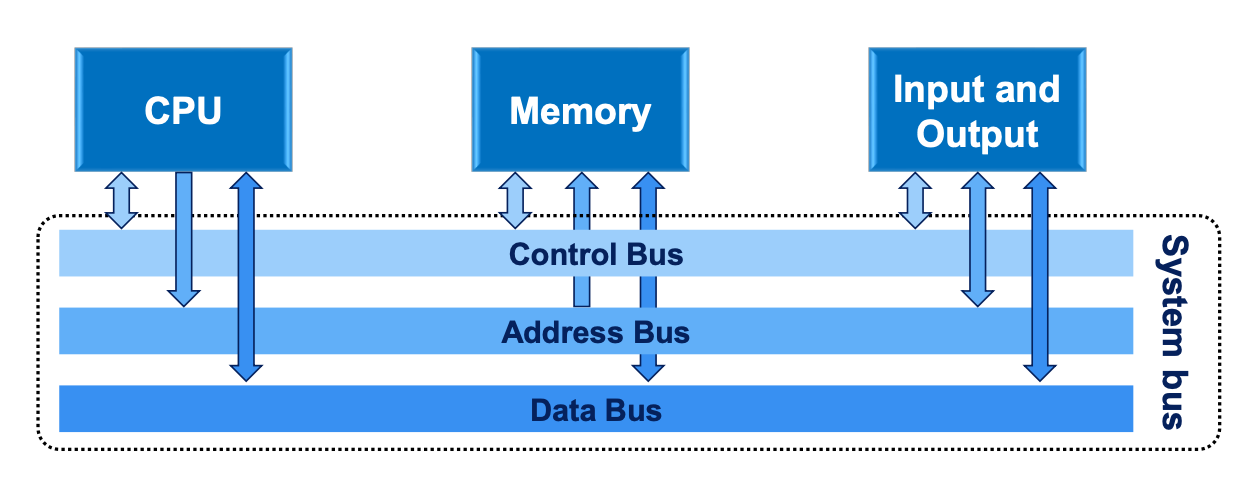

System Interconnect

- System bus / Data path는 Computer system의 component들을 연결한다.

- Control bus는 command와 status signal을 전달한다. Address bus는 data transfer를 위한 주소, Data bus는 data를 전달한다. Reda/Write 두가지 action은 indivisible하다.

- Bus Master vs Bus slave vs Bus Arbiter

Bus master는 bus request signal을 보내 bus transaction을 initiate한다. Bus Arbiter는 shared resource인 system bus를 exclusive하게 쓸 수 있도록 bus request signal을 받아 할당하고 bus grant signal을 전달한다. Bus Slave는 master로부터 bus transaction을 수행한다. 일반적인 경우 CPU가 bus master, memory와 I/O device는 bus slave가 된다. DMA Controller는 bus master의 역할을 수행한다.

I/O Operations

- Local Register인 Data Register (Input Register, Output Register), Control Register (Control Register, Status Register)와 Local Buffer를 가지고 있다.

- CPU의 command를 받아 I/O device controller는 I/O operation을 수행한다. Status register를 확인하여 data register가 available한지 확인 후, data를 data register에 command를 control register에 저장한다.

- Polling I/O vs Interrupt-driven I/O

I/O operation이 끝날때까지 CPU가 cycle을 돌며 data register를 확인하는 Polling I/O 방식과 I/O operation이 끝나면 CPU에 interrupt를 보내는 Interrupt-driven I/O 방식이 있다. - Memory-mapped I/O vs Port-mapped I/O

Memory-mapped I/O는 memory address space에 I/O register를 mapping하여 똑같은 system bus와 instruction을 사용하는 방식이다. Port-mapped I/O는 별도의 I/O address space를 이용하여 special bus와 instruction이 필요하다. - DMA (Direct Memory Access)

CPU는 DMA controller에게 command, 시작 address, size만 전달하면 device controller가 bus master로서 DMA를 수행하고 수행을 마치면 interrupt를 통해 CPU에게 알린다. 주로 block 단위의 I/O operation에 이용된다.

2. Interrupt Mechanisms

Interrupt Operation

- Interrupt란 Interrupt Service Routine (ISR)로 control을 넘겨주는 HW mechanism이다.

- HW interrupt (asynchronous) vs SW interrupt (synchronous)

- Interrupt Operation

1) 수행 중이던 instruction을 마친다.

2) Interrupt bit를 확인하고, 도착한 Interrupt가 있다면

3) PC를 비롯한 register들을 stack에 저장한다.

4) Interrupt vector table에서 IRQ (interrupt request number)에 해당하는 ISR address를 얻어 jump한다.

5) ISR를 수행하는 동안, 다른 interrupt를 놓치지 않도록 disable한다. ISR를 마치면, 저장한 PC로 돌아온다.

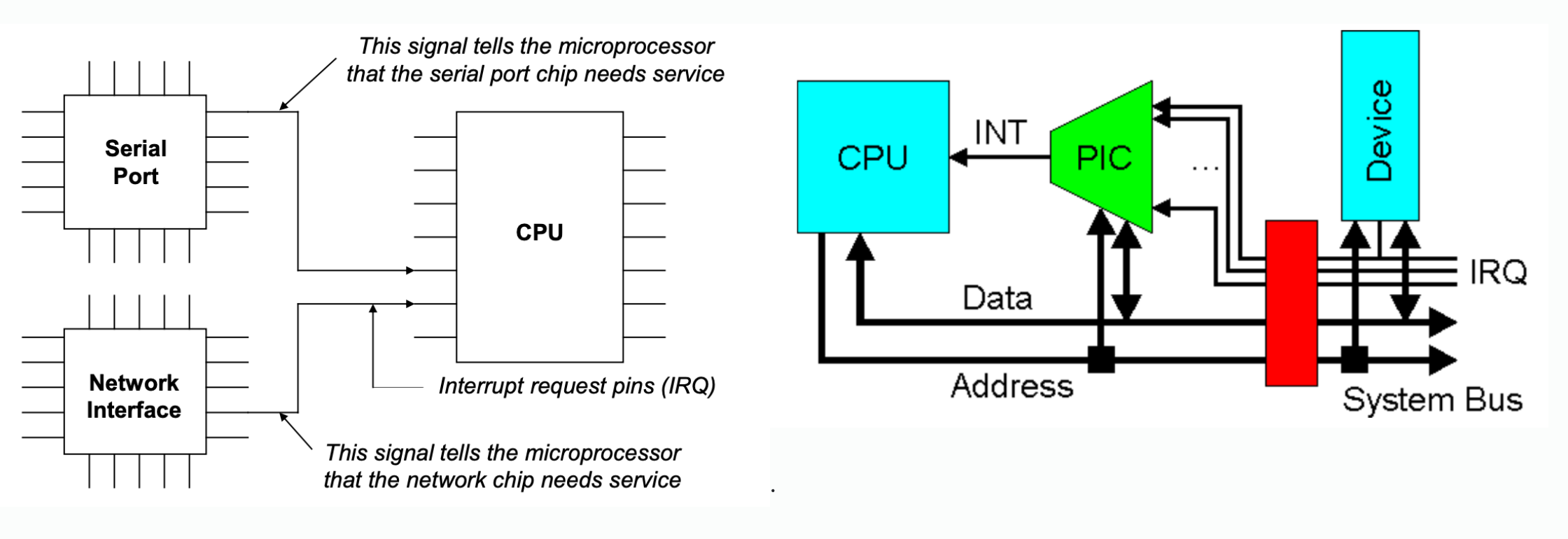

Interrupt Hardware

- Interrupt Source는 Interrupt Destination의 service가 필요할 때 HW적으로 signal을 전송한다.

- CPU가 IRQ number만큼 HW pin을 가질 수 없다. 따라서, manager 역할을 하는 PIC (programmable interrupt controller)를 도입한다. PIC는 interrupt 도착 여부를 확인하는 interrupt pending register, interrupt masking 여부를 확인하는 interrupt mask register, interrupt 우선순위를 알 수 있는 interrupt request number register를 가진다.

- PIC operation

1) IRQ line을 확인한다. signal이 도착하면

2) interrupt 정보를 data bus를 통해 CPU에 전달할 수 있도록 interrupt controller I/O port에 저장한다.

3) INTR pin을 통해 CPU에게 interrupt가 발생했다고 알린다.

4) CPU가 acknowledge하면 INT line을 clear한다.

3. Hardware Protection Mechanisms

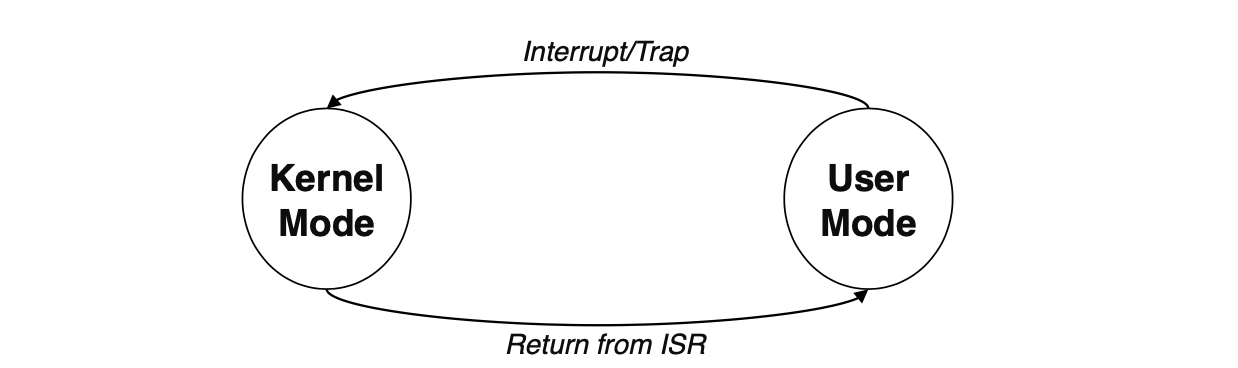

Dual mode operation

- system resource를 share하기 위해 User mode & Kernel Mode로 dual mode operation을 한다. Interrupt를 통해 user mode에서 kernel mode로 switch한다. Processor status register를 이용해 mode를 binary로 표현한다.

- system call : kernel function을 불러 kernel mode로 switch한 후 수행한다.

Protection

- I/O Protection

I/O operation은 모두 kernel mode에서만 수행가능한 privileged instructions - Memory Protection

Base Register와 Bound Register를 이용하여 프로그램이 접근할 수 있는 memory를 제한한다. - CPU Protection

한 프로세스가 CPU를 독점하지 않도록 timer를 이용하여 control한다.

Summary

1. Computer Systems Architecture

- Stored Program Concept

- Components : Processing Unit, Memory, I/O, Data Path

- System Bus : Control bus, Address bus, Data bus

- DMA

2. Interrupt Mechanisms

- Interrupt Service Routine (ISR)

- Programmable Interrupt Controller (PIC)

3. Hardware Protection Mechanisms

- Dual Mode : User & Kernel