이번 글에서는 modeling기법에 대해서 얘기하고자 합니다. 총 4가지이고 아래와 같습니다.

- gate level

- dataflow level

- behavioral level

- structural level

물론 기법을 3가지라고 하는 분들도 계십니다. structural level에 gate level을 포함시키느냐 마느냐의 차이긴 한데 이번 글을 읽어보시면 무슨 말씀이신지 이해가 가실겁니다.

저희는 이미 이전 글들에서 3가지 gate, dataflow, structural 기법을 다뤄보았습니다. 따라서 무엇인지만 이해하시고, behavioral level구문만 잘 익혀가시면 되시겠습니다.

해당 설계방식을 비교해드리기 위해서 full_adder를 예시로 가져왔습니다.

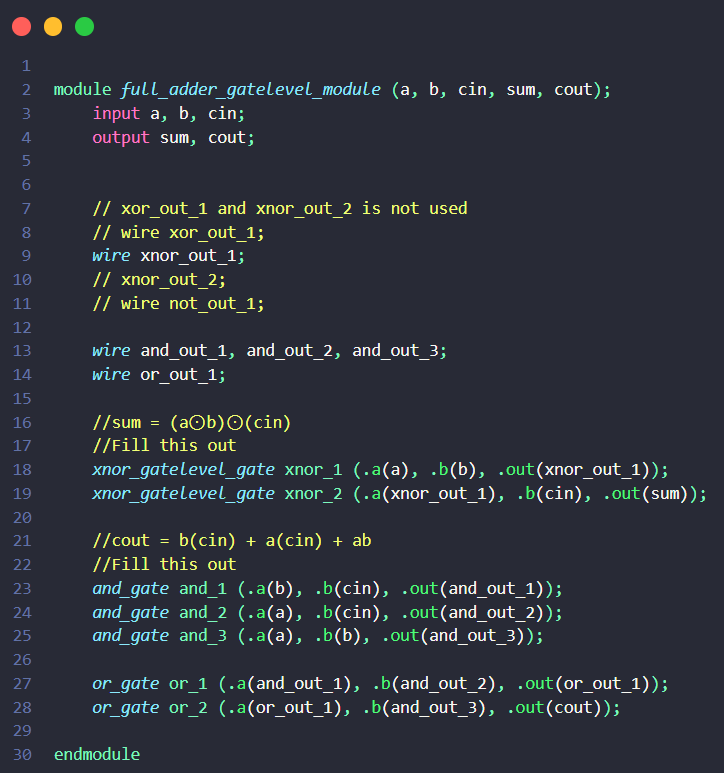

Gate level

gate level은 다음과 같습니다. 적당한 wire와 and, or, xnor과 같은 기본 gate들을 instination해서 full_adder를 설계하였습니다. 이런 경우를 gate level이라고 합니다.

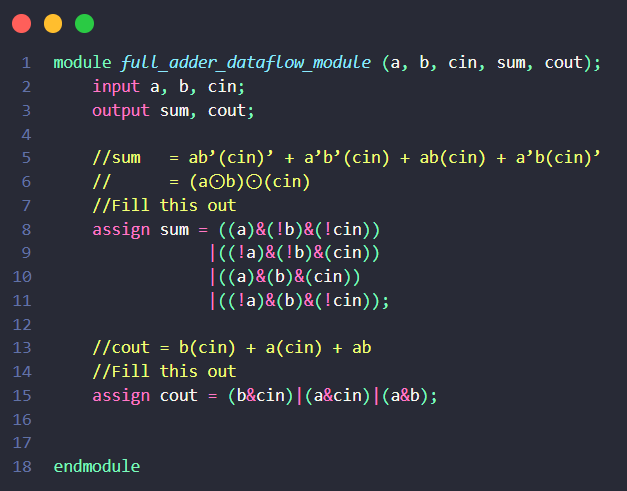

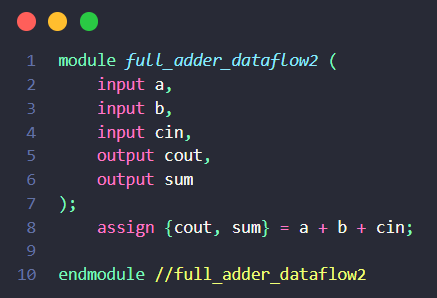

Dataflow level

dataflow level은 다음과 같습니다. 기존의 논리회로에서 boolean expression을 뽑아내어서 logic을 설계하였는데 저희가 가지고 있는 operator와 asign구문을 이용해서 설계하는 경우 dataflow level이라고 부릅니다. 참고로 저희는 add연산자인 +를 알고있습니다. 따라서 아래와 같이 적어도 dataflow level이라 할 수 있습니다.

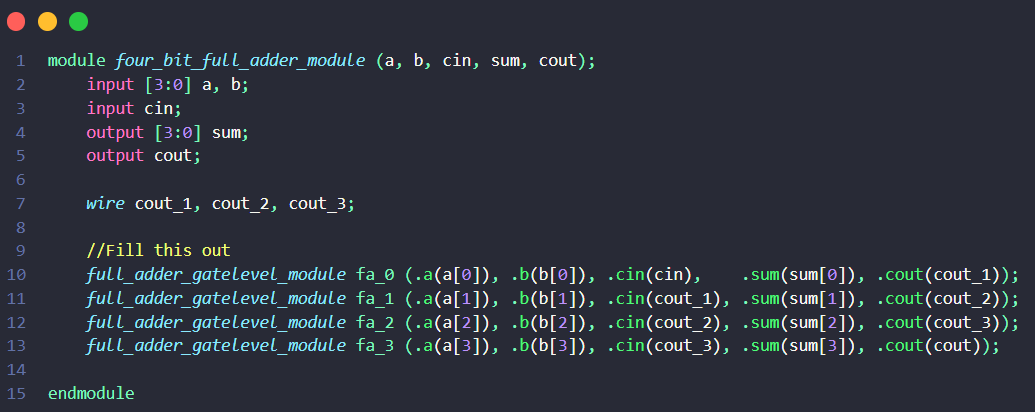

Structural level

Structural level을 설명하기 위해서 위와는 다르게 4bit full adder를 가지고 왔습니다. 기존에 존재하던 full adder를 instination하여서 4bit full adder를 설계하였고 이렇게 작은 module을 instination하여 큰 module을 설계할 때 structural modeling이라고 부릅니다. 생각해보면 기존의 gatelevel도 어떻게 보면 and, or, xnor과 같은 gate들을 instination하니까 그것도 structural level이라 부를 수 있습니다.

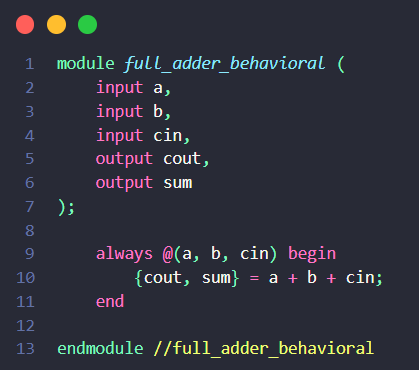

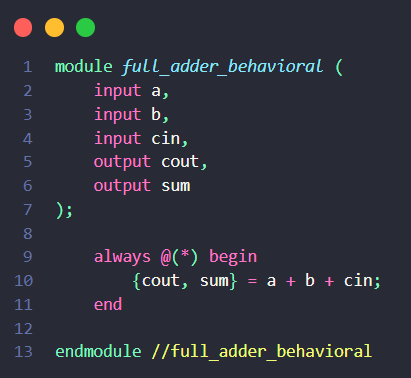

Behavioral level

마지막으로 behavioral level modeling에 대해서 얘기를 해야합니다. 어떻게 보면 해당 내용이 이번 글에서 가장 중요하고 잘 다뤄나야 하는 부분입니다. 일단 먼저 말씀드릴 내용은 해당 구문이 어떻게 보면 Verilog를 가장 c와 유사하게 만들어주는 언어이고, 가장 사용자의 편의성을 올려주는 구문입니다. 참고로 앞으로 대부분의 코드는behavioral modeling을 사용해서 작성할 예정입니다.

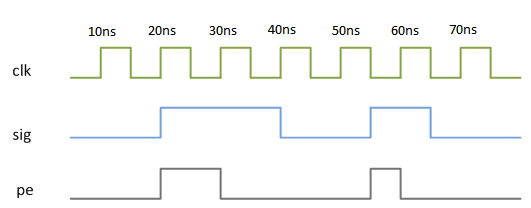

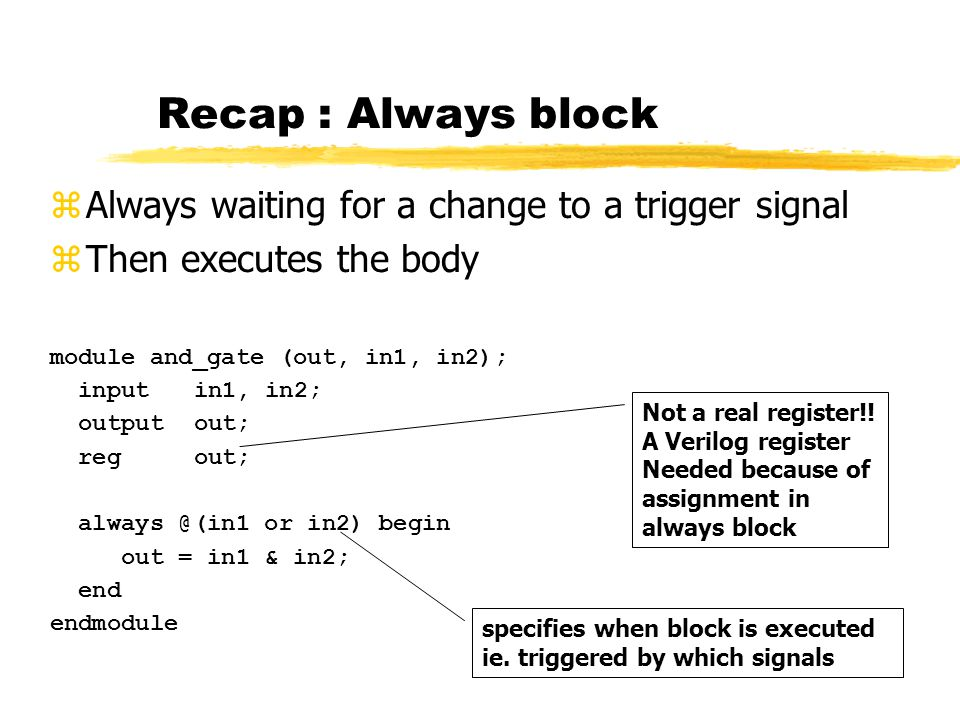

behavioral level modeling을 배우기 위해서 저희는 always구문이라는 문법을 배워야합니다. always구문은 말 그대로 '항상'수행되는 구문인데 무조건인것은 아니고, @뒤에 괄호 내부(해당 예시에서는 a, b, cin)의 값이 변경될 때마다 수행이 되는 구문을 의미합니다.

Verilog에서는 이렇게 값이 변경되는 것을 event라 부르고, 괄호 내부 값들을 sensitivity list라고 부릅니다. 다시 정리하자면 sensitivity list의 변수에 event가 발생할 경우 always구문이 수행됩니다.

always구문은 begin과 end로 경계를 구분합니다. 이는 c언어의 {}와 같은 역활이라고 생각하시면 됩니다.(Verilog에서 중괄호는 이전에 말씀드린 concatenation에 사용되기 때문에 대신 사용한다고 보시면 됩니다)

예시를 들자면 a, b, cin이 모두 0을 유지하고 있다가 a의 값이 1이 됩니다. 그럴 경우에 a에 event가 발생하였고, a를 sensitivity list에 포함하고 있는 해당 {cout, sum} = a + b + cin이라는 구문이 수행된다고 생각하시면 됩니다.

참고로 always구문의 sensitivity list는 로 대체할 수 있습니다. compiler가 알아서 체크해주기 때문에 combination구문을 설계할 경우 직접 sensitivity list를 기술하는 것보다는 를 사용해주시기 바랍니다.

그런데 이것만 들으면 아직 왜 behavioral을 사용하는지 납득이 안가실 겁니다. behavioral의 장점은 내부에서 c언어에서 사용하는 많은 문법들을 사용할 수 있다는 점입니다. 바로 if문, case문과 같은 것들을요. 이것들로 인해서 Verilog사용자는 c코딩과 '유사'하게 logic을 빠르게 설계할 수 있고, 내부 hierachy에 대한 이해를 좀 더 감출 수 있습니다.

이에 대한 내용은 다음 글에서 이어나가겠습니다.