안녕하세요

HDLBits의 Basic의 마지막편을 작성해보려합니다.

(사실 어렵지 않아서 금방 끝나는 거 같아요 ㅋㅋㅋ)

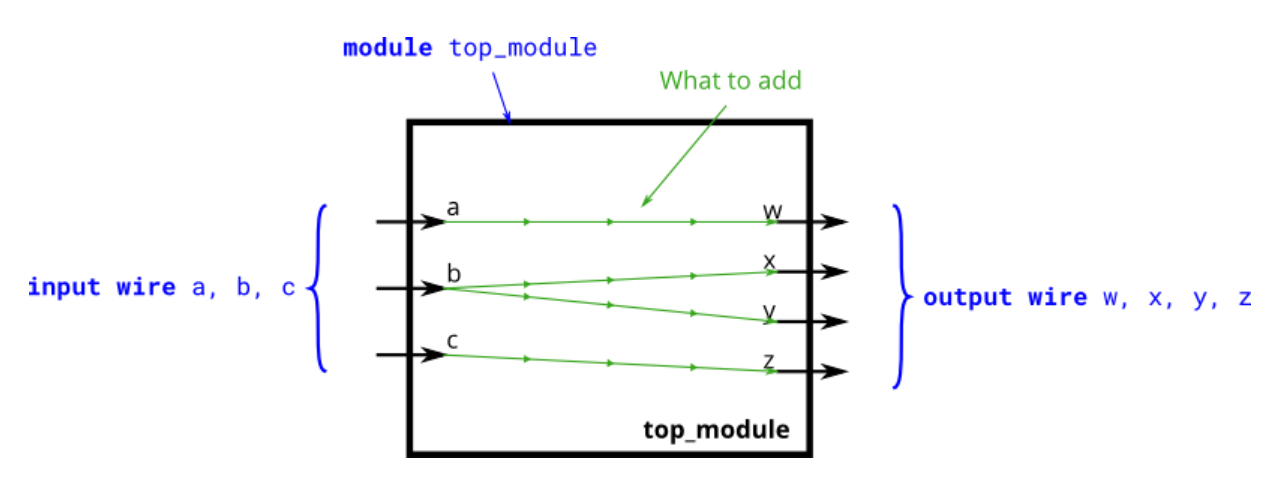

Wire4

이번에 풀어볼 문제는 아래와 같은 circuit을 만들면 됩니다.

여러분들도 어렵게 않게 할 수 있습니다.

assign문을 사용하면 그 wire간의 연결을 잘 정의해줄 수 있습니다.

단 주의할 점은 C/C++과 같이 프로그래밍 언어에서 값을 복사한다는 개념이 아닙니다.

회로적으로 바라보는게 맞겠습니다.

학부 때 회로이론을 배울 때 node voltage라는 것을 배웠지요?

a지점 마디 전압이 5V인 것을 w에 전선으로 이어준다라고 생각하면 좋겠습니다.

전선으로 이어주니까 동일한 마디 전압을 가지겠지요?

이 둘이 서로 관련이 없어보이지만, 같이 접목해서 생각해본다면 코드를 작성할 때 머리 속에서 그려질 것 같습니다.

module top_module(

input a,b,c,

output w,x,y,z );

assign w=a;

assign x = b;

assign y = b;

assign z = c;

endmodule

이렇게 작성해면 그림과 같이 circuit을 기술할 수 있습니다.

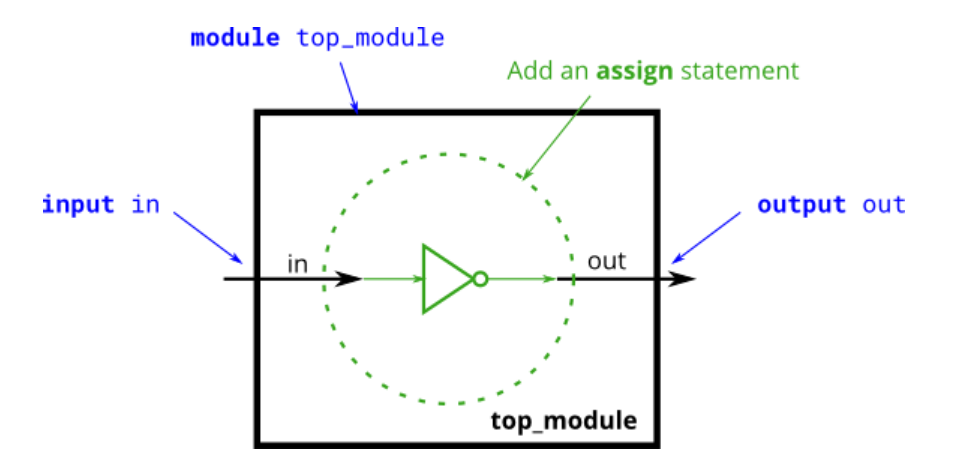

Inverter

자 이번에는 Inverter라고 불리는 NOT gate에 대해 빠르게 다루어 보겠습니다.

NOT gate의 심볼은 아래와 같습니다.

이 NOT gate의 역할은 A를 반전시킨 A'을 출력해주는 것인데요, 나중에 이를 이용해서 SRAM을 만들기도 합니다...

(왜 갑자기 SRAM이야...하시겠지만,, 나중에 다뤄보겠습니다..)

자 A를 반전시킨 A'이 무엇이냐?

입력을 1'b1을 주면 출력으로 1'b0이 나오고,

입력을 1'b0을 주면 출력으로 1'b1이 나온다는 말입니다.

원리는 정말로 간단하죠?

자 근데 어떻게 5V를 0V로 바꾸고 0V를 어떻게 5V로 바꾸냐.... 하는 분들도 있을 겁니다.

자.. 처음에 NOT gate의 심볼이 저렇게 생겼다고 했습니다.

실제로는 NOT gate에도 VDD와 GND를 인가해줘야한다 이말입니다.

아마 학부 때 gate IC chip으로 실험을 해보신 분들이라면 바로 알 수 있을 겁니다.

자 말이 길어졌네요.

위에 보이는 circuit을 만들기는 참 쉽겠죠?

input, output사이에 inverter(NOT gate)를 배치해주고 연결하면 끝납니다.

말은 이런데 assign문을 통해 작성하면 그냥 한 줄이면 끝납니다.

module top_module( input in, output out );

assign out = ~in;

endmodule

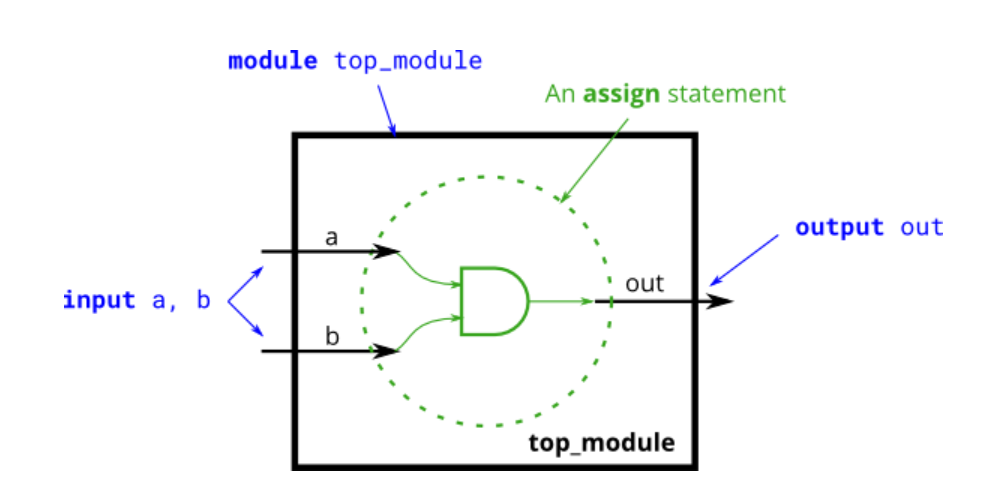

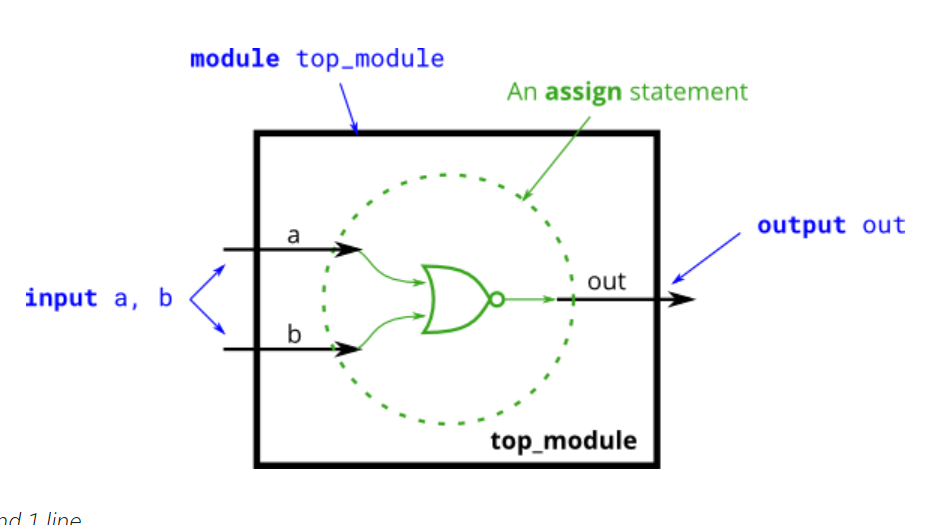

AND gate

이번에는 AND gate를 다루어보겠습니다.

이것 또한 어려운거 1도 없습니다.

AND gate는 하나라도 0이 입력으로 들어오면 출력은 0이 됩니다.

AND gate의 역할은 부울대수적으로 본다면 곱하기 입니다.

우리 산술계산할 때 0xX 하면 그 결과는 X에 상관없이 0이 되죠?

AND gate가 그런 연산이라는 겁니다.

자 심볼을 보겠습니다

자 이걸 이제 Verilog로 기술해봅시다.

module top_module(

input a,

input b,

output out );

assign out = a & b;

endmodule

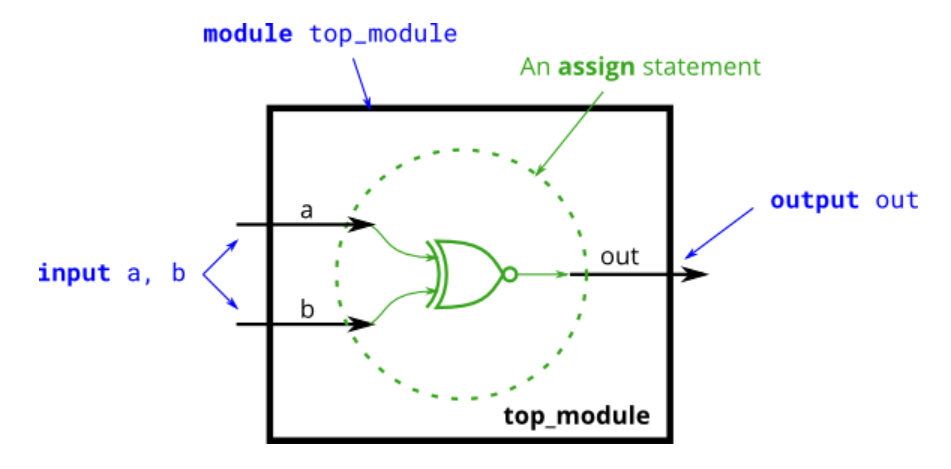

NOR gate

자 NOR gate에 대루어 봅시다.

사실 NOR gate를 다루기 전에 OR gate를 먼저 알면 좋습니다.

OR gate는 입력이 하나라도 1이라면 출력은 1입니다.

그리고 부울대수적으로는 더하기이지요.

자 우리는 bit wise하게 생각하면 지금 편합니다.

십진수도 아닌 이진수도 아닌

자 1+1=1????

1bit 세상에서는 그렇습니다...

nbit이라면 올림수가 발생해서 1+1=10(2)가 되어서 LSB가 0이 됩니다.

하지만 지금 우리 bit단위로 보고 있지요?

이 말을 하는 이유는 나중에 헷갈리지 말라는 겁니다.

자 다시 본론으로 돌아와서 NOR gate에 대해 생각해봅시다

OR gate 앞에 NOT gate가 붙은 녀석이 NOR gate입니다.

NOR gate는 OR gate의 결과를 뒤집은 녀석입니다.

지금 우리는 진리표를 보면서 공부하는 시간은 아니니... 궁금하신 분들은 GATE의 진리표를 확인하길 바랍니다...

(절대 귀찮아서 그러는 거 아닙....맞아요)

위의 NOR gate를 Verilog로 기술해봅시다.

module top_module(

input a,

input b,

output out );

assign out = ~(a|b);

endmoduleXNOR gate

XNOR gate는 XOR gate를 안다면, 쉬운 녀석입니다.

XOR가 무엇인가요? 입력이 서로 같으면 출력은 0입니다.

거기에 NOT을 한 녀석이 XNOR입니다.

자 그렇다면 바로 Verilog로 기술해봅시다

module top_module(

input a,

input b,

output out );

assign out = ~(a^b);

endmodule

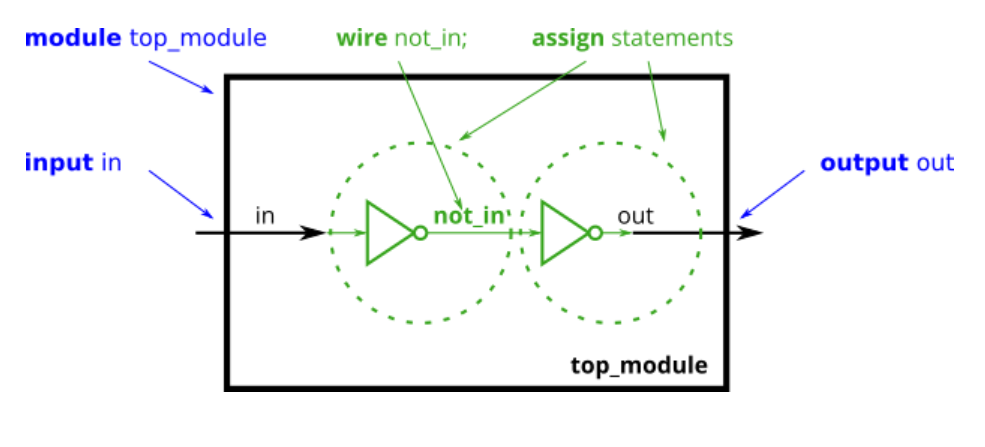

Declaring wires

자... 솔직히 지금까지 너무 easy했다 그렇죠?

그래서 조금 더 난이도를 올리기 위한 문제를 풀어봅시다

우리 모듈을 입력과 출력으로 만들지만, 그 내부는 수 많은 logic들로 이루어져 있겠지요?

이 때 wire로 중간중간 연결을 해준다면 내부를 조금 더 깔끔하게 기술할 수 있습니다.

assign b = a&b^c|q;이런식으로 한번에 작성해도 괜찮지만, 때에 따라서 이렇게 하는 것 보다는 wire를 중간에 선언해주면서 코드를 작성하는게 좋았던 것? 같습니다.

이 정도는 여러분들 충분히 할 수 있을거라 생각합니다.

module top_module (

input in, // Declare an input wire named "in"

output out // Declare an output wire named "out"

);

wire not_in; // Declare a wire named "not_in"

assign out = ~not_in; // Assign a value to out (create a NOT gate).

assign not_in = ~in; // Assign a value to not_in (create another NOT gate).

endmodule // End of module "top_module"충분히 그 예시를 설명해주고 있네요

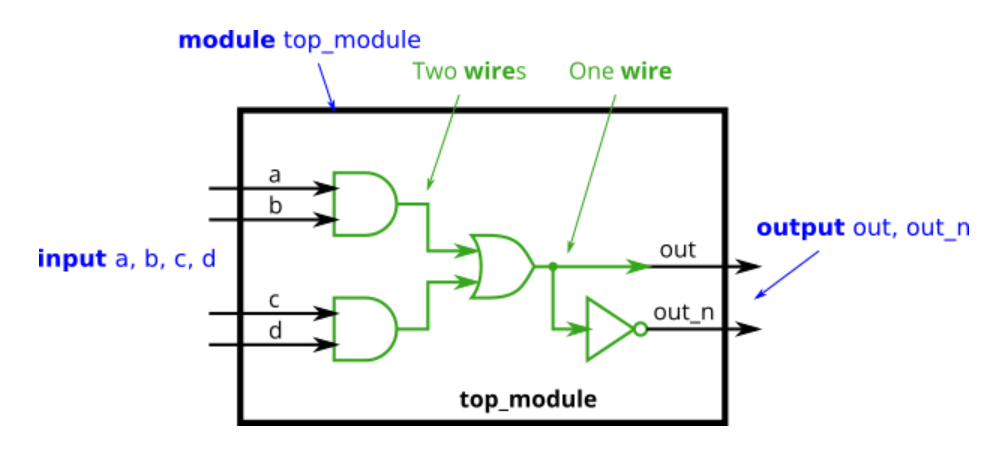

그럼 문제로 들어가봅시다.

자 문제에서 친절하게 wire 이름도 알려주네요.

가끔 변수 이름 지정해주는 것이 시간이 걸릴 때가 좀 있습니다..

(물론 저런식으로 Two wires, One wire으로 하면 개구대기 같습니다)

`default_nettype none

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire [1:0]Two;

wire One;

assign Two[0] = a&b;

assign Two[1] = c&d;

assign One = Two[0]|Two[1];

assign out = One;

assign out_n = ~One;

endmodule

어때요 참 쉽죠?

네 정말로 쉬워야 합니다...여기까지는

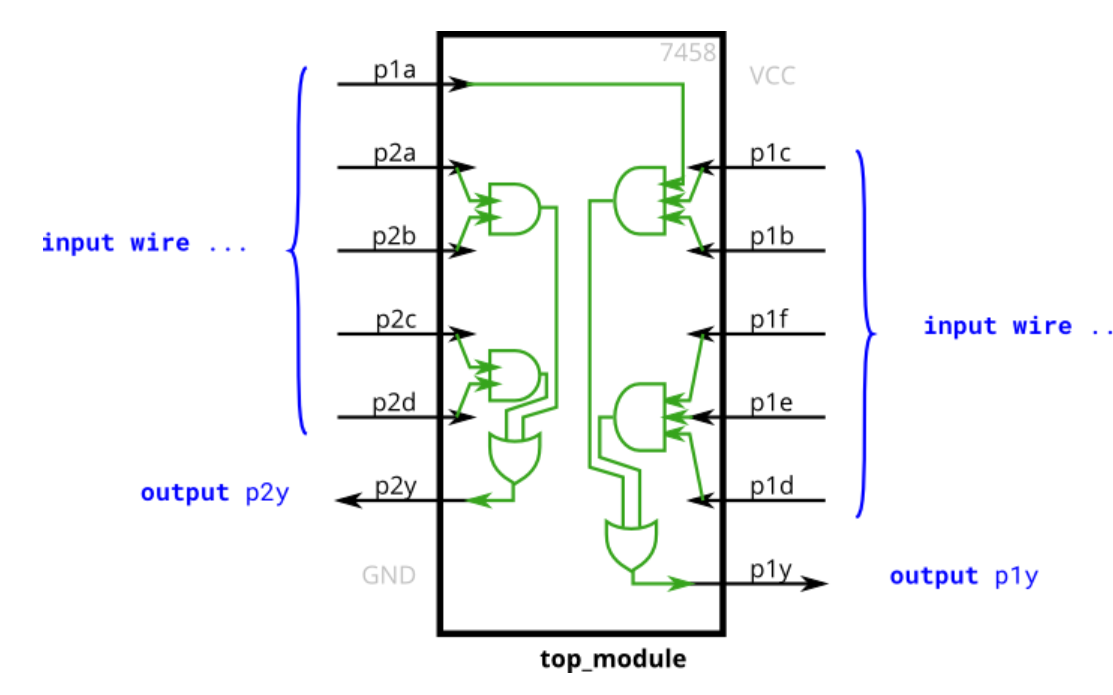

7458 IC chip

이번에는 7458이라는 IC chip내부를 기술해봅시다.

이 내부에는 4개의 AND gate와 2개의 OR gate가 있다고 합니다.

자 이정도도 금방할 수 있습니다

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p2y = (p2a&p2b)|(p2c&p2d);

assign p1y = (p1a&p1b&p1c)|(p1d&p1e&p1f);

endmodule

네 이렇게 HDLBits Basic편을 빠르게 다루어 봤습니다.

어떤가요?

아마 완전 처음 접하시는 분은 조금 생소할 수 있을 것 같습니다.

하지만 저랑 함께 HDLBits를 풀어본다면 금방 따라 오실 수 있을겁니다.