이번에는 Vectors편에 대해 다뤄보도록 하겠습니다.

Declaring Vectors

Vectors는 관련된 신호들을 묶을 때 사용하면 편리한 Type입니다.

우리가 간단하게 32bit signal을 보낼 때

wire a0;

wire a1;

wire a2;

.

.

.

.

wire a31;이런식으로 32개를 선언하면 힘들겠지요.

이럴 때 사용하면 좋은 것이 바로 Vector입니다.

간단하게

wire [31:0] a;라고 해주면 32bit짜리 wire를 한번에 만들 수 있습니다.

단순히 wire로 선언할 때 말고도, input, output을 선언할 때도 가능하니

적절하게 써주면 엄청 편리합니다.

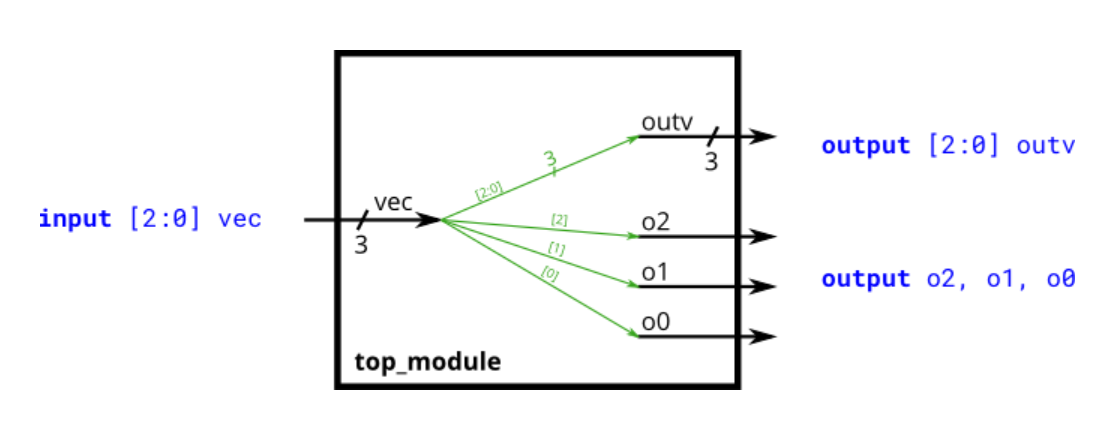

이번 Vectors 파트의 첫번째 문제는

이런식으로 만들어라 입니다.

참 간단하죠?

module top_module (

input wire [2:0] vec,

output wire [2:0] outv,

output wire o2,

output wire o1,

output wire o0 ); // Module body starts after module declaration

assign outv = vec;

assign o2 = vec[2];

assign o1 = vec[1];

assign o0 = vec[0];

endmodule이렇게 작성하면 끝납니다. 정말로 간단합니다.

자 그럼 우리 조금 더 응용하는 문제를 함께 풀어봅시다.

이번 문제는 Vectors in more detail이라는 문제인데요.

제가 생각하기에 기초적인 내용 중에서 정말로 top3에 드는 정도로 중요한 내용이라고 생각합니다.

위에서 32bit 크기를 가지는 변수를 선언할 때,

wire [31:0] a;이렇게 선언했었지요.

이제 이걸 선언하는 여러가지 방식에 대해 다루어 봅니다.

예시로는

wire [7:0] w; //8bit wire

reg [4:1] x; //4bit reg

output reg[0:0] //1bit reg and it is also output port 여전히 vector라고 합니다

input wire [3:-2] z; //6bit wire input(negative ranges are allowed)

output [3:0] a; //4bit output wire

wire [0:7] b; //8bit wire b[0] is MSB이 부분에서 저도 생소한 것은 바로 input wire [3:-2] z 부분인데요,

실제로 쓴 경험은 없습니다만, 있다고 하니 코드 가독성을 위해 필요하다면 사용하면 될 듯합니다

(하지만 이거 쓰는거 1번도 본 적이 없음)

그리고 제가 처음에 혼동했던 내용은

output wire, output reg는 가능한데,

input wire, input reg에서 input reg는 올바른 문법이 아니라는 겁니다.

기본적으로 input, output을 선언하면 wire type으로 됩니다.

즉, input wire, output wire를 할 필요 없이 input, output으로만 선언해도 이미 wire type이라는 겁니다.

하지만 저는 이런 스타일 보다는 내부에 reg를 선언하고 이 값을 출력해야한다면

assign문으로 할당하는 스타일로 코드를 짭니다.

(이건 제 개인적인 취향입니다.)

네 그리고 wire[0:7] b로 선언했을때 주의할 점은 바로 MSB가 b[7]이 아닌 b[0]이라는 것입니다.

이 부분 헷갈리지 않도록 주의해야겠습니다.

Implicit nets

이 부분에서는 우리가 주의해야할 부분입니다.

Verilog를 이용해서 코드를 작성할 때 wire나 reg type의 변수를 선언하고 작성해야하는데, 그렇게 하지 않은 경우 코드상 오류가 발생하거나, 나중에 디버깅 하기 정말로 힘들어 집니다.

보통 우리가 코드를 작성할 때

reg [7:0] r_cnt;

wire [3:0] threshold_value;이런식으로 먼저 선언하면서 코드를 작성합니다.

하지만 만약에

wire [2:0] a,c //a is 3bit vector and b is 3bit vector

assign a = 3'b101;

assign b = a;

assign c = b;이렇게 위에서 wire를 선언하고 코드를 작성했다고 생각합시다.

b에 a의 값을 할당하는 assign 코드를 작성하면 보통 그 의도는 a의 3bit값이 b에 할당되는 것을 생각할 것입니다.

하지만 이런 경우, 문제가 발생합니다.

b는 따로 선언되지 않았기에 암묵적으로 1bit wire타입으로 선언됩니다.

그렇게 된다면 b에는 3'b101이 아니라 1'b1이 할당될 것입니다.

이것이 의도된 것이었다면 상관없겠지만, 그게 아니라면 정말로 힘들어지는 경우가 발생합니다.

사실 가끔씩 오타를 만들어서 혹은 a,b,c를 입력해야하는데 손가락이 미끄려졌다면...

흑흑 별로 생각하고 싶지 않습니다.

작은 module을 만드는 경우면 디버깅해서 찾는게 쉬울 수 있어도....

여러개의 sub module을 만들고 top module에 합친 상태에서 이것 때문에 오동작이 일어난다?

정신나갈겁니다...흑흑

(저는 그랬던 경험이 있습니다...하 64bit size wire이어야 하는데 잘못 입력해서 1bit으로 되었던... 네 저는 바보였답니다.)

아무튼 이런 경우를 혹시나 만들기 싫다

그럼 directive를 이용하면 됩니다.

나중에 다룰 것인데 c언어에서 #define #ifdef이런거 쓴 기억나시죠?

Verilog에서도 이런 지시어들이 있습니다.

`default_nettype none이걸 작성해주면 input, output이런식으로 선언하는것이 아니라 모든 변수에 대해 type을 명확하게 명시해주면서 코드를 작성해야합니다.

(귀찮긴한데.... 이렇게 한다해서 손해보는건 없을 거 같습니다.)

Unpacked vs Packed Arrays

네 이번에는 Unpacked, Packed Array에 대해 다뤄 볼 예정입니다.

학부 3학년 1학기 때 마이크로프로세서 시간에 32bit CPU를 Verilog로 작성해보고 시뮬레이션 돌리면서 분석하는 기간이 있었는데요, 이 때 16개의 32bit regitster를 선언할 때 사용한 기억이 납니다.

reg [7:0] mem [255:0]; #1

reg mem2 [28:0]; #2

자 1번과 2번의 차이를 잘 알아둬야, 코드를 잘 작성할 수 있겠지요?

1번에 대해 먼저 생각해봅시다.

우리가 8bit reg 변수를 선언할 때, 어떻게 했었나요?

reg [7:0] mem이렇게 선언했었죠? 이 뒤에 [255:0] 이건 8bit reg가 256개 있다는 뜻입니다.

2번에 대해서는

1번의 경우에서 1bit 크기의 reg변수를 29개 선언했다 라는 의미입니다.

여기서 Unpacked와 Packed Array에 대해 따져보면

1번과 2번은 둘다 unpacked array입니다.

하지만

1번은 256개의 unpacked elements이고 이 안에 8bit은 packed vector of reg라고 합니다.

2번은 29개의 unpacked elements이고 1bit reg입니다.

이걸 인덱싱하는 방법은 먼저 Unpacked에 해당하는 index number로 인덱싱하고 이 후 packed에 해당하는 index number로 인덱싱하면 됩니다.

자 이제 문제를 풀어보도록 합시다.

문제에서는 half word를 lower byte, upper byte로 나누는 circuit을 작성하라고 되어있습니다.

`default_nettype none // Disable implicit nets. Reduces some types of bugs.

module top_module(

input wire [15:0] in,

output wire [7:0] out_hi,

output wire [7:0] out_lo );

assign out_hi = in[15:8];

assign out_lo = in[7:0];

endmodule이런식으로 작성해주면 되겠습니다.

위의 내용을 잘 읽어봤다면 충분히 이해가 될 것이라 생각합니다.