안녕하세요

HDLbits 시작기를 작성 후 이제 본격적으로 시작해보려 합니다.

이번 글에서는 정말로 간단한 Basics편에 대해 다뤄보려 합니다.

첫번째 문제는 Wire입니다.

친절하게 wire 변수에 대한 설명이 나와 있습니다.

(물론 영어로 작성되어 있지만요. 한글이면 얼마나 좋겠어)

혹시나 영어로 되어있어서 읽기 힘든 분을 위해 제가 대신 설명해드리겠습니다.

물리적인 전선과 차이점이 있다고 합니다. Verilog에서는 전선은 방향성을 가진다는 점인데, 소스(source)에서 싱크(sink)로만 흐른다는 의미입니다.

여기서 Source는 신호를 보내는 쪽, Sink는 그 신호를 받아들이는 쪽이라고 생각하시면 됩니다. Source는 종종 Driver라고 불리는데, 회로 공부하다보면 어떤 회로를 Driving해준다는 말들을 듣게 됩니다. 그 뜻으로 받아들이면 편할거 같습니다.

Verilog에는 assign이라는 연속 할당문(countinuous assignment)라는 것을 통해서 오른쪽에 있는 신호의 값이 왼쪽의 전선에 전달된다 이렇게 생각하시면 됩니다.

네, 그리고 모듈의 포트에도 방향성이 있는데 input, output으로 선언한 것들입니다

input으로 선언한 변수들은 입력포트로, 모듈 외부에서 값을 받는 역할이고, output으로 선언한 변수들은 출력포트로, 모듈 외부로 값을 보내는 역할입니다.

이번 문제에서는 assign으로 전선을 만들어 주라고 하는군요.

module top_module( input in, output out );

assign out = in;

endmodule위와 같이 assign 문을 사용해주면

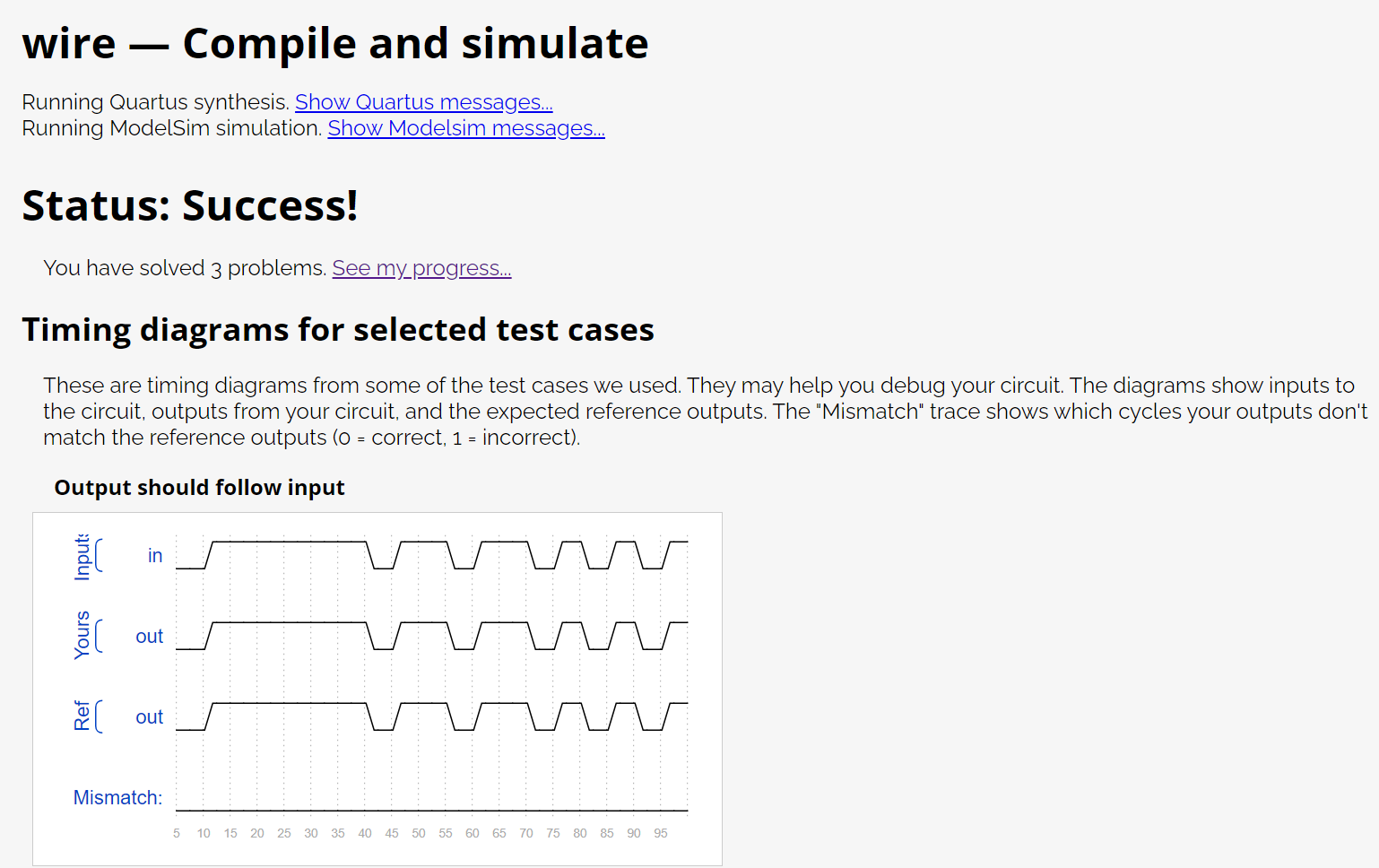

Compile and simulate 성공했다고 나오고, HDLBits에서 간단하게 제공하는 Testcase에 대해 waveform을 보여줍니다.

(참 친절한 거 같아요. 이런거 testbench작성하는거 너무 귀찮...)