1. Memry Hierarchy

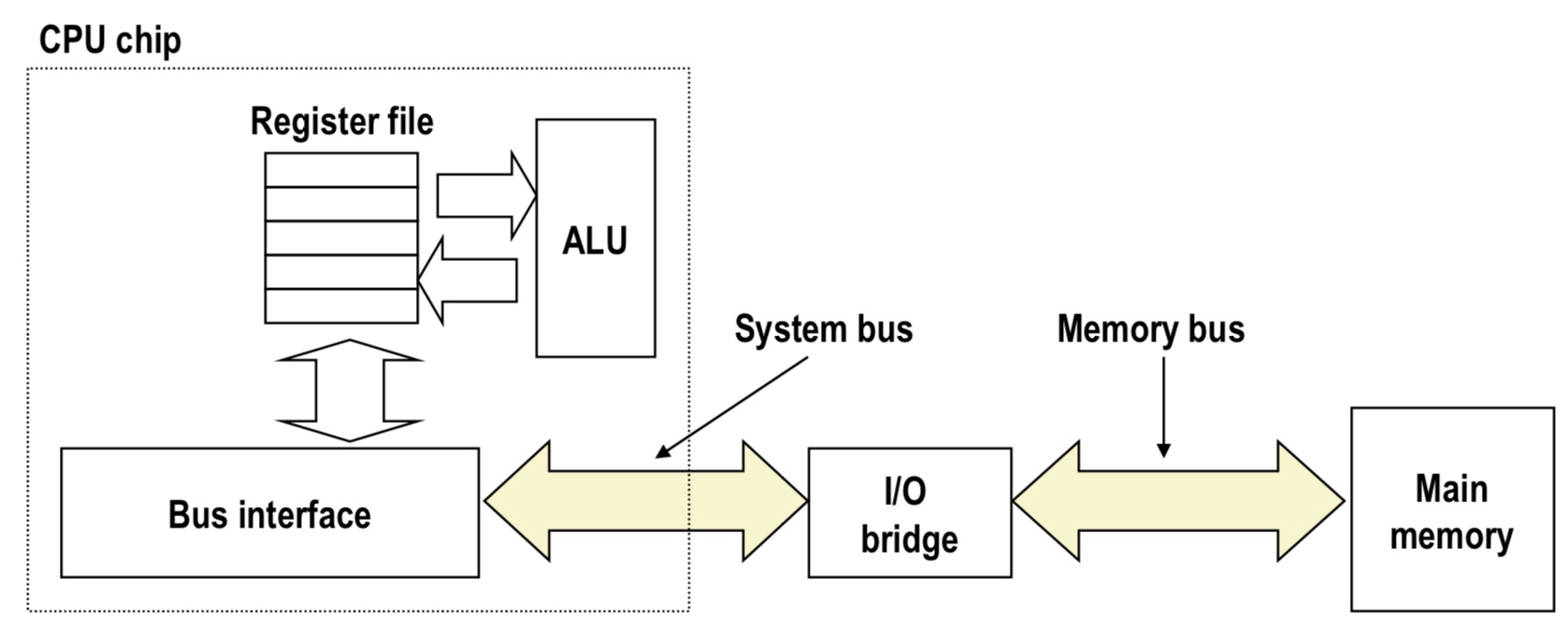

- bus 가져오는 시간만 고려하더라도 register 안에 있는 값들 끼리의 연산이 빠르다

SSD(Solid State Disks)

- 안에 flassh memory가 있고 블록들이 있으며 블록은 저마다 여러 Page 가짐

- 각 블록은 덮어쓰기가 안됨 : 데이터가 있는 경우 지운 후 update 하기 때문에 수명이 길지 않다.

1-1 locality

- 시간 지역성(Temporal) : 한번 접근한 메모리 위치에 대해 가까운 미래에 다시 접근할 확률이 높은 것

- 루프에서 반복적으로 사용되는 변수, 배열의 경우

- 공간 지역성(Spatial) : 한번 접근한 메모리 위치의 근처에 있는 메모리 위치에 가까운 미래에 접근할 확률이 높은 것 의미

- 배열 순차 접근, 구조체 필드 참조시

- 지역성 높을수록 : CPU Cache hit rate이 높아져 프로그램의 실행속도 빨라짐

1-2 General Cache Concepts

-

CPu 연산 속도, Memory에서 가져오는 속도 간의 차이 -> 병목 현상 발생

- Cache hit : 캐시에 있을경우

-

Cache miss : 없을경우(메모리에서 찾는다)

-

Cach Memories

- 캐시 먼저 검사후 있으면 가져감, 없으면 메모리에 request -> 느려짐

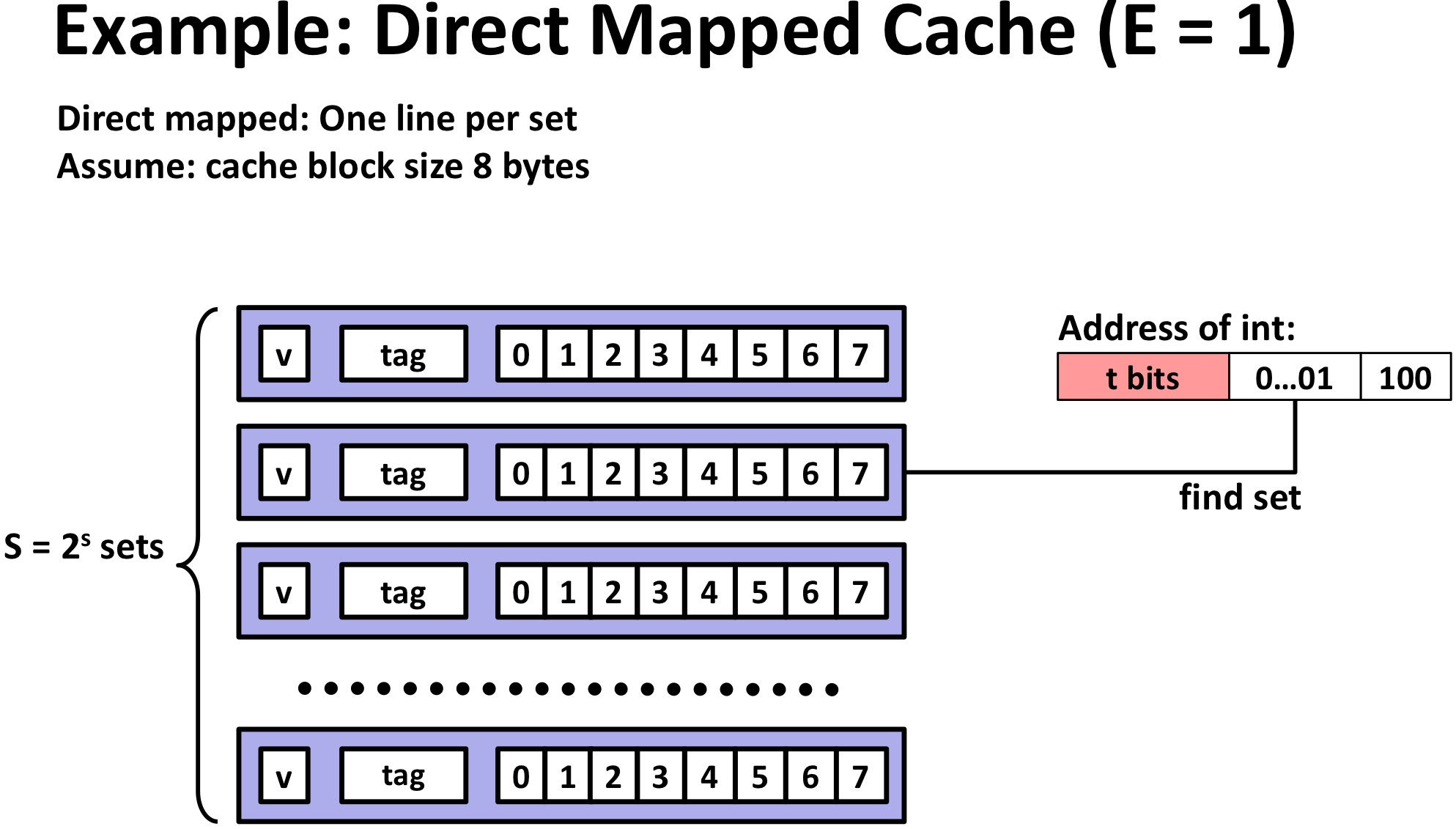

- 캐시의 세트수 S = 2 ^ s

- 집합의 선(블록) 수 K = 2 ^ k

- 한줄의 바이트 수 : B = 2 ^ b

- 캐시 사이즈 C = E B S

- 특정 주소 읽어오는 과정

- tag : 캐시에서 해당 line 찾는데 사용

- set index : 캐시의 행중 몇번째 줄인지, 몇번째 set인지 가리킴

- block offset : line안에서 Meta data 저장하고 있는 Bbytes 공간안에서 세부적으로 정확히 어떤 데이터를 가리키는지 저장

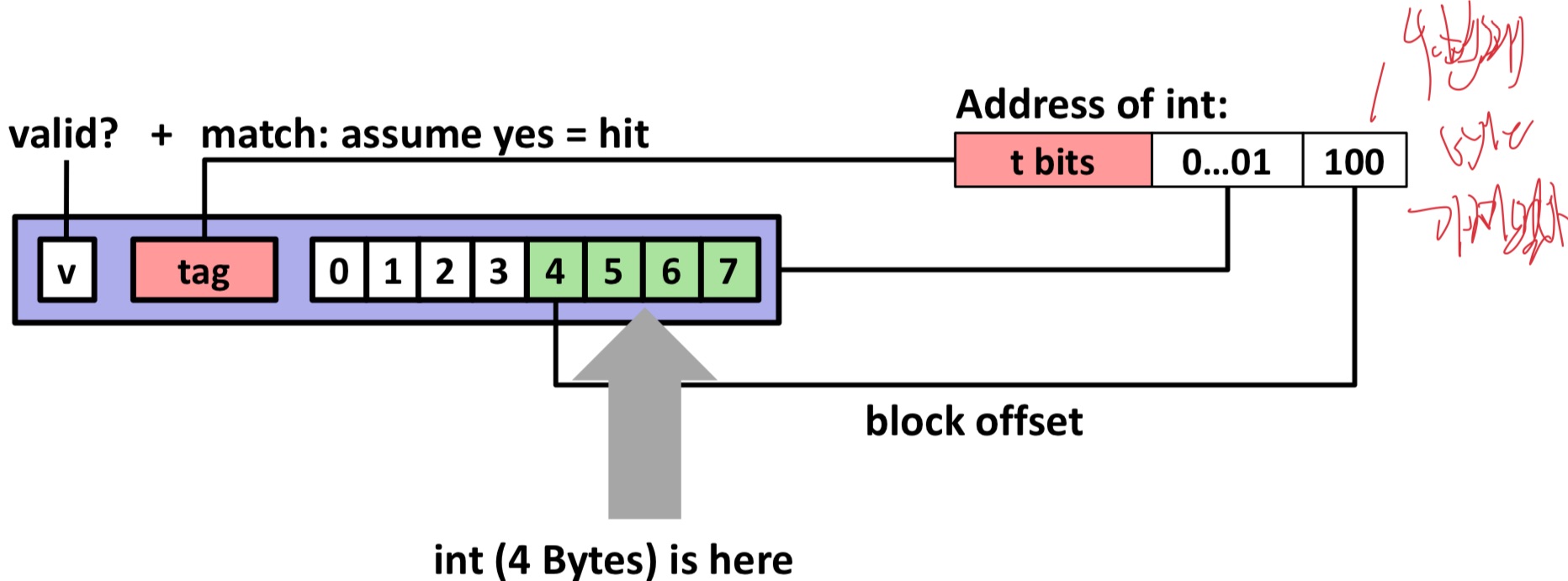

1-2-1 E = 1

- set offset : 00...01 = 2번째 행

- 100 : 4번째 행부터, Int : 4bytes 크기만큼 가져온다

- 마지막으로 valid, tag 확인

- tag 정확 but valid 0 : 기존의 값이 오래된 데이터 저장 -> 새로운 데이터로 덮어씌움

- 반대 : 다른 사람이 쓰고 있다, 다른거 쓰던지 다른방법으로 처리

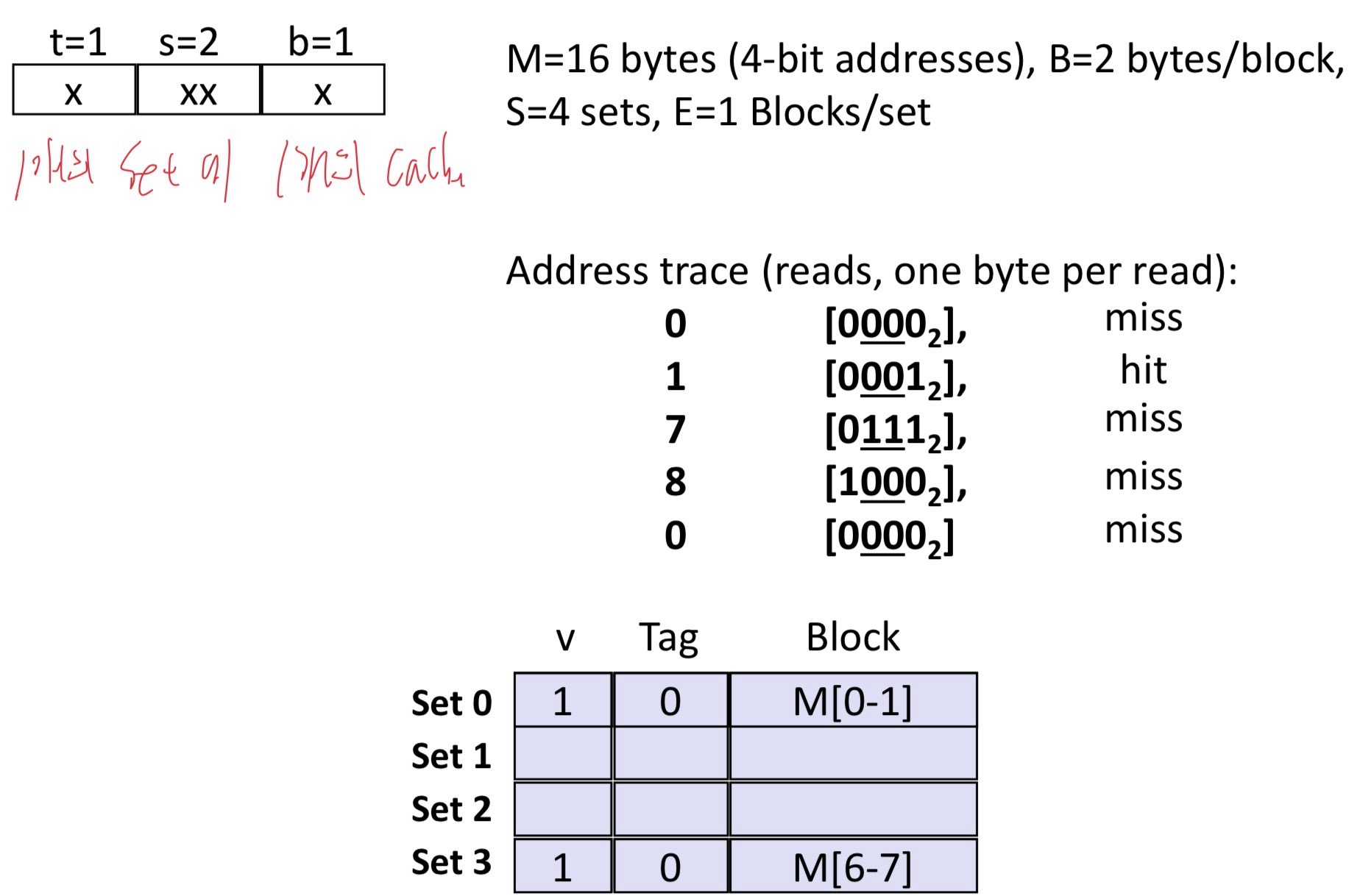

시나리오 1

- 0000 : tag = 0, set = 00, block = 0

- v = 0 -> miss

- 맨처음 캐시에 접근하는 경우는 무조건 Miss

- set 0 : valid = 1, tag = 0, block = M[0-1]

- 0001 : tag = 0, set = 00, block = 0

- v = 1, tag = 0 -> hit

- 0111 : tag = 0, set = 11, block = 1

- set 3 : valie = 0 -> miss

- set 3 : valid = 1, tag = 0, blcok = M[6-7]

- 1000 : tag = 1, set = 0, block = 0

- 기존 set 0 : valid, tag = 0 -> tag 일치하지 않으므로 -> miss

- 새로운 tag값 입력 set 0 : v = 1, tag = 1, block = M[8-9]

- 0000 : tag = 0, set = 0, block = 0

- 방금 8접근으로 인한 Tag값 변경 -> miss

- set 0 : valid = 1, set = 0, block = M[0-1]

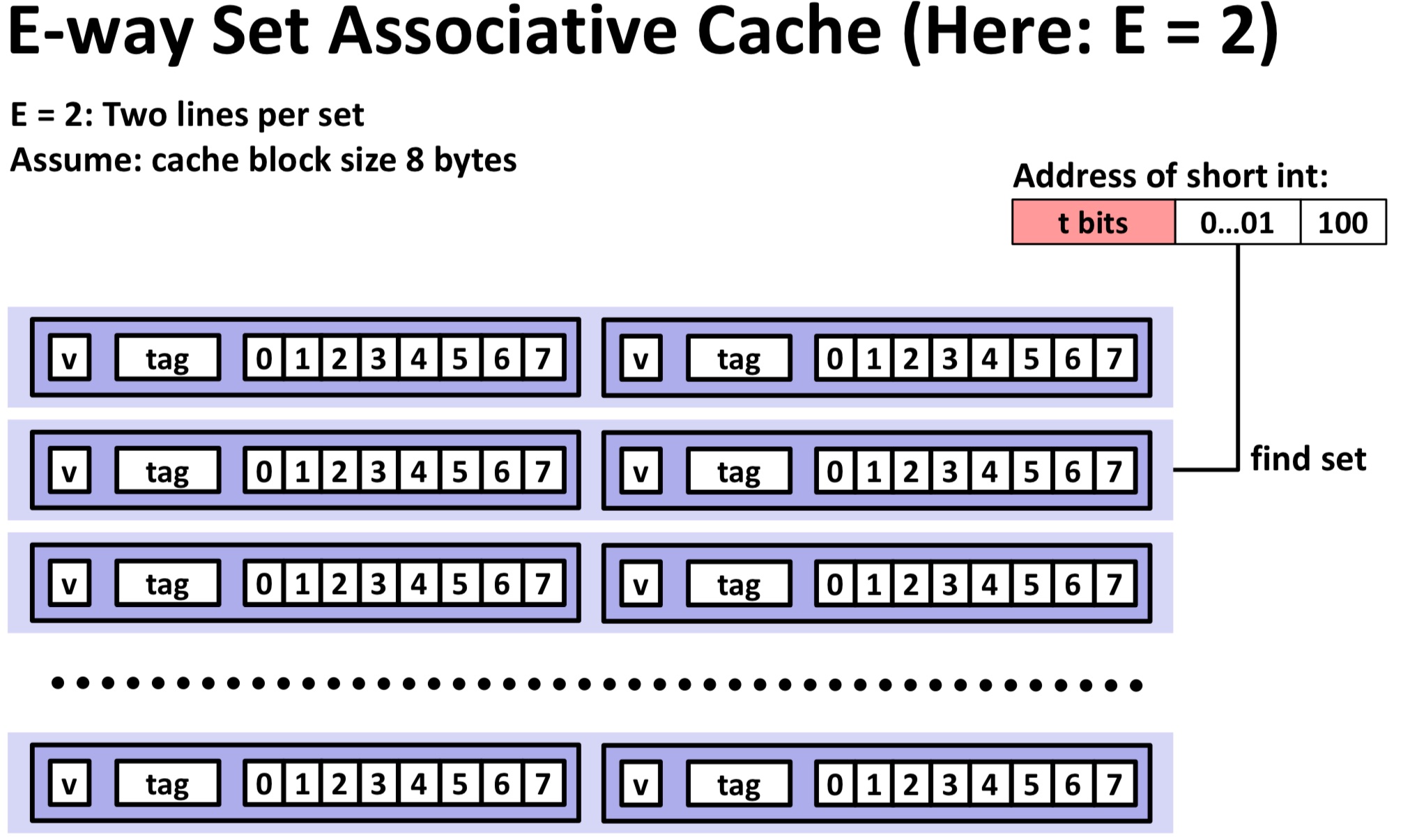

1-2-2 E = 2

- E = 2 => columns = 2

안쓰이는 Tag에 사용가능

- Types of Cache Misses

- Cold(Compulsory) miss : 캐시 비어있을 때 -> 첫번째 접근 miss(부팅시 캐시 X)

- Capacity miss : 캐시 용량 부족

- 프로그램 수행시 접근하는 데이터의 야이 캐시의 사이즈 넘어갈 경우

- conflict : set의 way 부족

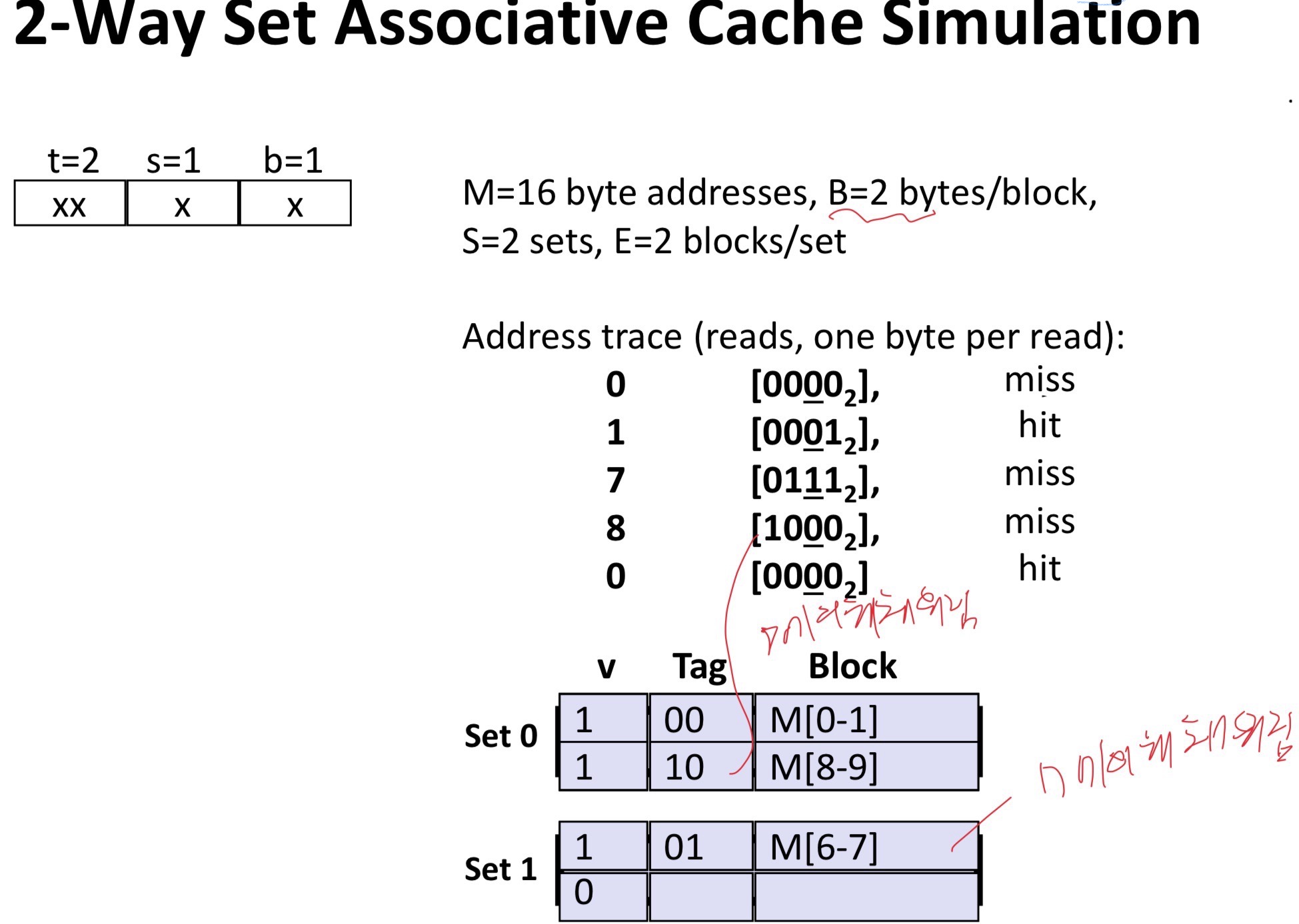

시나리오 2

- set offset 2 -> 1, tag 1-> 2

- 00 0 0: tag 00, set0, block 0

- set 0 : 비어있는 상태 -> miss

- set 0 : v = 1, tag = 00, blockoffset = M[0-1]

- 00 0 1 : set 0, tag 00

- set 0 : v = 1, tag = 00 -> hit

- 01 1 1 : set 1, tag = 01

- set 1 : empty -> miss

- set1 : v = 1, tag = 01, block offset M[6-7]

- 10 0 0 : set 0, tag 10

- set 0 : v = 1, tag 매칭 x -> miss

- 빈자리 tag 10 설정

- 00 0 0 : 10 0 0 이 다른 영역 init했기 때문에 Hit

1-3 캐시 성능 분석 위한 단위

- Miss Rate

- 메모리에서 가져온 비율

- Hit Time

- L1 : 4 clock

- l2 : 10 clock

- hit time 보다 데이터를 빨리 가져올 수 없음

- Miss Penalty

- 데이터 못가져오는 경우 L3 or Main memory에서 가져와야함

- 50, 200 cycles

- Hit rate 계산 : cache hit time 1 cycle, miss penalty 100 cycles라 가정

- 97% hit : 1 + 0.03 * 100 = 4

- 99% hit : 1 + 0.01 * 100 = 2