Instruction execution

먼저 PC 안에 주소를 사용해서 instruction 을 Fetch 한다.

그리고 LOAD 명령어는 1개의 Register , 그리고 다른 명령어는 2 개의 Register 를 사용하게 된다.

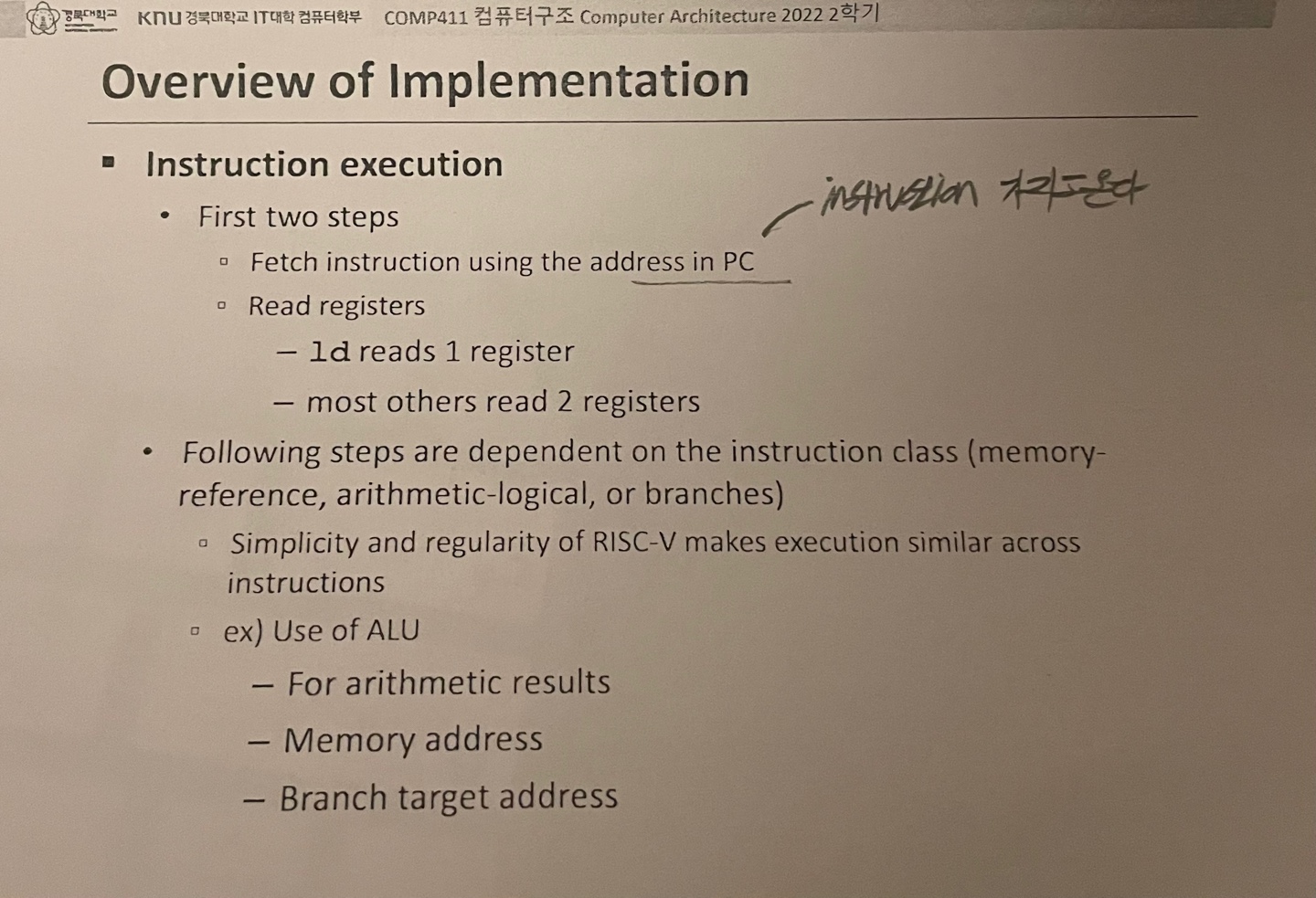

Digital Systems

digital system 은 3개의 요소가 필요하게 되는데

Combinational element, Sequential element, Clock signal 이렇게 3개가 있다

- 와이어가 있다고 하는데 크게 중요하지는 않다고 한다.

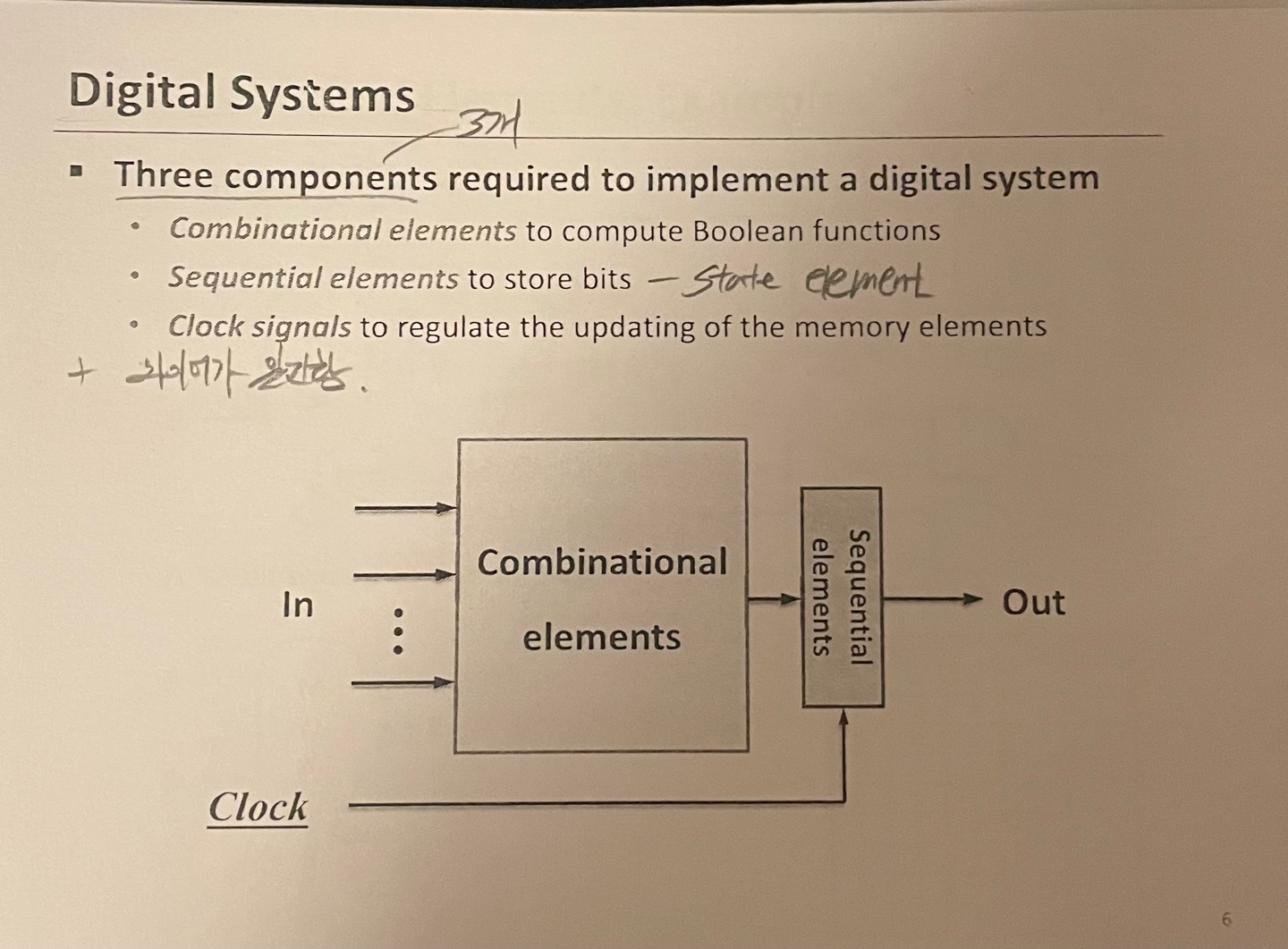

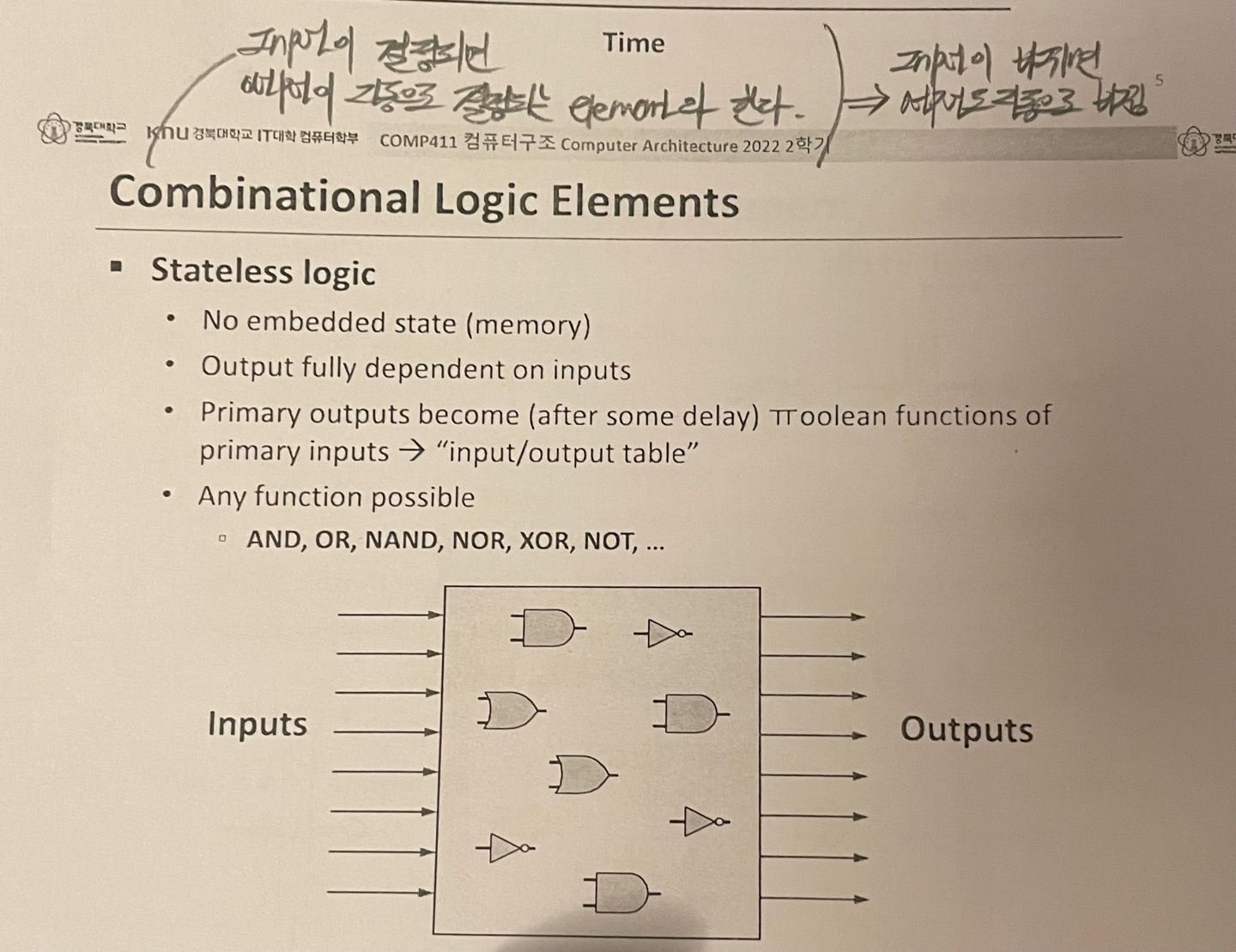

Combinational Logic Elements

Combinational Element 는 Input이 결정되면 Output이 자동으로 결정되는 Element 라 한다

그 말은 Input 이 바뀌면 Output 도 자동으로 바뀐다.

예시로는 AND , OR , NAND , NOR , XOR , NOT 이 있다.

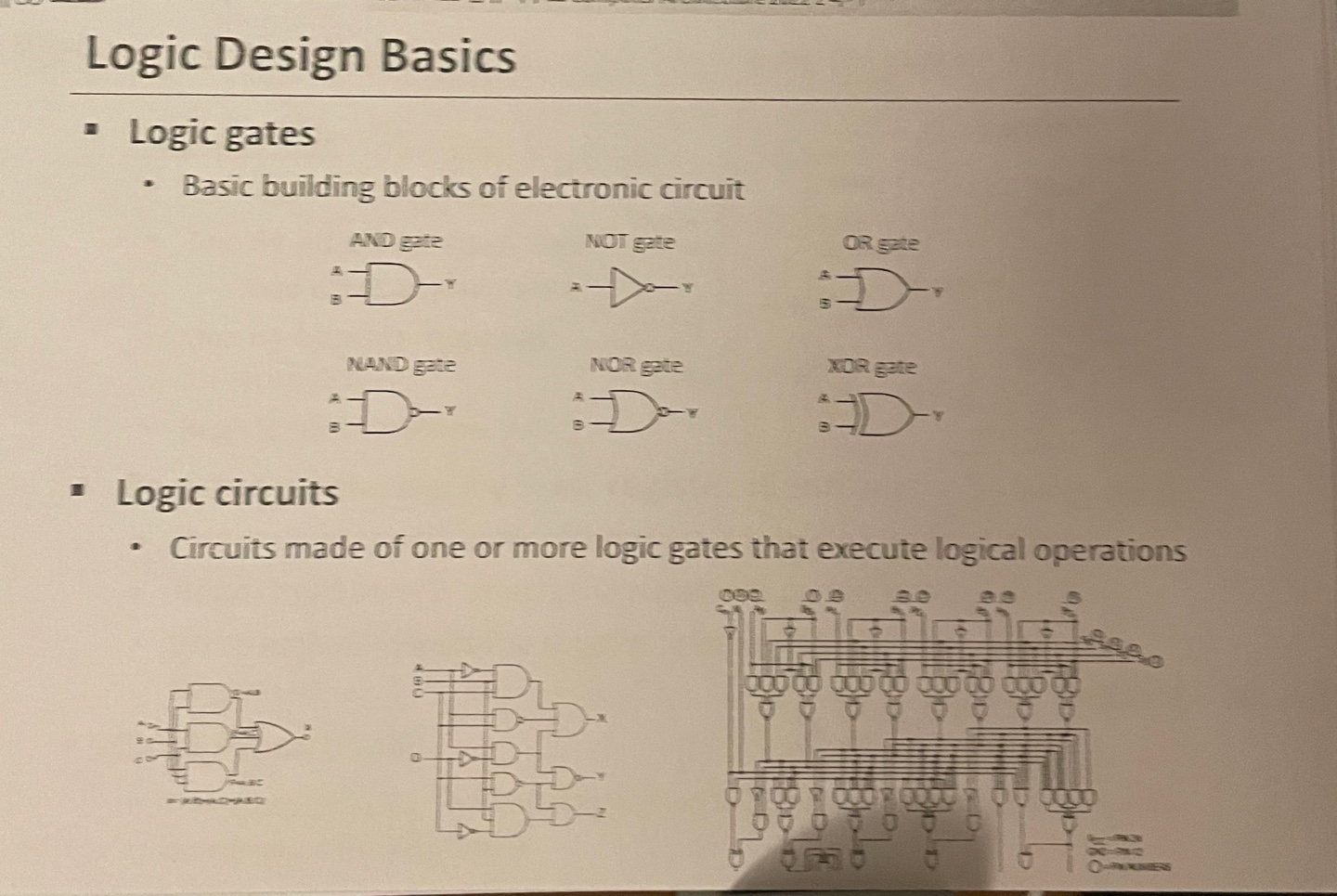

Logical Design Basic

Combinational Elements

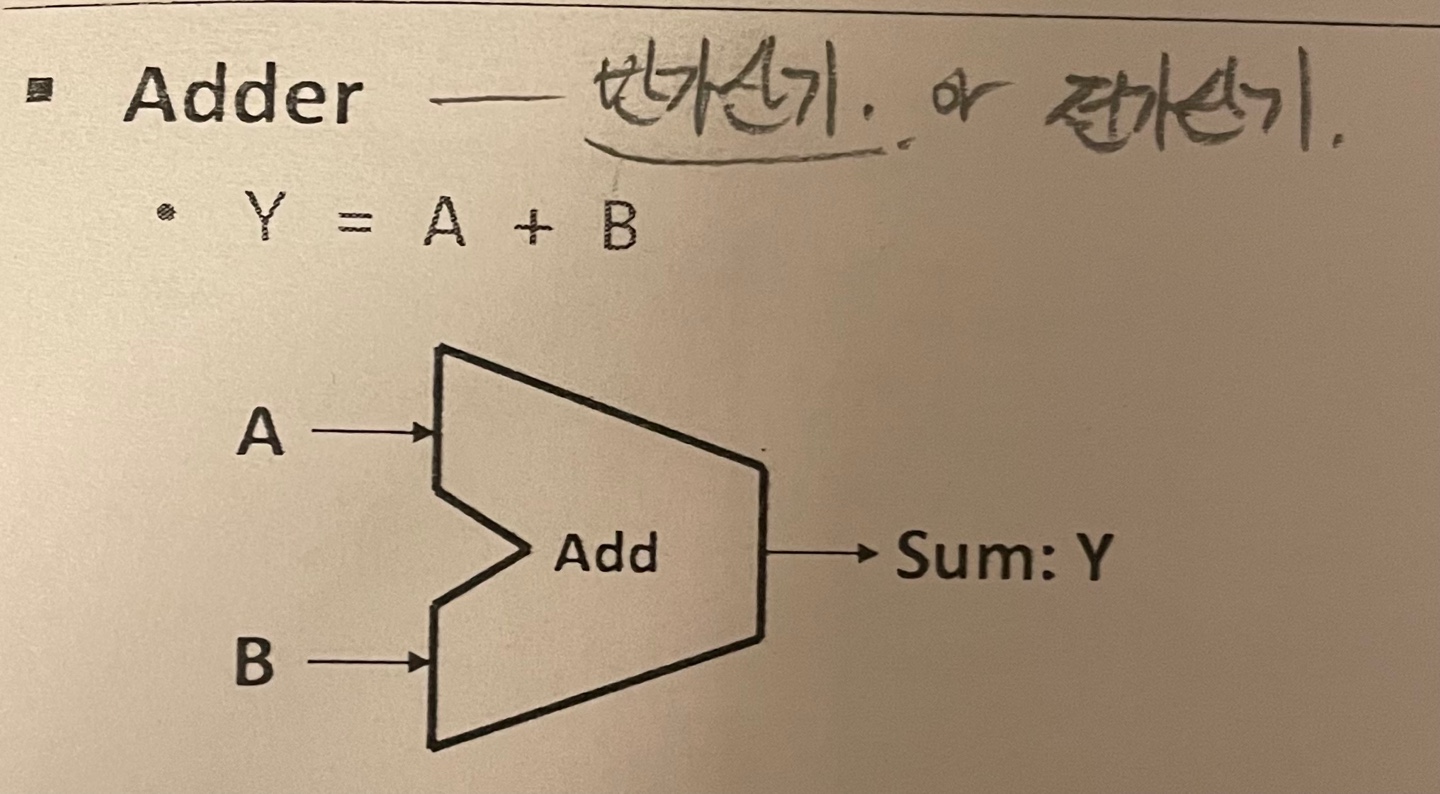

ADDER

A 와 B 의 값을 더해서 Y 의 값으로 결과가 나온다.

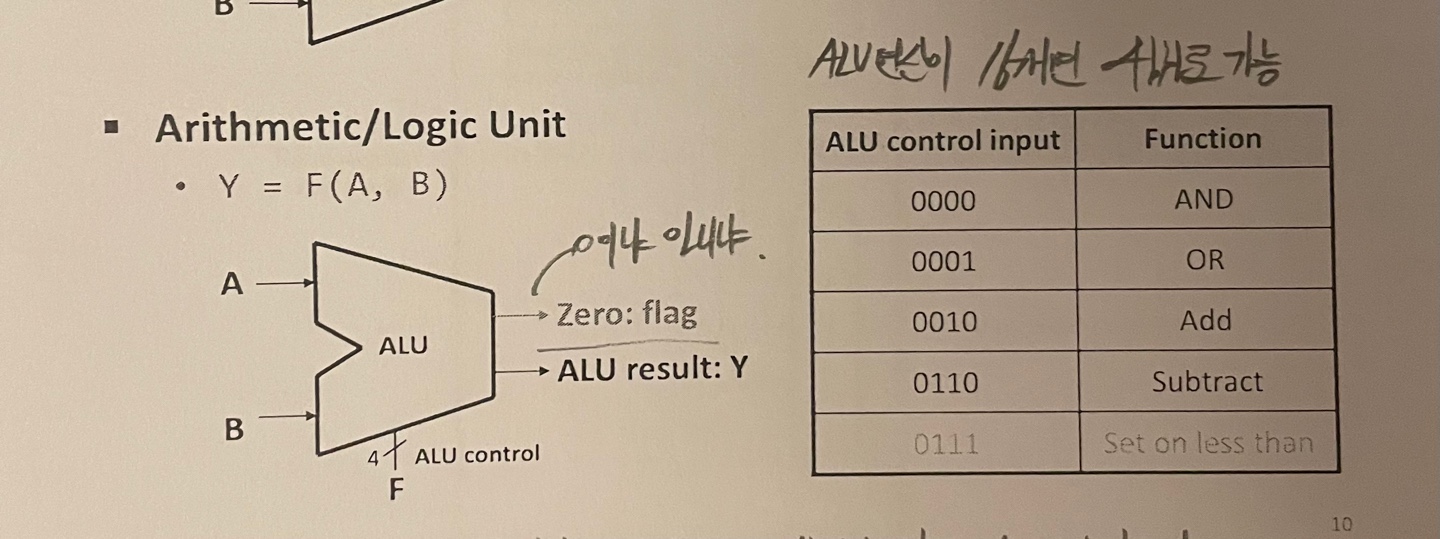

Arthmetic/Logic Unit(ALU)

Y = F(A,B) 이다

ALU result 로는 AND,OR,NAND,SUB 으로 A 와 B 의 연산값의 결과로 나오게 된다.

Zero 는 Flag 로써 BEQ 로 같으면 1 다르면 0 이렇게 FLag 를 통해 결과가 나온다.

ALU 연산이 16개면 4bit 로 표현이 가능하다.

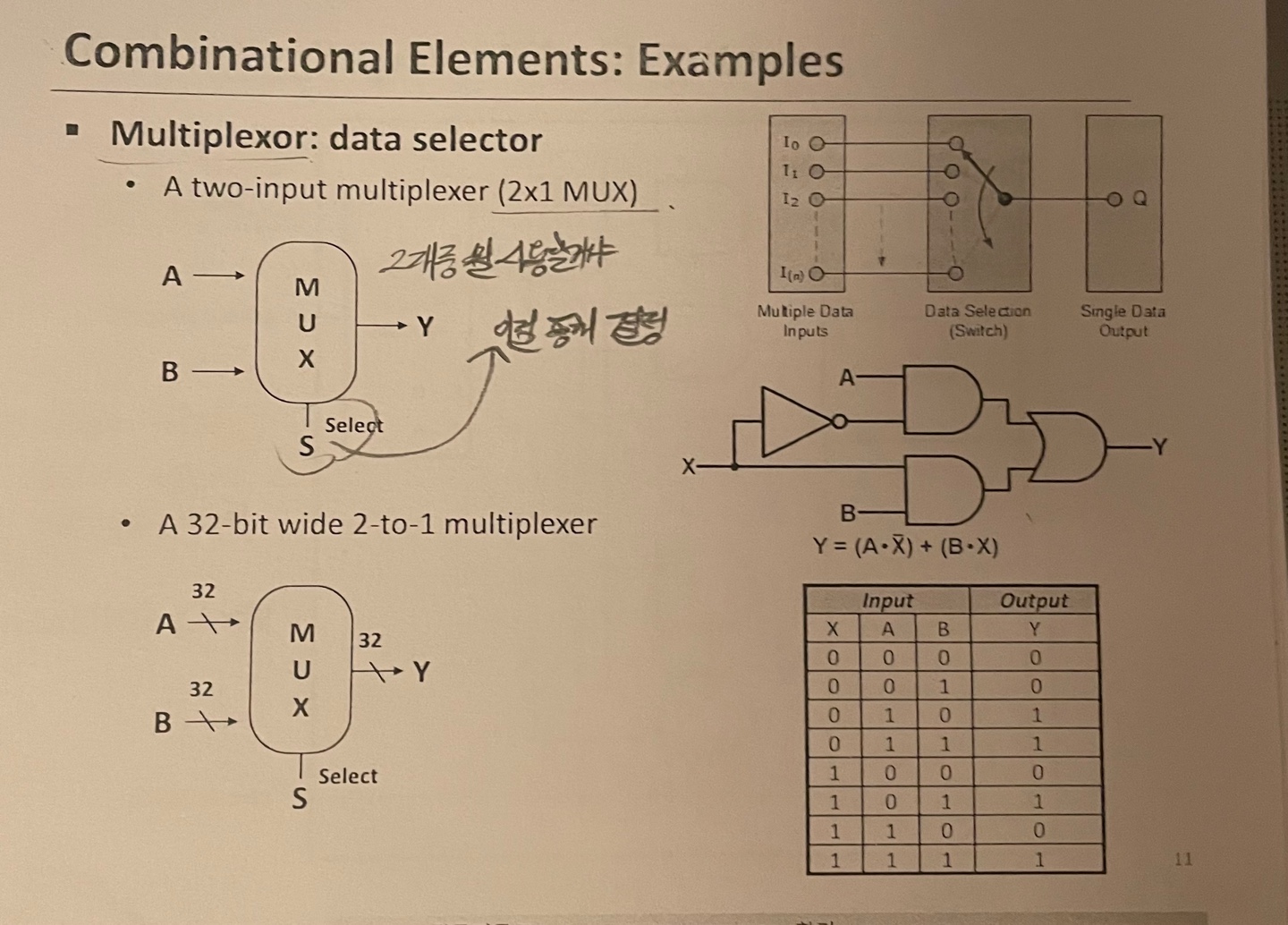

MultiPlexor

Multiplexor 는 여러개의 Input 중 하나를 고르는 것이다.

Data Selector 라고도 부르는데 2X1 MUX는 2개중 뭘 사용할것이냐를 고르는것이다. 그림의 S 는 Select 로 이걸 통해서 무엇을 사용할지 선택한다.

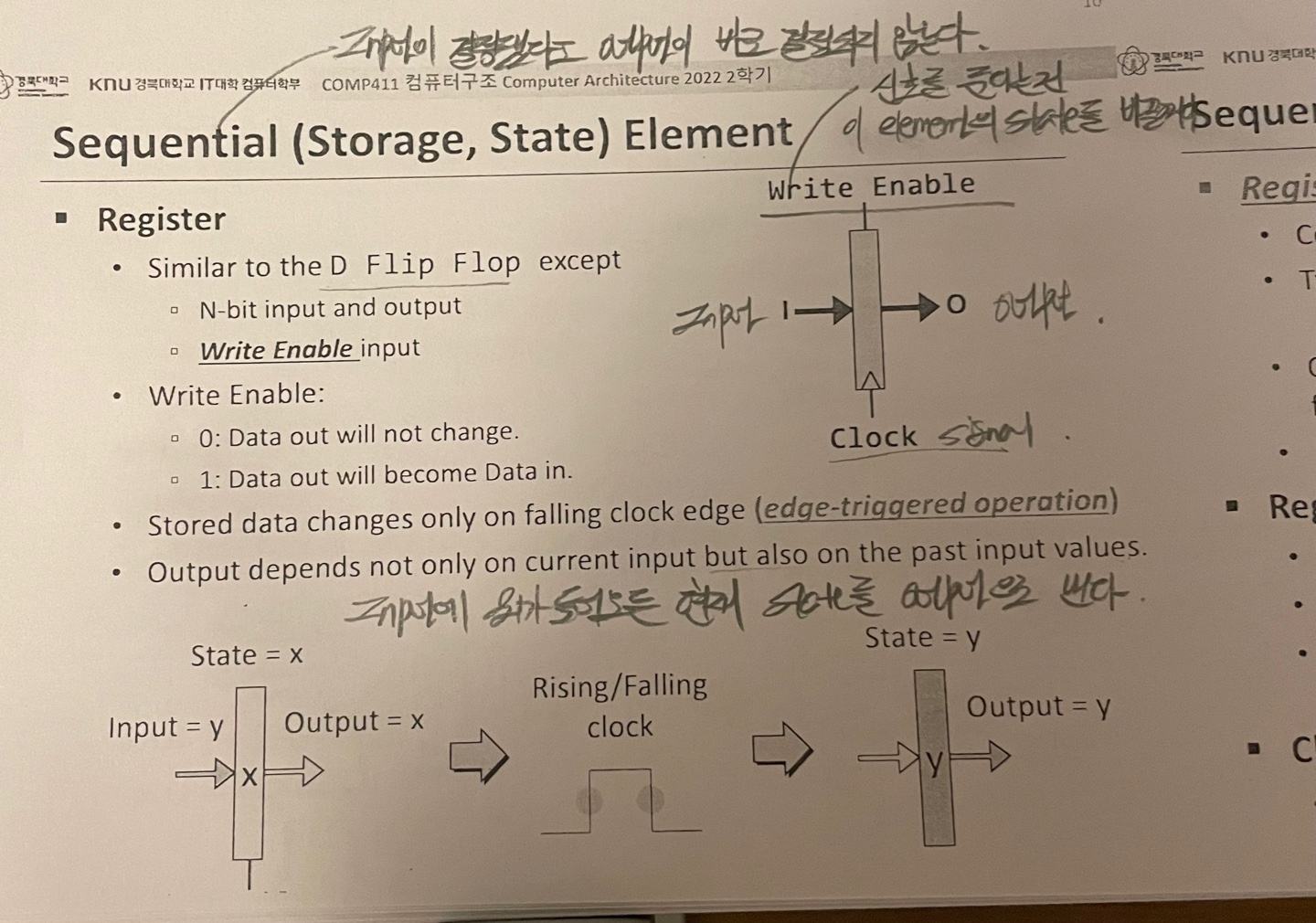

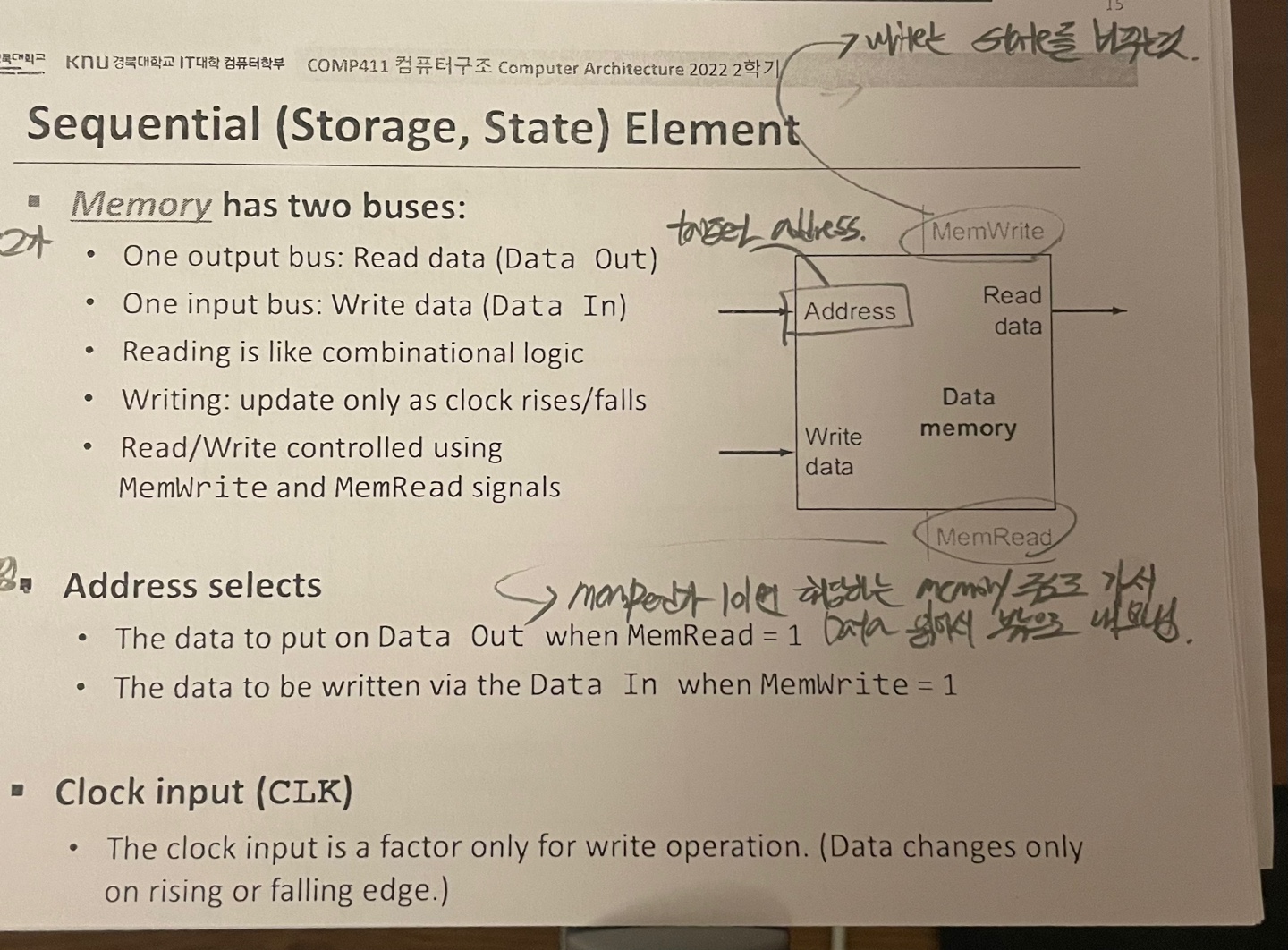

Sequential (Storage, State) Element

Sequential Element 는 Combinational Element 와는 다르게 Input이 결정됐다고 Output이 바로 결정되지 않는다.

Input 이 있고 Write Enable ,Clock Output 이 있다.

Clock 으로 값이 변하기 전엔 Input에 뭐가있든 현재 State 를 Output 으로 사용한다.

그래서 Input 이 들어오고 Write Enable로 신호를 줘 이 element 의 State 를 바꿀것이고 Clock 이 Edge를 통해 값이 변경되면 output 도 바뀐 값으로 나오게 된다.

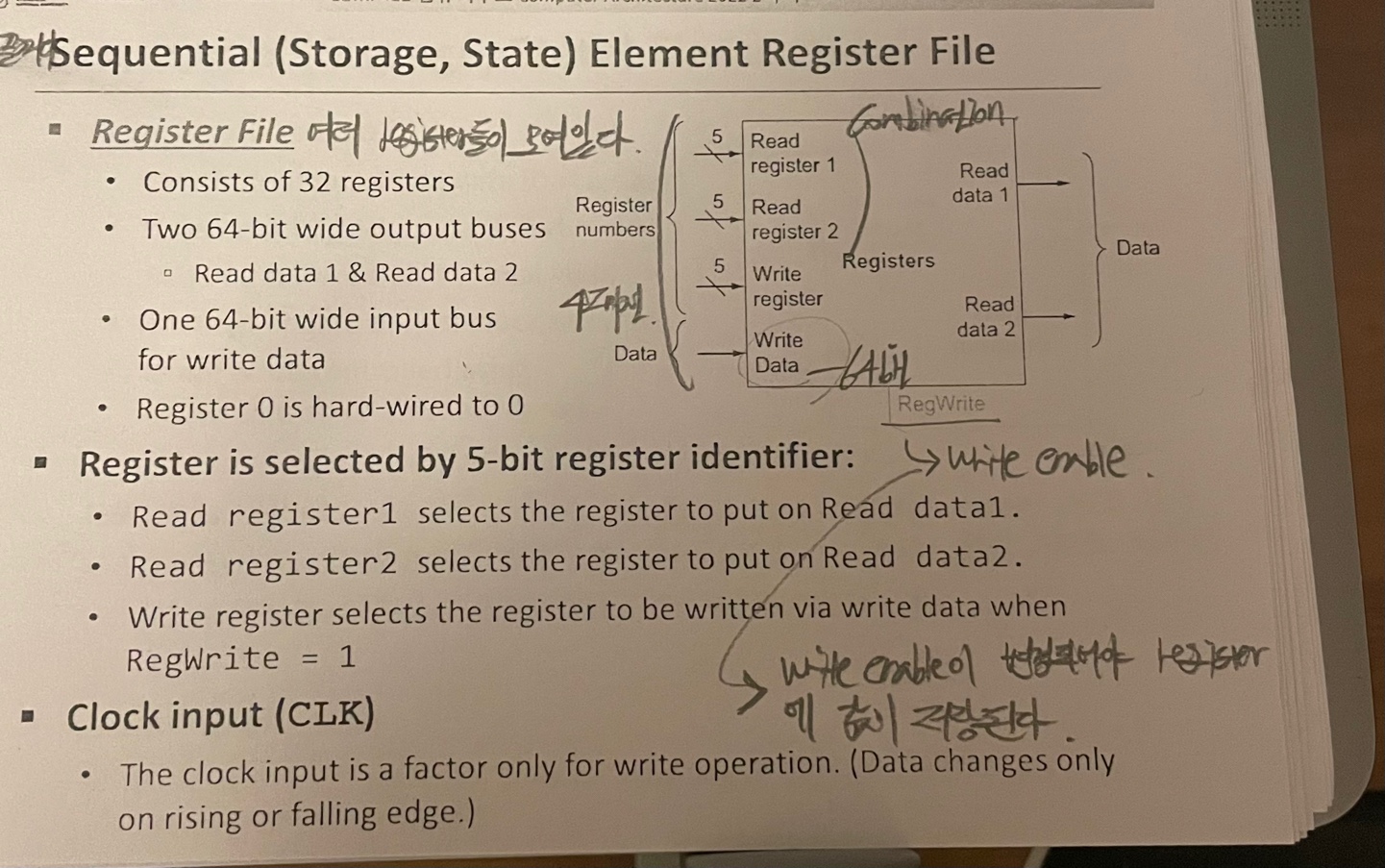

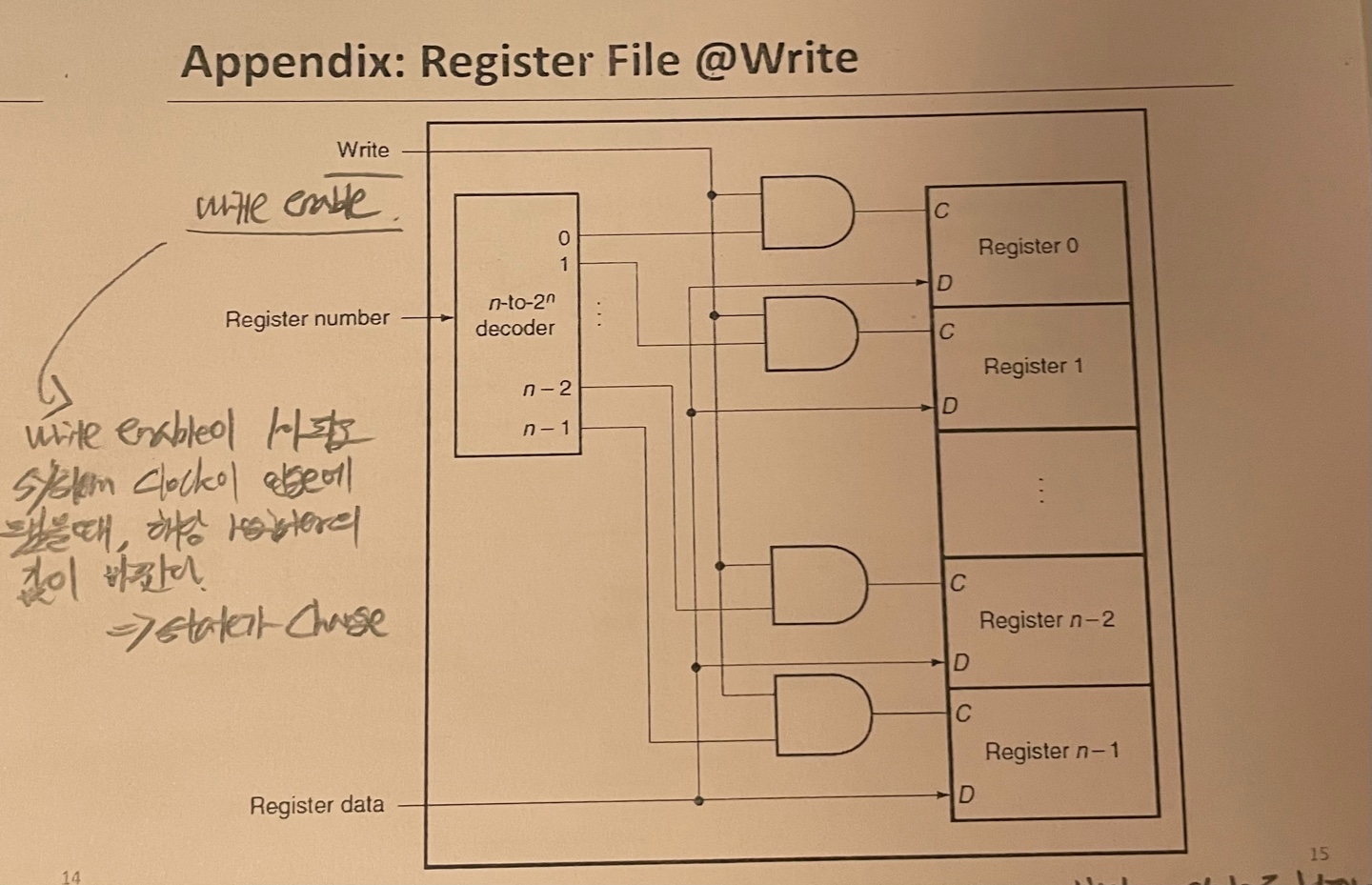

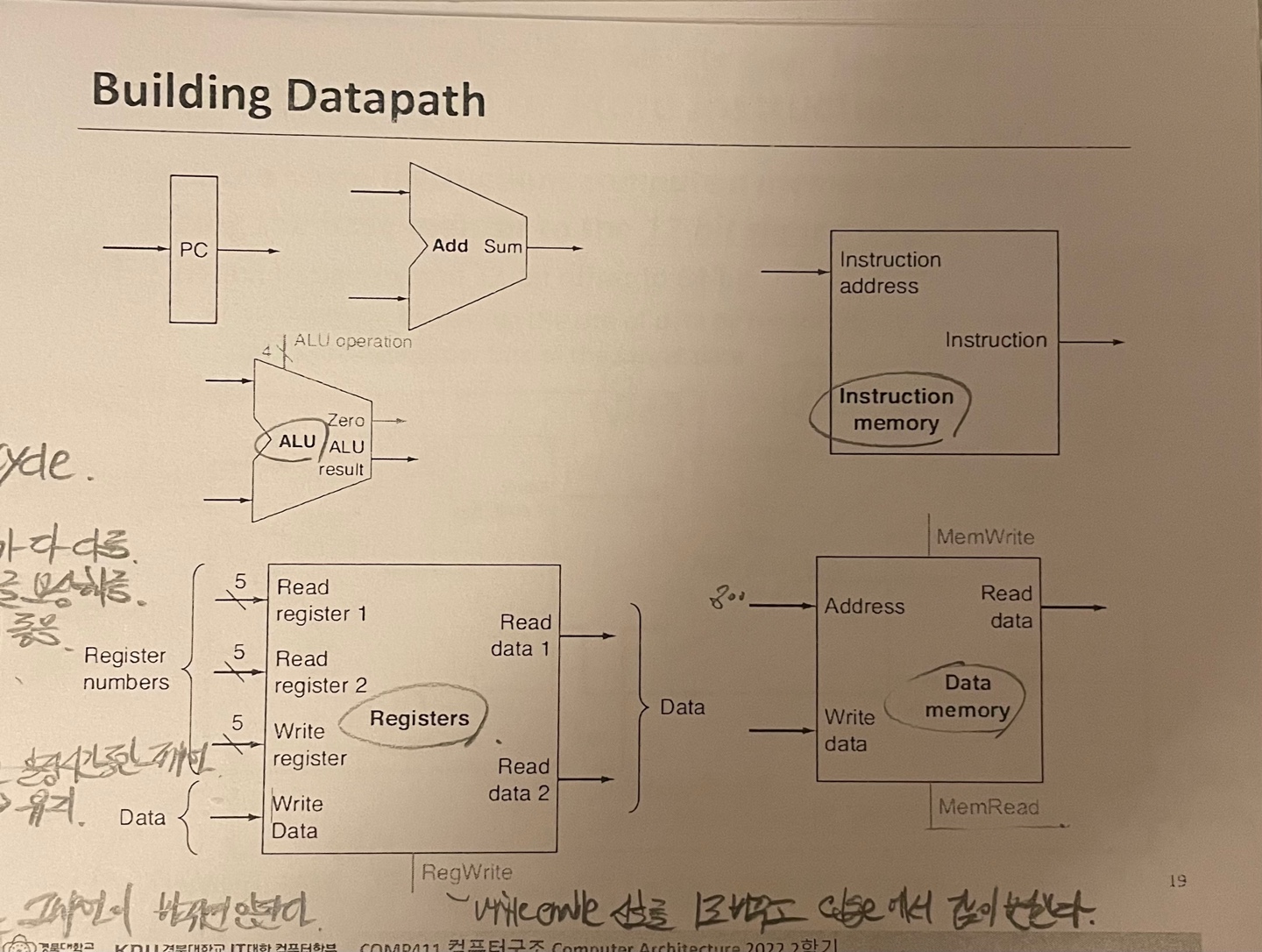

Sequential Element Register File

Register File 에는 여러 Register 들이 모여있다.

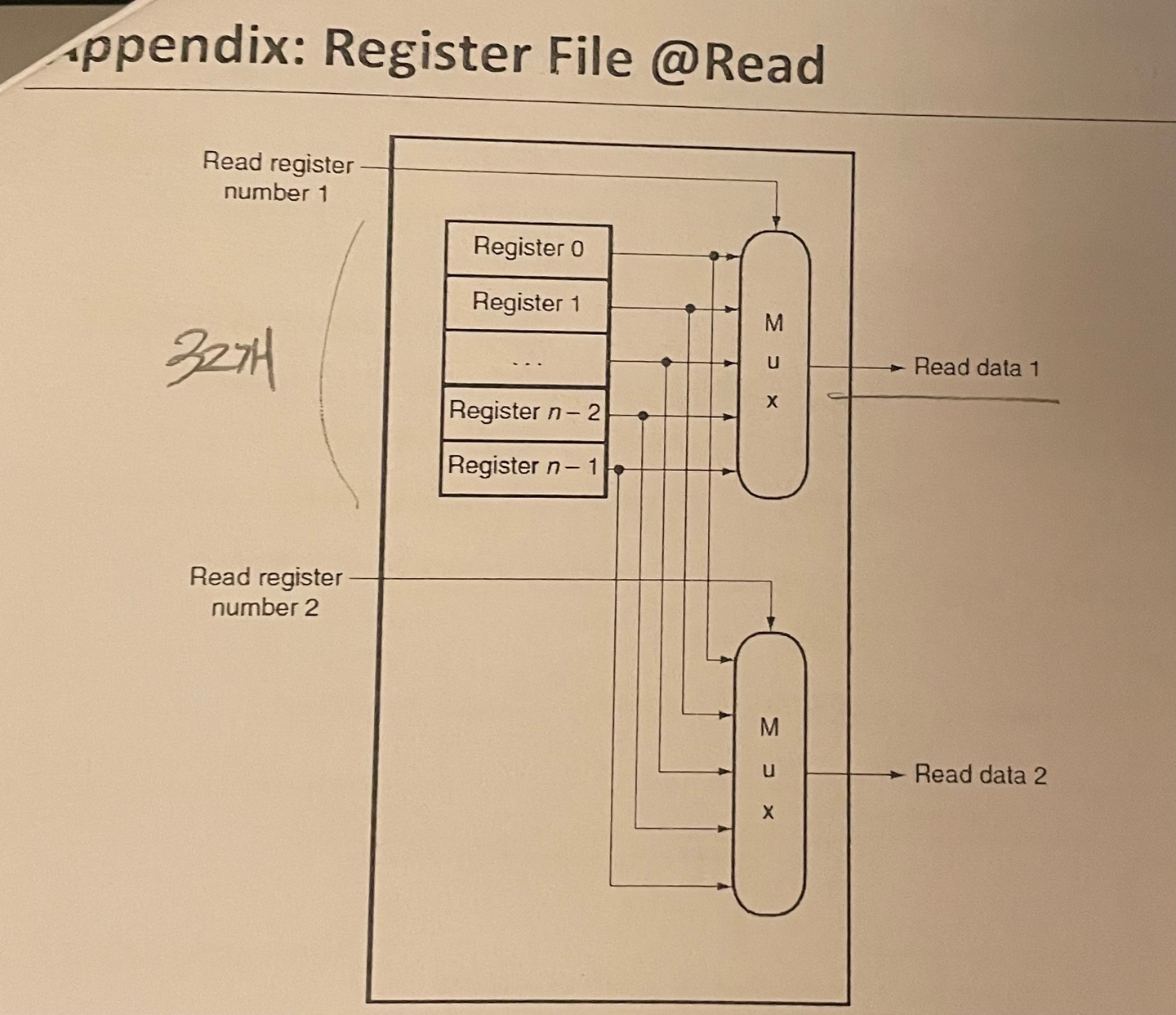

Read register 1 & Read register 2 가 각각 5bit 로 총 64bit 의 비트값을 가진다. 이 두개는 Combination 을 위해 사용된다.

wirte data 에는 64 bit 값을 가진다.

Read Register 1 는 Read data 1에 값을 넣게 된다.

그리고 Write Register 에는 Write Data에 담겨있는 값이 RegWrite 가 1 일때 Clock 에 값이 변경되면 Write Register 에 값이 들어가게 된다.

Data Memory

Read data 는 Output 이고 Write data 는 input 이다.

MemWrite 는 State 를 바꾸는것이다.

MemRead 는 값이 1 이면 해당하는 memory 주소로 가서 Data 읽어서 밖으로 내보낸다.

그리고 Write 는 Clock 값이 바뀌게 되면 write 값이 바뀌게 된다.

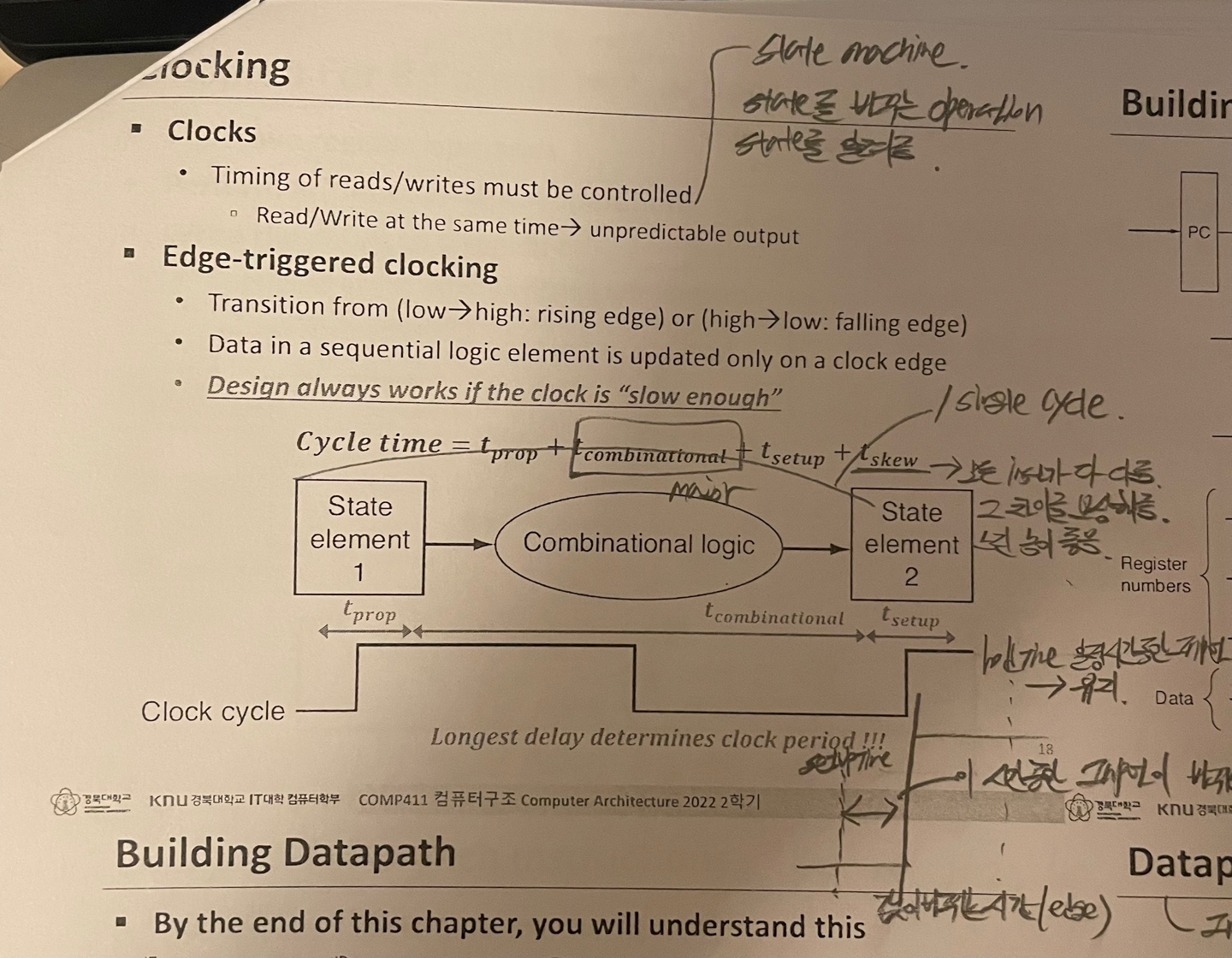

Clocking

State Machine 은 State 를 바꾸는 Operation 이다.

State 를 알려준다.

Edge-triggered clocking

Data 는 Clock Edge에 값의 변경에 따라 Data 값이 변경된다.

Cycle Time 은 Propogation Time + Combinational TIme + Setup TIme + Skew Time 이라한다.

Skew Time 은 모든 Instruction 이 다 다른데 그런 차이를 보상해준다한다.

그리고 Propogation Time 이랑 Setup Time 은

값이 바뀌는 시간을 Edge 라한다.

그 어느순간부터 Edge 까지 Input 이 바뀌면 안되는 구간을 Setup Time 이라한다.

그리고 그 Edge 부터 어느순간까지 Input 이 유지되는 구간을 Hold Time(Prop TIme) 이라 한다.

Building DataPath

PC , Add , ALU , Register ,Instruction Memory , Data Memory 를 활용할것이다.

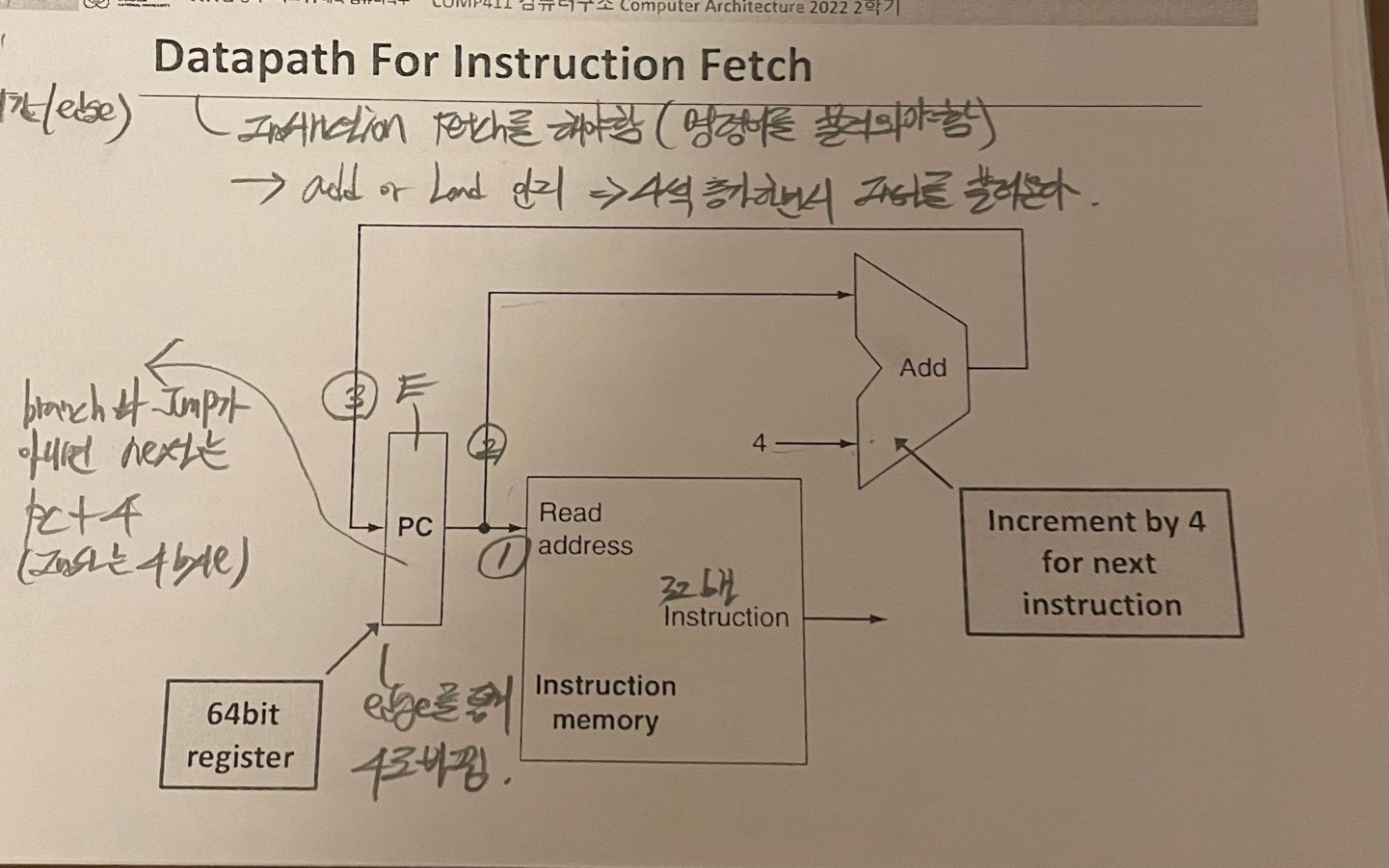

DataPath for Instruction Fetch

제일 먼저 시작으로는 Instruction Fetch 를 해야한다. 명령어를 불러와야한다는 말이다.

ADD 인지 LOAD 인지 4씩 증가시키면서 Instruction 을 불러온다.

먼저 PC 에 있는 주소를 읽어서 해당 주소의 Instruction 을 읽어낸다.

그리고 Branch나 Jump 가 아니면 Next 는 PC+4 다

Instruction 은 4Byte 이기때문에 4Byte 를 추가한다.

DataPath for R-format Instruction

add rd(3) rs1(1) rs2(2) 의 Instruction 이 있다 가정한다.

Register 번호를 각각 3,1,2 라고 한다.

add 명령어는 rs1와 rs2 레지스터 값을 더해서 rd 에 넣는것이다.

먼저 instruction 의 Opcode 를 통해서 어떤 연산인지 알아야한다.

그리고 01 를 Read Register 1 으로 부터 10 을 Read Reigster 2 로 부터 읽어서 Read data 1 에는 rs1 의 값 Read data 2 에는 rs2 의 값이 들어가게 된다.

그리고 ALU Opertaion 의 연산에 따라 rs1 과 rs2의 연산이 result 로 나가서 Write Data 에 들어가게 된다.

여기서 만약 연산이 Beq 였으면 Zero Flag 로 값이 나가게 된다.

하튼 Write Data는 3번 Reg 에 연산값을 쓰라고 한다.

RegWrite 신호를 0에서 1 번으로 바꾼다

그리고 Edge 를 통해 3번 레지스터인 Rd 의 값을 바꾸게 된다.

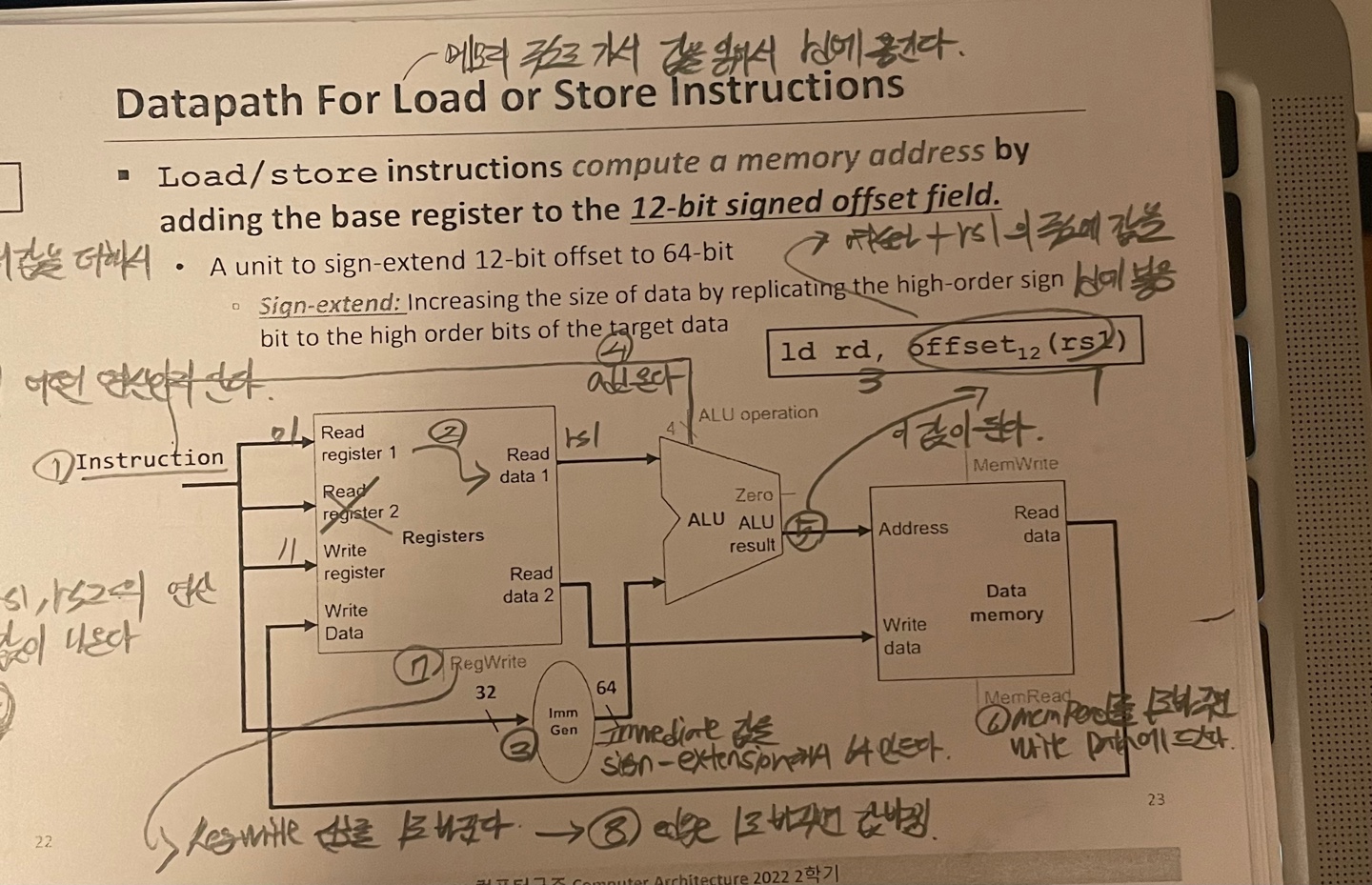

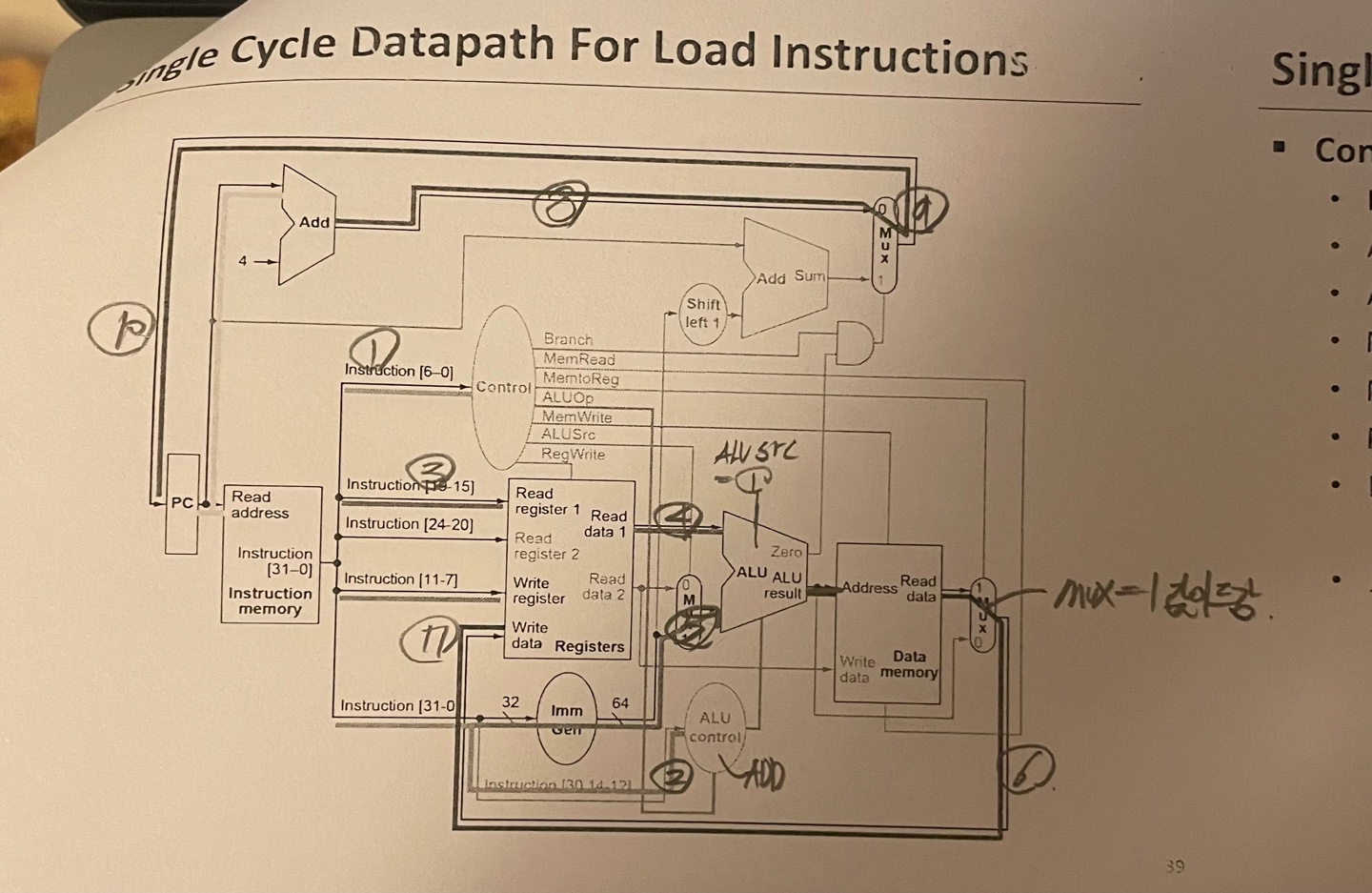

DataPath for Load Instruction

Load 는 메모리 주소로 가서 값을 읽어서 Rd 에 옮긴다.

ld rd, offset(rs1) 이라는 명령어가 있을때 이 명령어는 offset 값과 rs1 의 값을 더한 메모리 주소로 가서 그 메모리 주소의 값을 rd에 넣는다.

먼저 Instruction 을 통해 어떤 연산인지 확인하고 Load 명령어 임으로 한개의 Read Register 를 사용하게 된다.

Read Register 1 에 01 을 넣고 Read data 1 에 rs1 의 값이 들어오게 된다.

그리고 ImmGen 이 Immediate 값을 Sign-extend 를 통해 64 bit 로 바꾼다. 그 값이 ALU 에게 가서 IMM 값과 rs1 을 더해 ALU Result 로 나오게 된다.

그럼 Data Memory 에서는 ALU Result 로 나온 값을 주소로 받아서 MemRead 를 1로 바꿔주면 Write Data 에 들어가게 된다.

그리고 RegWrite 신호를 1로 바꾸고 Edge를 1로 바꾸면 값이 바뀌게 된다.

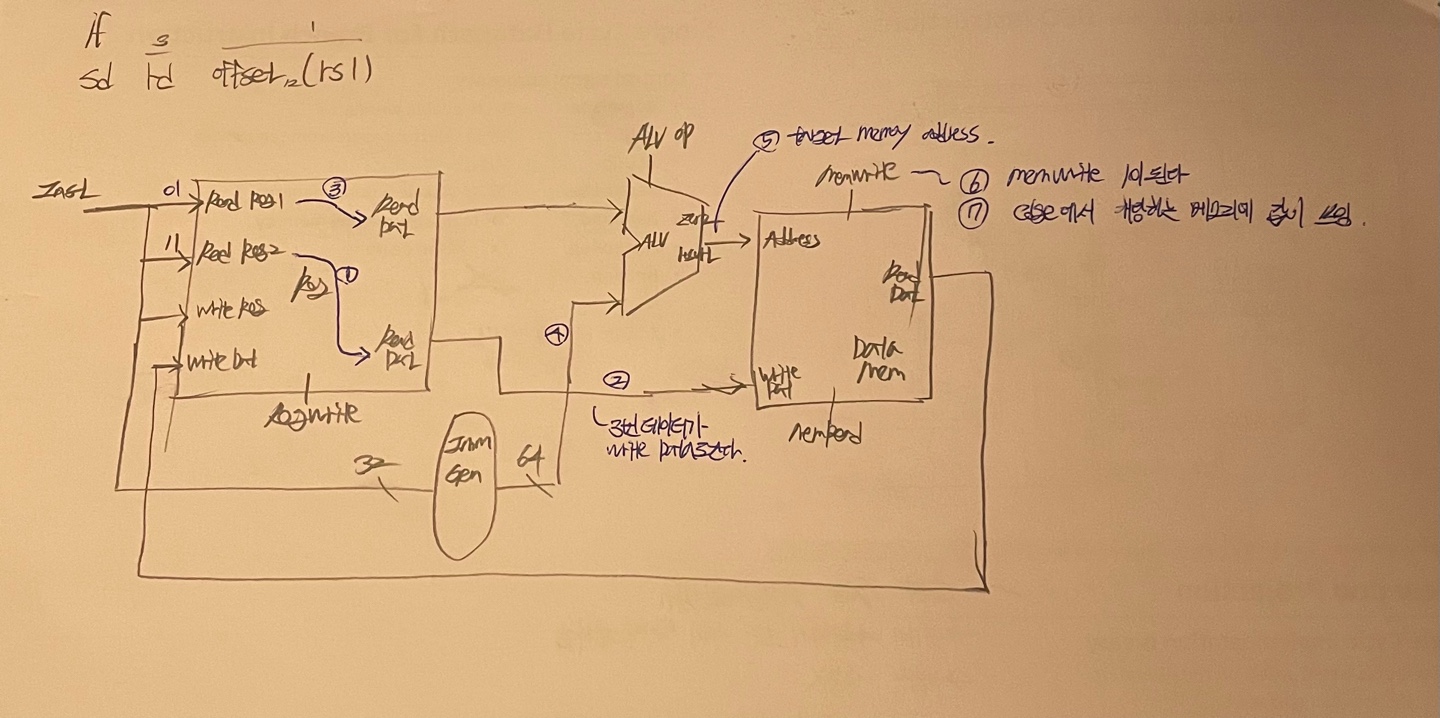

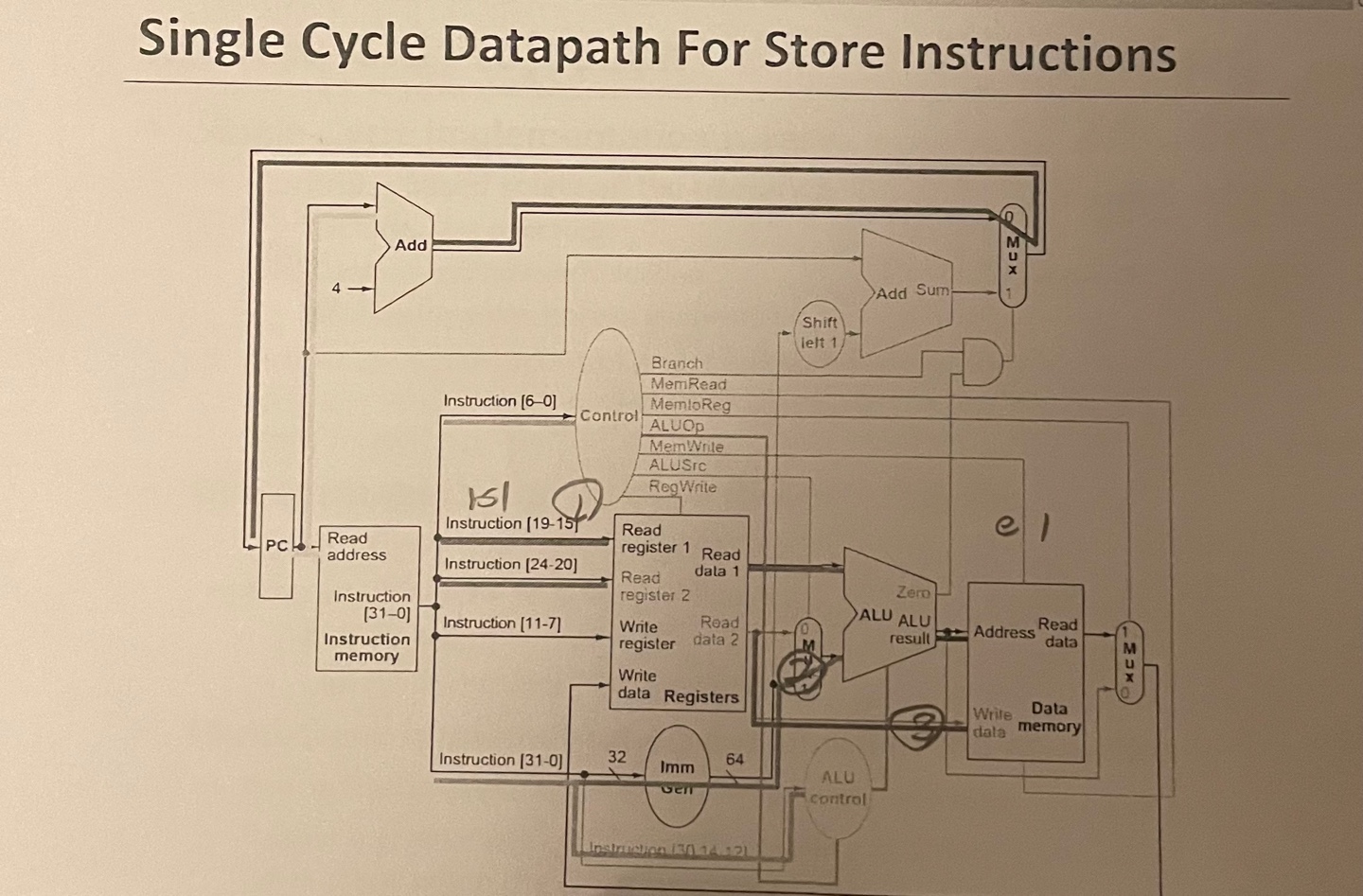

DataPath For Store Instruction

Store 은 Rd 에 있는 값을 Offset+rs1 의 주소에 저장하는것이다.

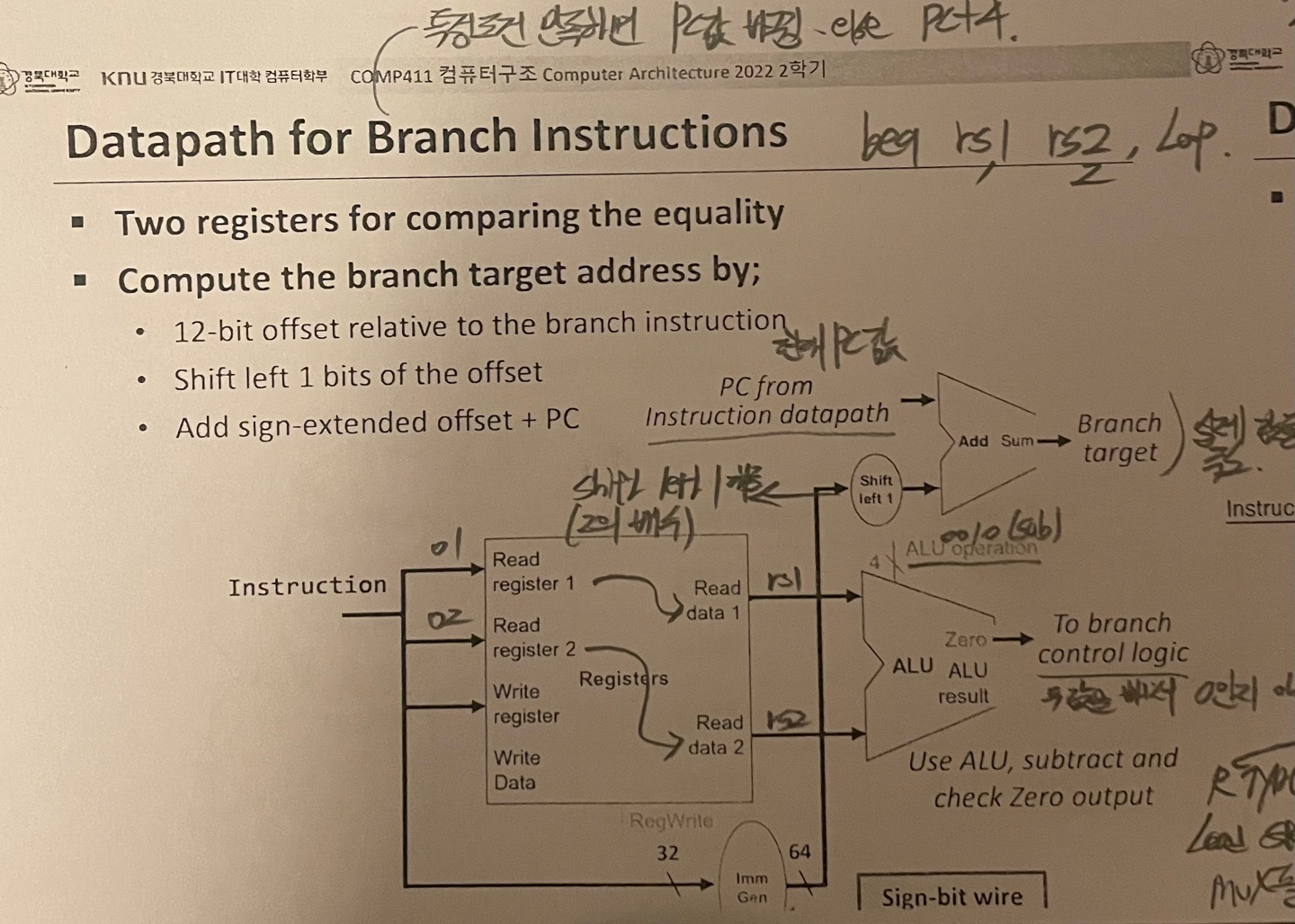

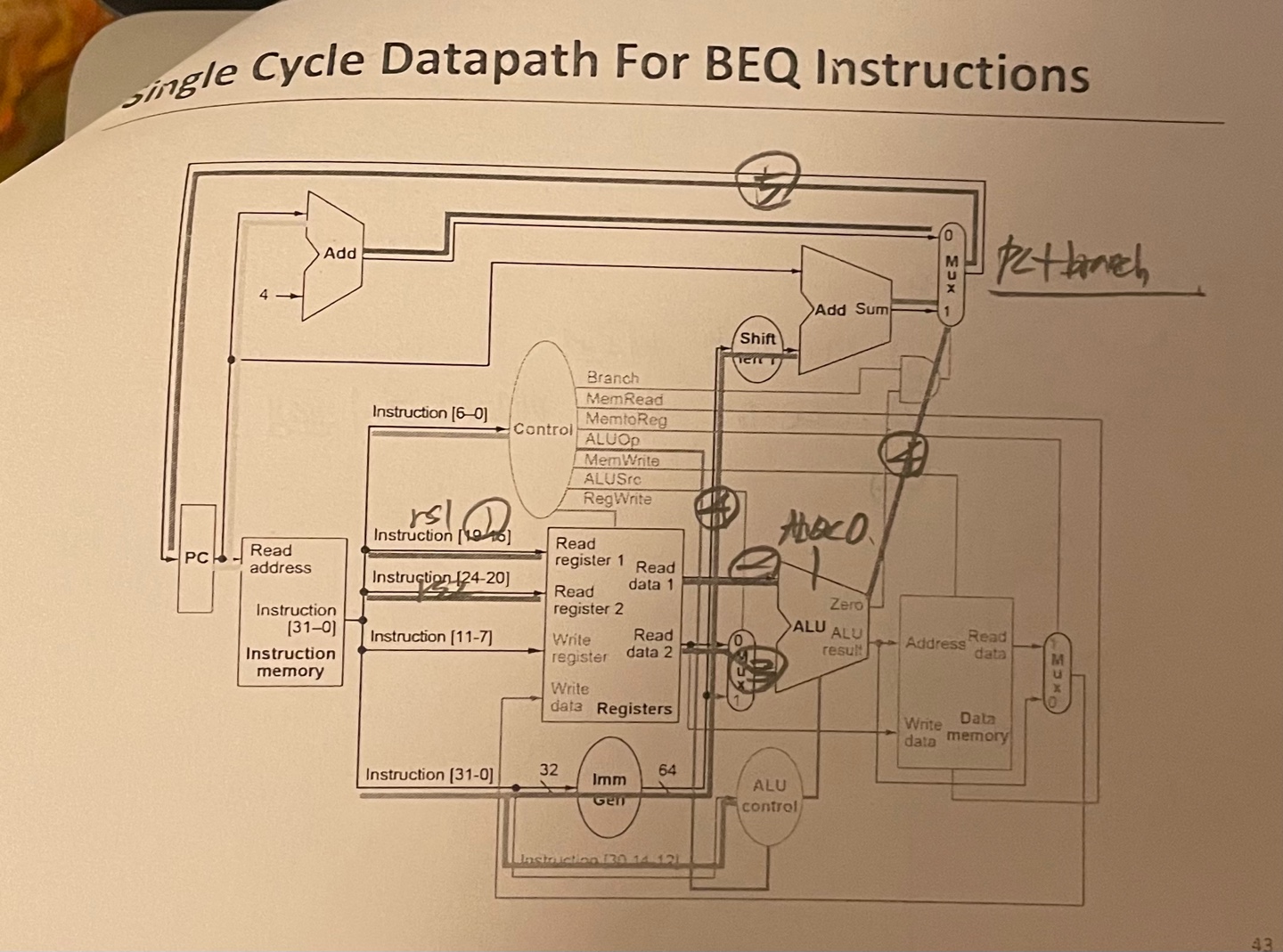

DataPath For Branch Instruction

Beq rs1 rs2 Loop 는 rs1 과 rs2 가 같으면 Loop 위치로 가는것이다.

그렇지 않으면 Pc+4 하라는 말이다.

rs1 을 1 번 rs2 를 2번 레지스터라 한다.

Read Register 1 은 01 의 register 를 찾고 Read register 2 는 10 의 레지스터를 찾는다 그리고 Read data 1 과 Read data 2 에는 rs1 의 값과 rs2 의 값이 들어가게 된다.

ALU 에는 SUB 가 들어오게 되는데 둘의 값을 뺴서 0이면 같은 값이기에 ) 이면 Loop 의 위치 0의 값이 아니면 Pc+4 의 주소로 가면 되는것이다.

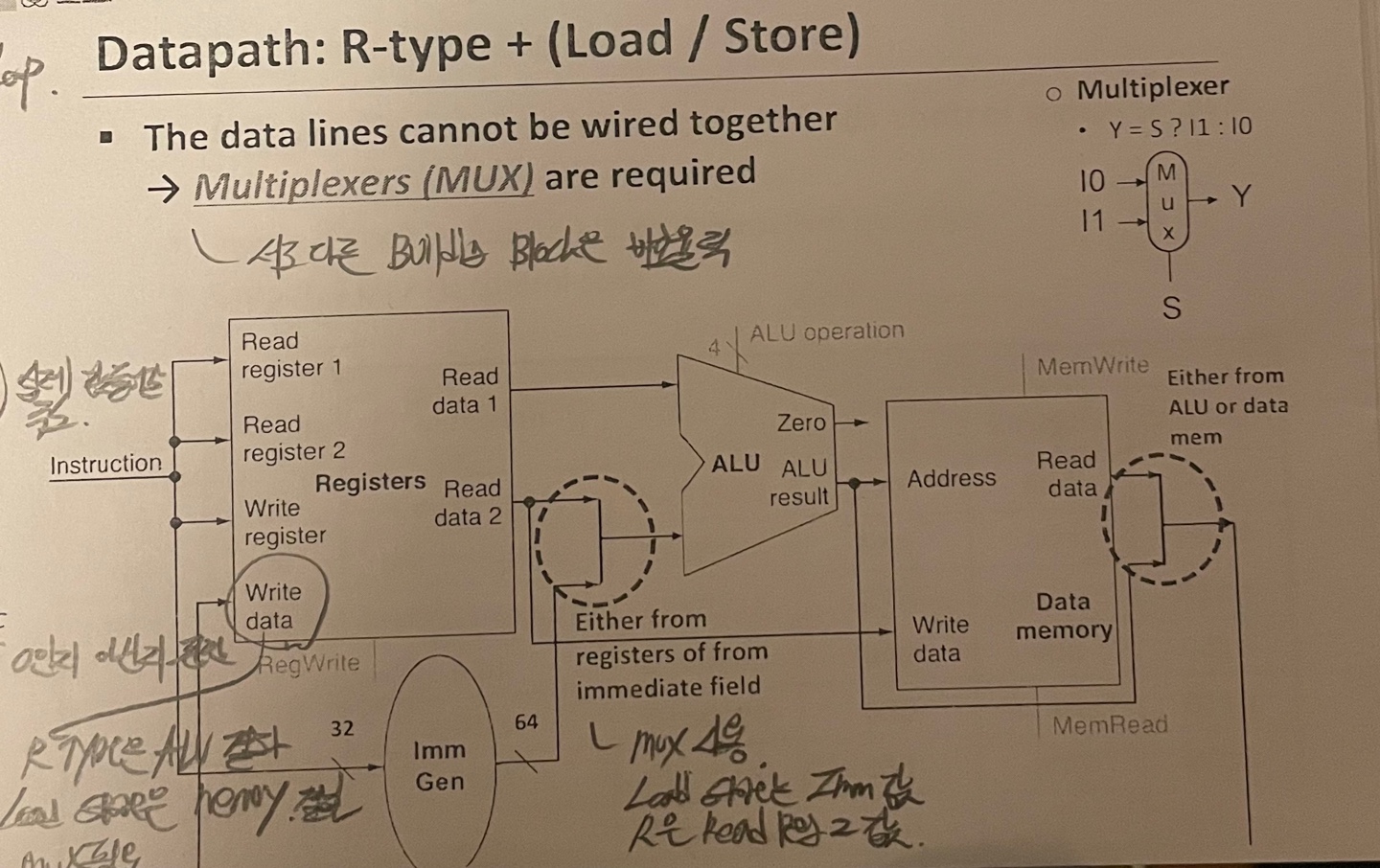

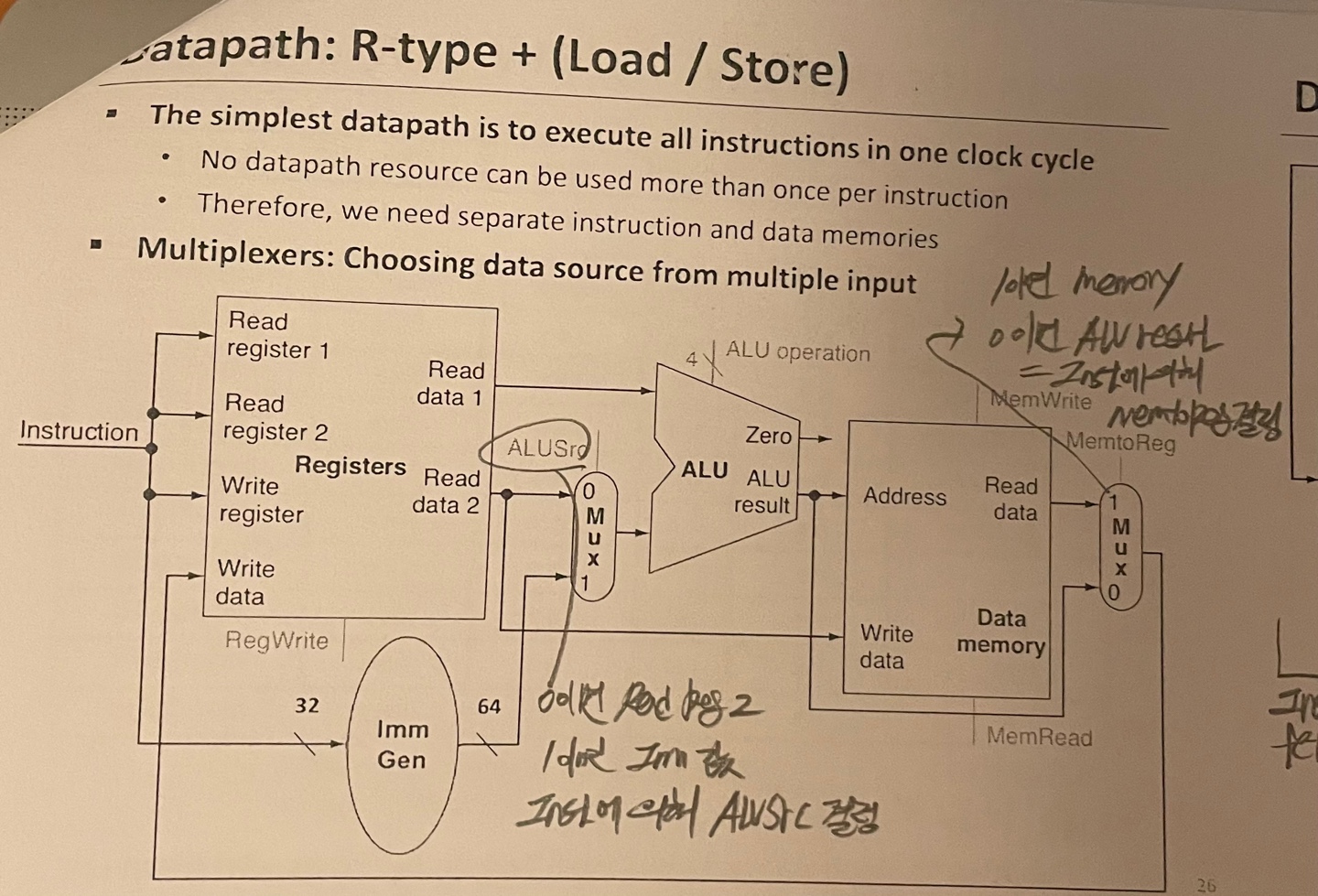

DataPath : R-type + (Load/Store)

서로 다른 Building Block 은 비효율적이다.

실제로 R-type 과 Load/Store 은 틀이 비슷하다.

Load / Store 는 IMM 의 값이 필요하고 R 은 Read data 2 의 값이 필요하다. 그래서 그 자리에 IMM 의 값과 Read data 2 중 하나를 고르는 MUX 가 필요한것이다.

그리고 R-Type 은 ALU Result 가 필요하고 Load/Store 는 Memory 결과가 필요하다. 그래서 이부분도 MUX 가 필요한 것이다.

이 사진에서도 Read Data 2 와 Imm 값의 MUX 는 MUX 의 값이 0 이면 Read data 2 의 값 1 이면 Imm 값이 선택되게 되는것이다.

Instruction 에 의해 ALU SRC 가 결정되게 된다.

뒤에도 MUX 의 값이 0 이면 ALU Result 값 1 이면 Memory 값을 가진다.

똑같이 Instruction 에 의해 Memto Reg 가 결정된다.

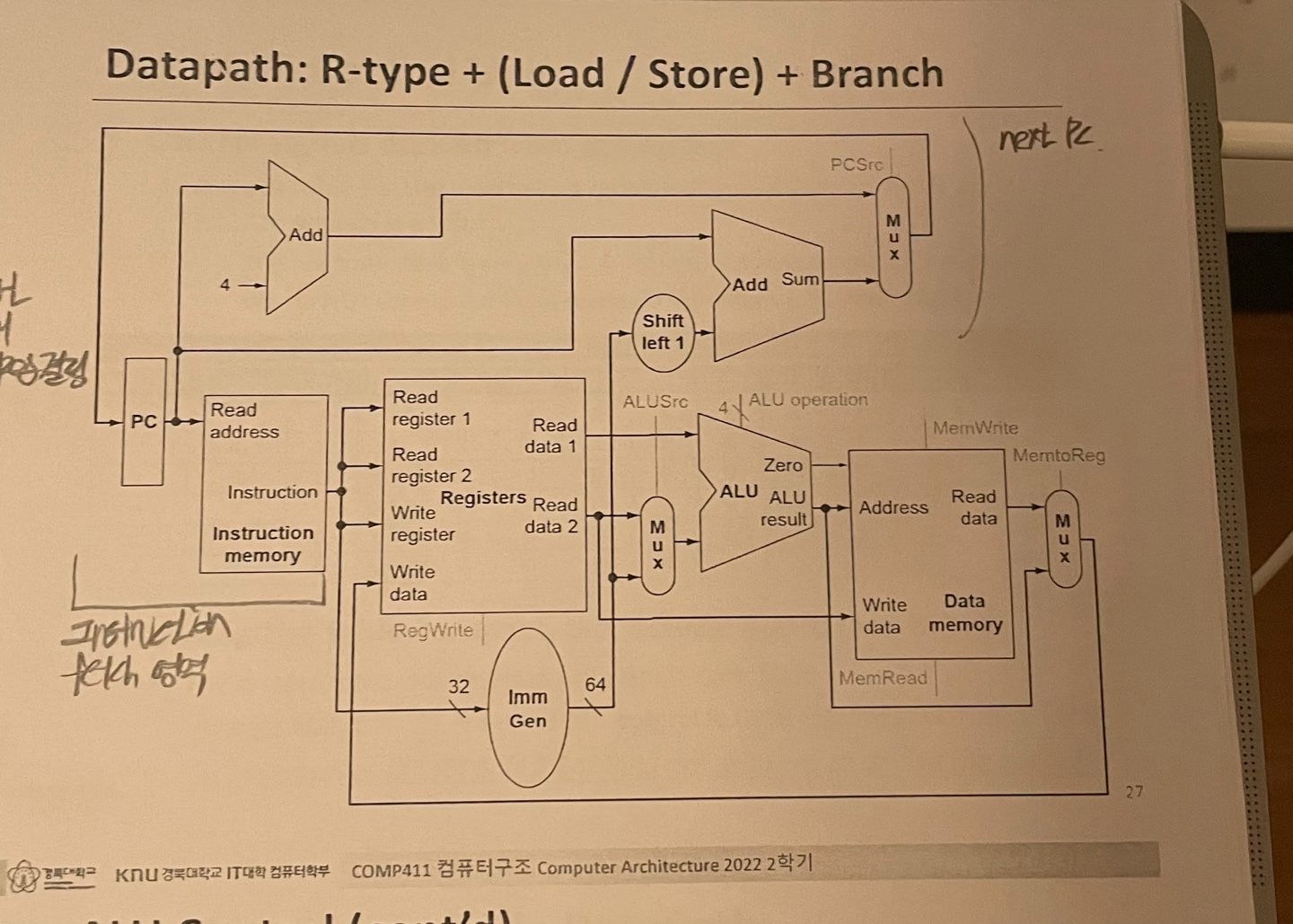

이것이 R-type + Load/Store + Branch 그림이다.

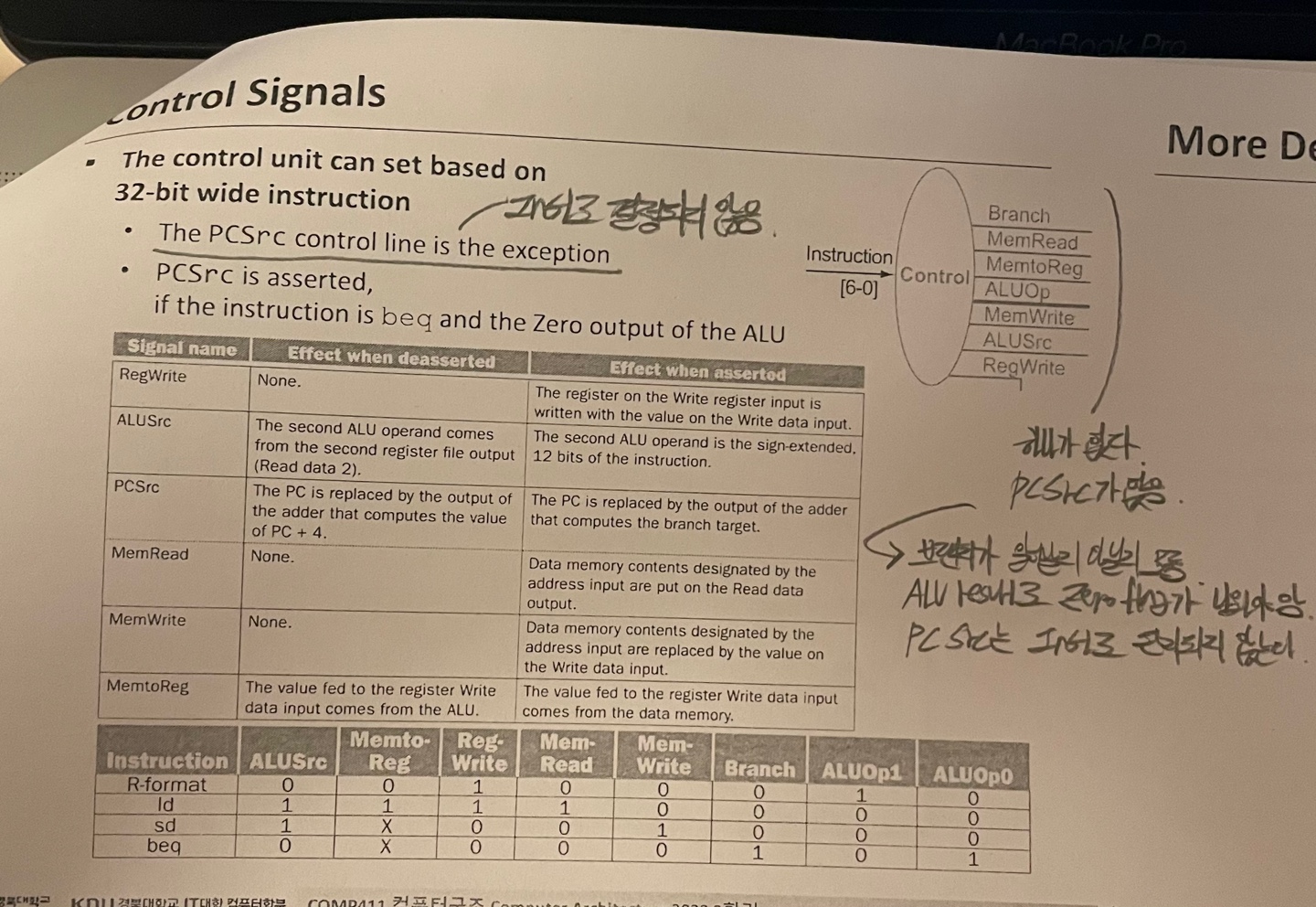

Control Signals

이 사진을 보면 Instruction 의 Control 이 하나가 없다.

바로 PC Src 인데 PC Src 는 branch 가 일어날지 아닐지 모른다. ALU Result 로 Zero Flag가 나와야 안다.

그래서 PCSRC 는 instruction 으로 관리되지 않는다.

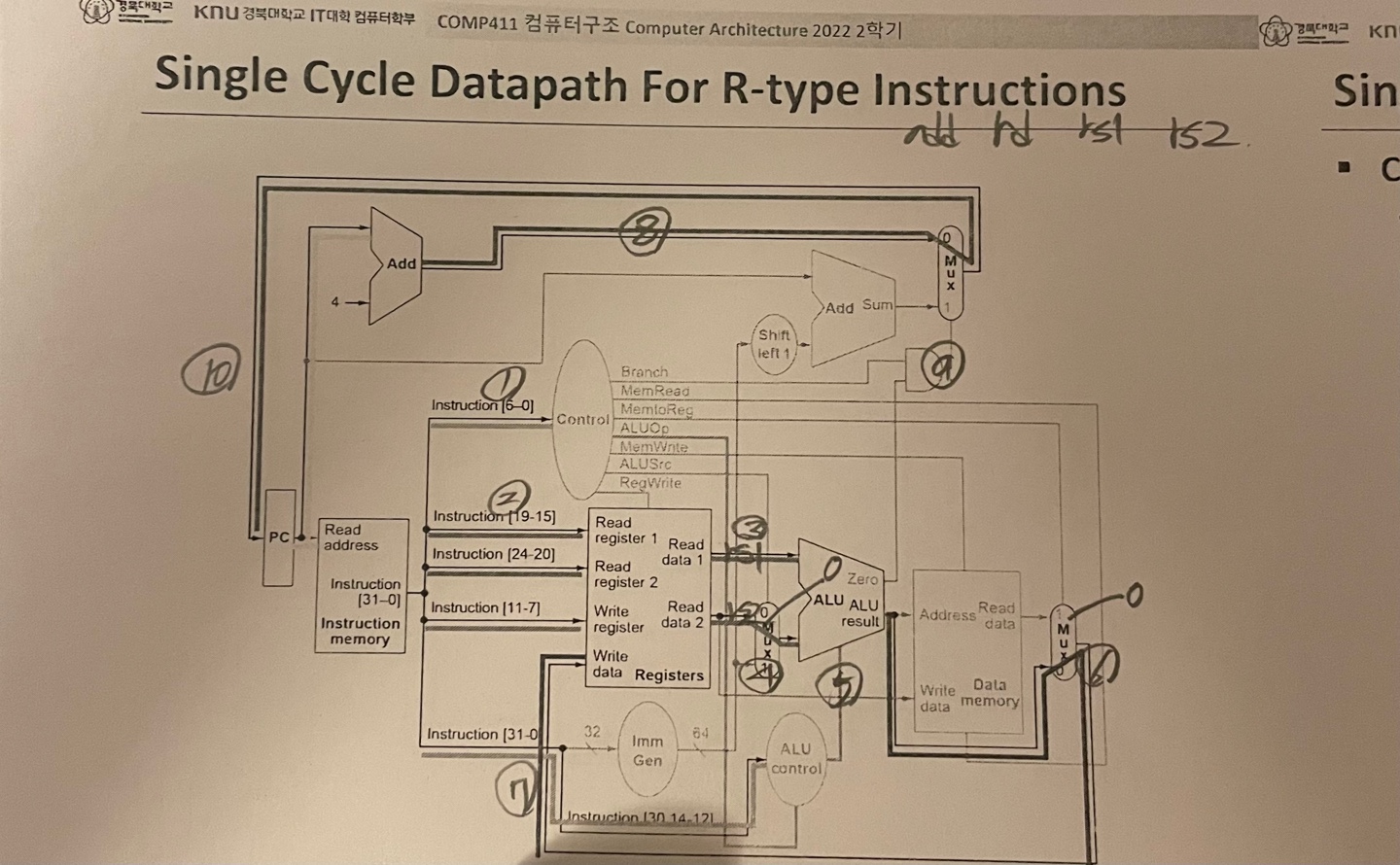

Single Cycle DataPath For R-Type Instruction

add rd rs1 rs2 일때의 그림이다.

Single Cycle DataPath For Load Instruction

Single Cycle DataPath For Store Instruction

Single Cycle DataPath for BEQ Instruction

결국 Single Cycle Implementation 은 하나의 사이클에서 모든 우리가 아는게 되어있어야한다. 지금은 사용하지 않는다.

가장 긴놈의 명령어에 맞게 짤수밖에 없다

R-type 이 1초 LOAD 가 5초라고하면 5초로 만들어야한다.

지금은 Multi-cycle Implementation 을 사용한다.

다음장에서 알아볼것.