Digital Design Basic Practice

1.Half Adder, Full Adder

sum = A ⊕ Bcarry = ABex)A + B + Cin = sum0 + 0 + 1 = 10+ 1 + 1 = 10 -> sum = 0, carry = 1Sum= (A ⊕ B) ⊕ CinCARRY-OUT = AB + Cin(A ⊕ B)both A and B are

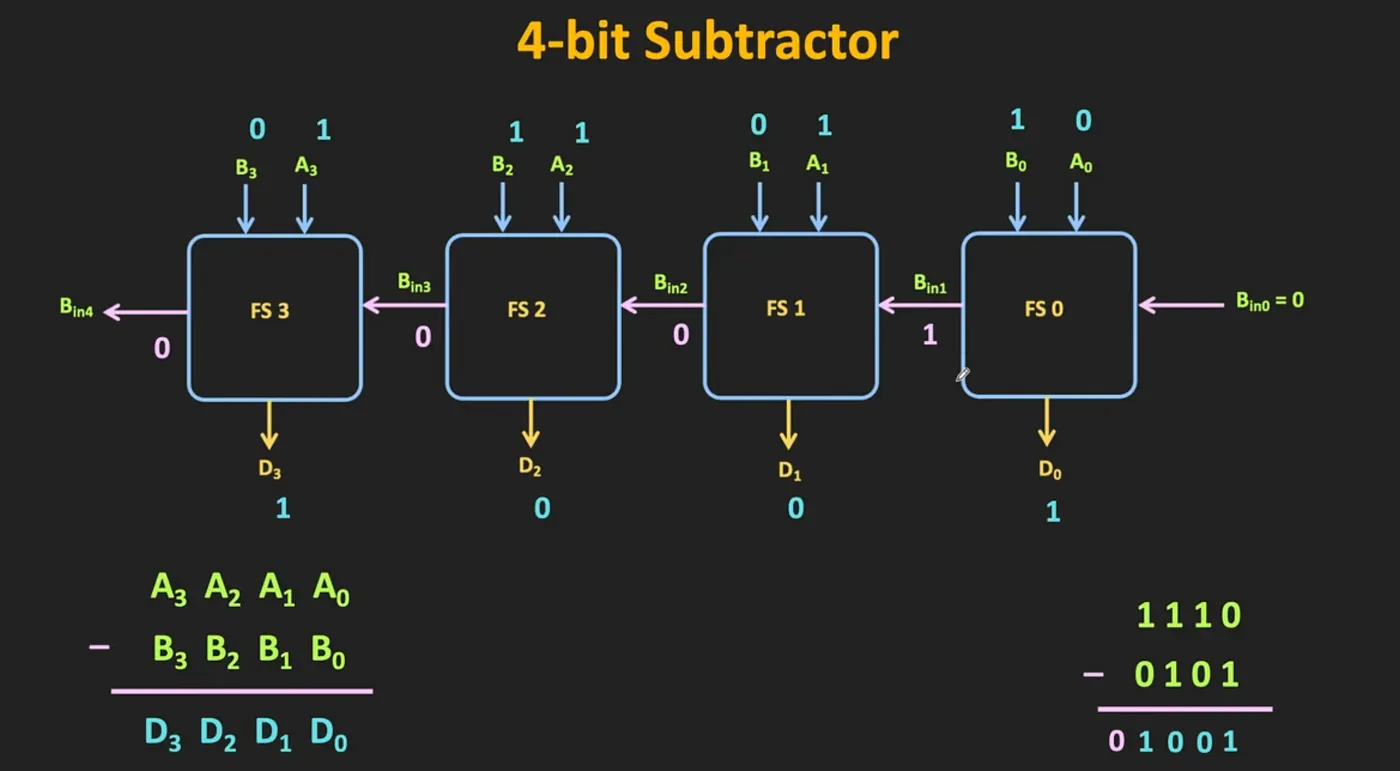

2.4-bit Adder and Subtractor

14–5 = 1110–0101Change 5(0101) by using 2’s Complement0101-> 1010+1 -> 101114–5=1110+1011, carry=112–7 = 1100–0111 = 1100+1001= 0101, carry =1Change B

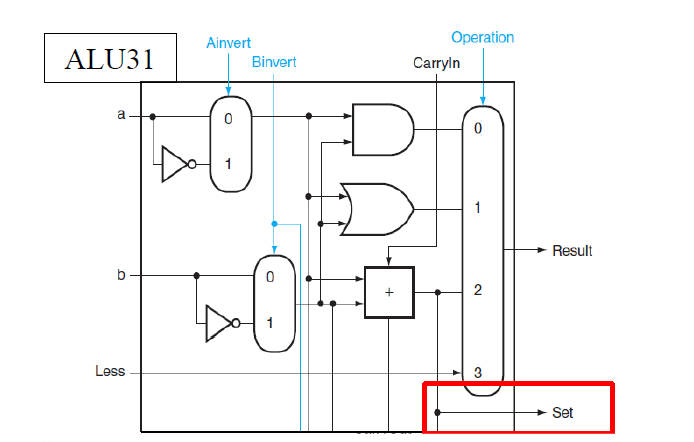

3.ALU(Arithmetic Logic Unit)

ALU는 산술(덧셈·뺄셈 등)과 논리(AND/OR/XOR 등) 연산을 수행하는 조합논리 블록 산술: ADD, SUB, (option) MUL, INC, DEC, ABS 등논리: AND, OR, XOR, NOT, NAND, NOR 등비트 연산 및 쉬프트: SHL (log

4.FSM(Traffic Light Controller)

FSM은 현재 상태(Current State) 와 입력(Input) 에 따라다음 상태(Next State) 와 출력(Output) 을 결정하는 논리 회로typedef: 새로운 자료형 정의enum: 열거형-여러 상태 이름을 나열reg 1:0: 각 상태를 2비트로 표현{S

5.FSM (Elevator)

2층 엘리베이터1\. 엘리베이터는 1층 또는 2층 중 하나에 위치2\. 버튼은 3개 1층 버튼(call_1) 2층 버튼(call_2) 엘리베이터 안의 층 선택 버튼(req_1, req_2)3.엘리베이터 동작 1층에서 2층 요청 -> 올라감 2층에서 1층

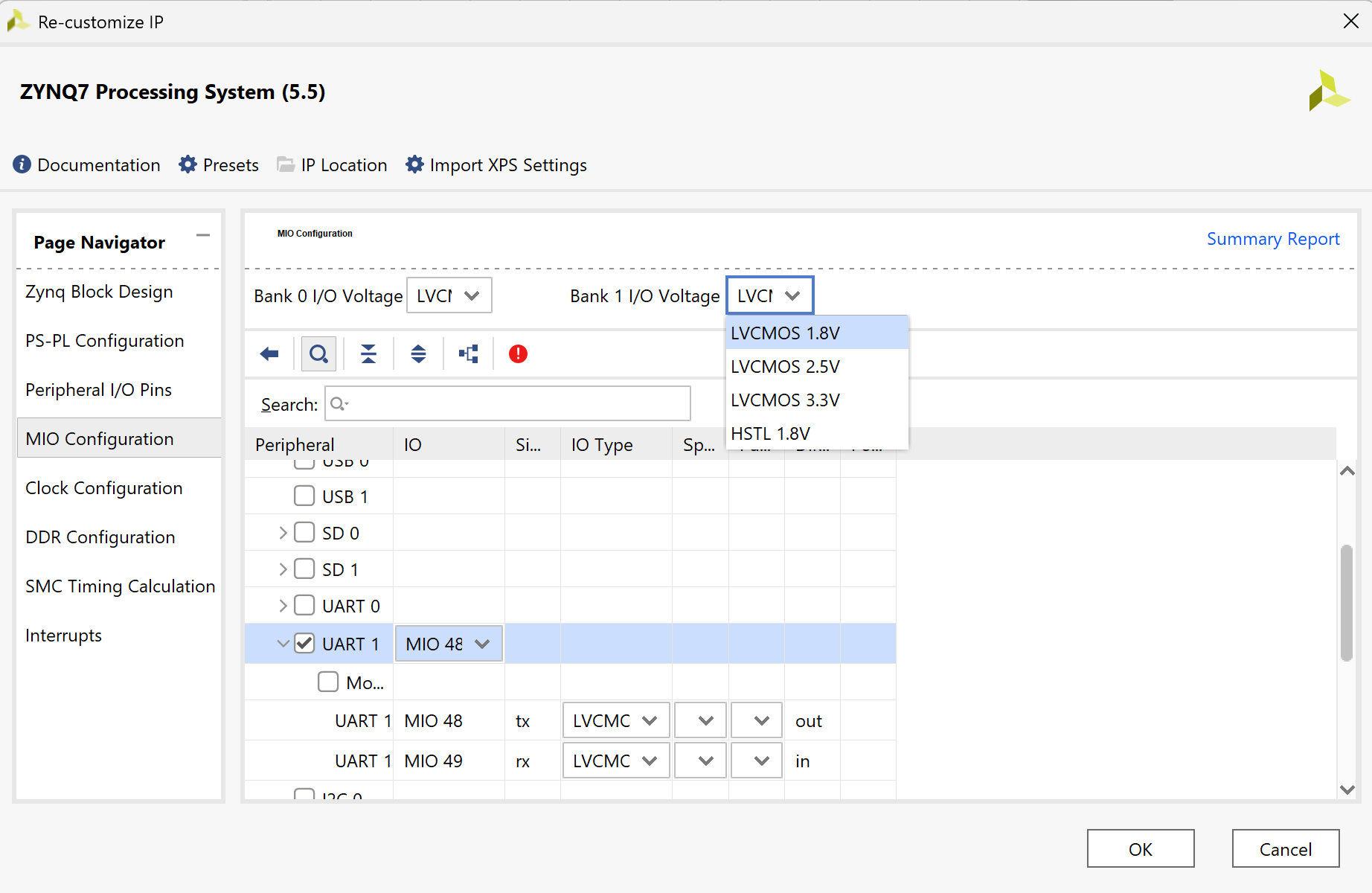

6.FPGA hello_world(PS)

create lab4_hello_seungyun_worldCreate Block DesignDiagram 에서 + 누르고 ZynQ7 Processing System 클릭UART 1에 체크하고 Bank 1 IO에 LVCMOS 1.8V로 변경해주기 안쓰는 기능 체크 해제

7.Zynq 개발 전체 구조

→ 여러 Verilog를 묶어서 재사용 가능한 하드웨어 블록으로 만든다.→ FPGA 전체 시스템을 구축하는 하드웨어 통합 환경이다.→ Zynq PS + Custom IP + AXI 연결을 한 눈에 보여주는 시스템 회로도이다.→ Vivado에서 만든 하드웨어를 FPGA가