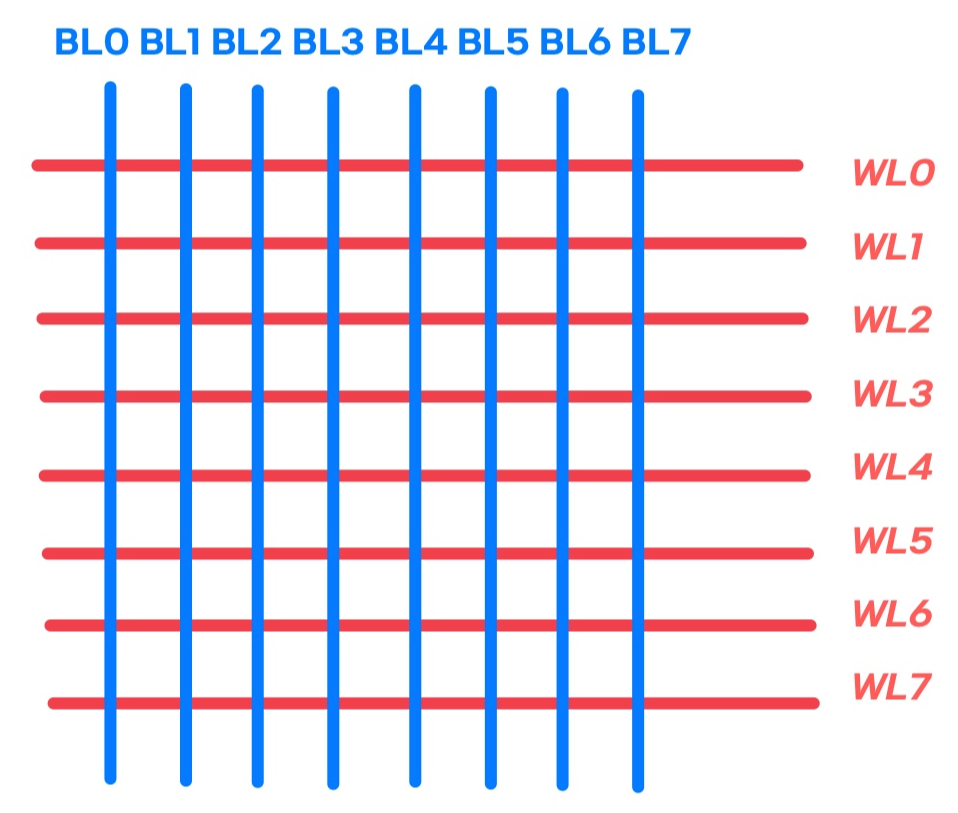

Bitline 과 wordline

-

실제 DRAM 메모리는 단일 셀로 구성된 것이 아닌 여러 개의 DRAM cell의 집합, 즉 array 형태로 이루어져 있다.

-

예를 들어 256bit DRAM이라고 하면 256개의 DRAM cell이 16X16 배열 형태로 구성

-

가로줄을 wordline, 세로줄을 bitline으로 정의

DRAM (Dynamic RAM)

구조 및 특징

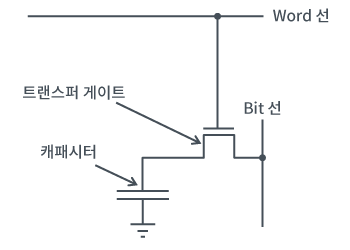

구조 개요

- 1개의 트랜지스터 + 1개의 커패시터 (1T1C 구조)로 하나의 비트를 저장

커패시터의 전하 충전량으로 0과 1을 구분

재충전(Refresh) 필요 – 전하가 자연 방전되기 때문

기본 셀 구성

- Access Transistor: Word Line에 의해 제어

Storage Capacitor: Bit Line과 연결되어 전하 저장

DRAM 특징

- 회로 구조 단순 → 고집적, 저비용

속도는 SRAM보다 느림 (수십 ns 수준)

주 기억장치(RAM), 그래픽 메모리, 모바일 메모리 등에 사용

동작 원리

▶ 동작 단계:

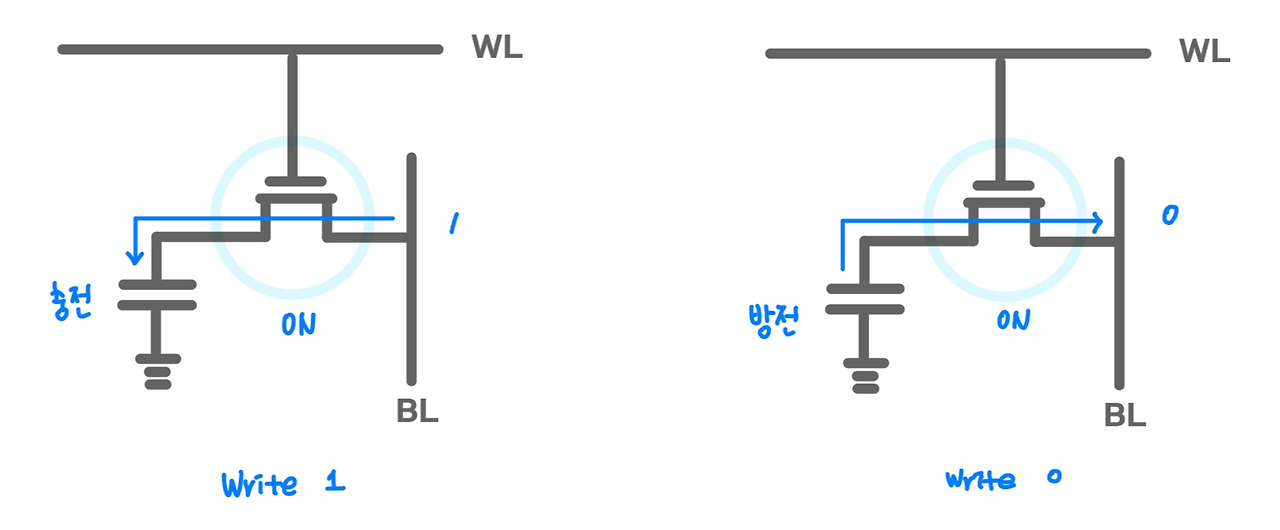

쓰기 (Write)

- Word Line 활성화 (Word선 전위를 high)

Bit Line에서 원하는 전하(0 or 1)를 커패시터에 충전 또는 방전

Word선 전위를 Low (Return to hold mode)

※ 커패시터에 저장된 전하는 hold mode에서 WL를 off 시키면서

외부와 격리되어 쓰기 동작이 완료

- BL에 V(H)를 인가하면 커패시터에 전하가 충전되며 데이터 '1'이 써진다.

BL에 V(L)를 인가하면 커패시터에서 전하가 방전되며 데이터 '0'이 써진다.

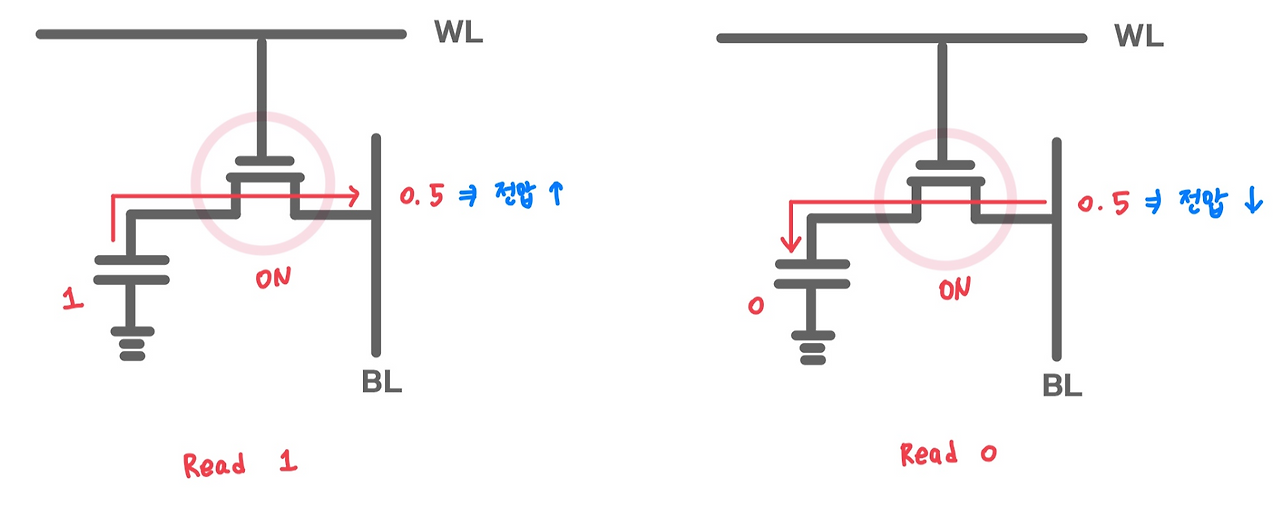

읽기 (Read)

-

Word Line 활성화

커패시터의 전하를 Bit Line으로 방출

Sense Amplifier가 전하량을 감지하여 0/1 판단 -

커패시터에 V(H)가 걸려있는 상태라면 전하가 커패시터에서 BL로 이동하면서 BL 전압이 약간 증가함

커패시터에 V(L)가 걸려있는 상태라면 BL의 전하가 커패시터로 이동하면서 BL 전압이 약간 감소함

읽은 후에는 원래 데이터가 파괴됨 → 즉시 재쓰기 필요 (Restore)

SRAM (Static RAM)

구조 및 특징

구조 개요

-

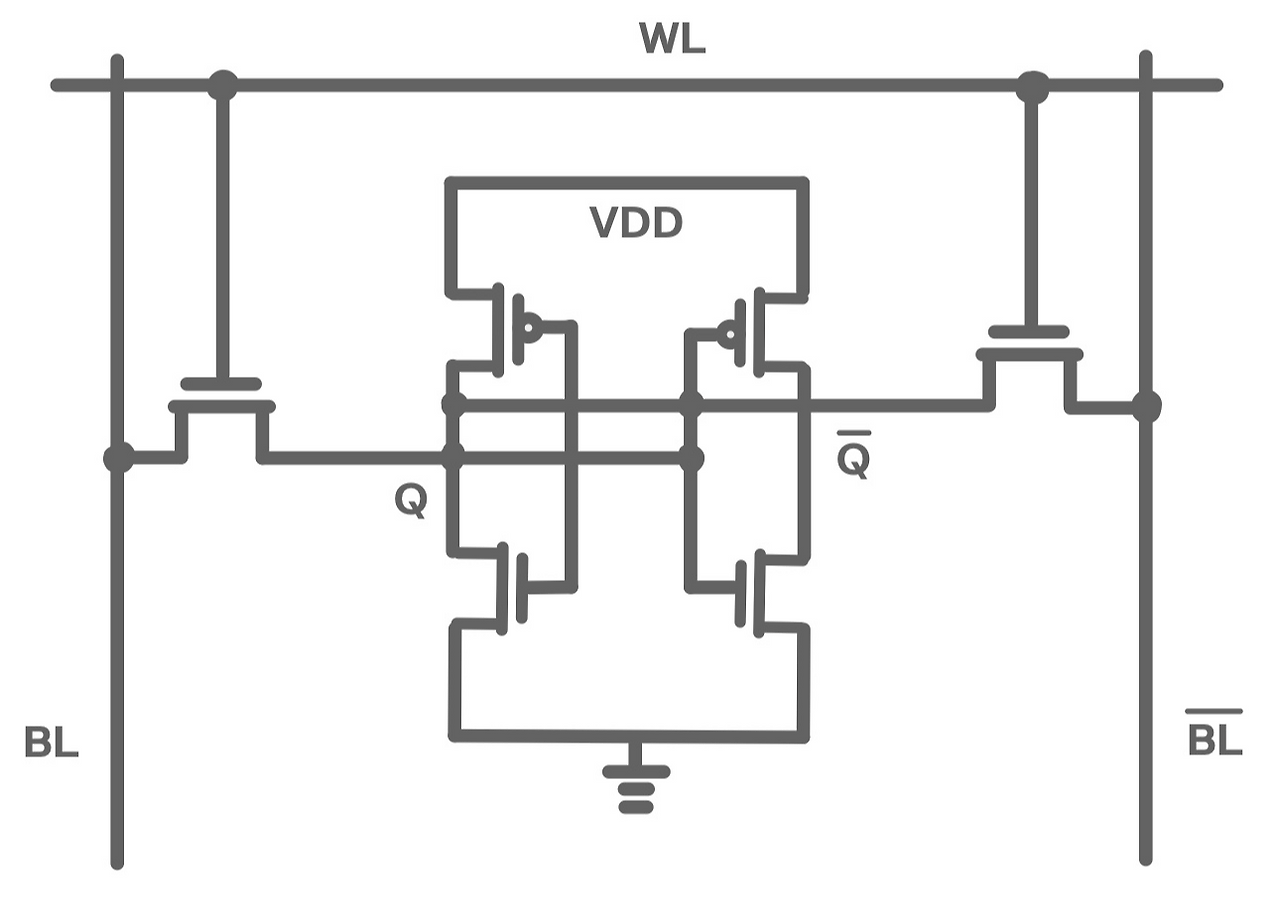

6개의 트랜지스터(6T 구조)로 하나의 비트를 저장

내부에 플립플롭(Flip-Flop) 회로를 구성해 데이터를 유지

재충전 불필요, 전원이 켜져 있는 동안은 상태를 그대로 유지 -

기본 셀 구성

2개의 Cross-Coupled Inverter (플립플롭 역할)

2개의 Access Transistor (Word Line을 통해 Bit Line과 연결)

SRAM 특징

매우 빠른 접근 속도 (수 ns 수준)

복잡한 회로 구조 → 면적 큼 → 고밀도 구현 어려움

캐시 메모리, 레지스터 파일 등에 사용

동작 원리

-

플립플롭(Flip-Flop) 구조로 데이터를 유지

전원이 켜져 있는 동안, 별도 Refresh 없이 상태 유지 -

셀 구성: 6T 셀

2개의 크로스 커플드 인버터 → 1비트를 기억

2개의 Access 트랜지스터 → Bit Line과 연결

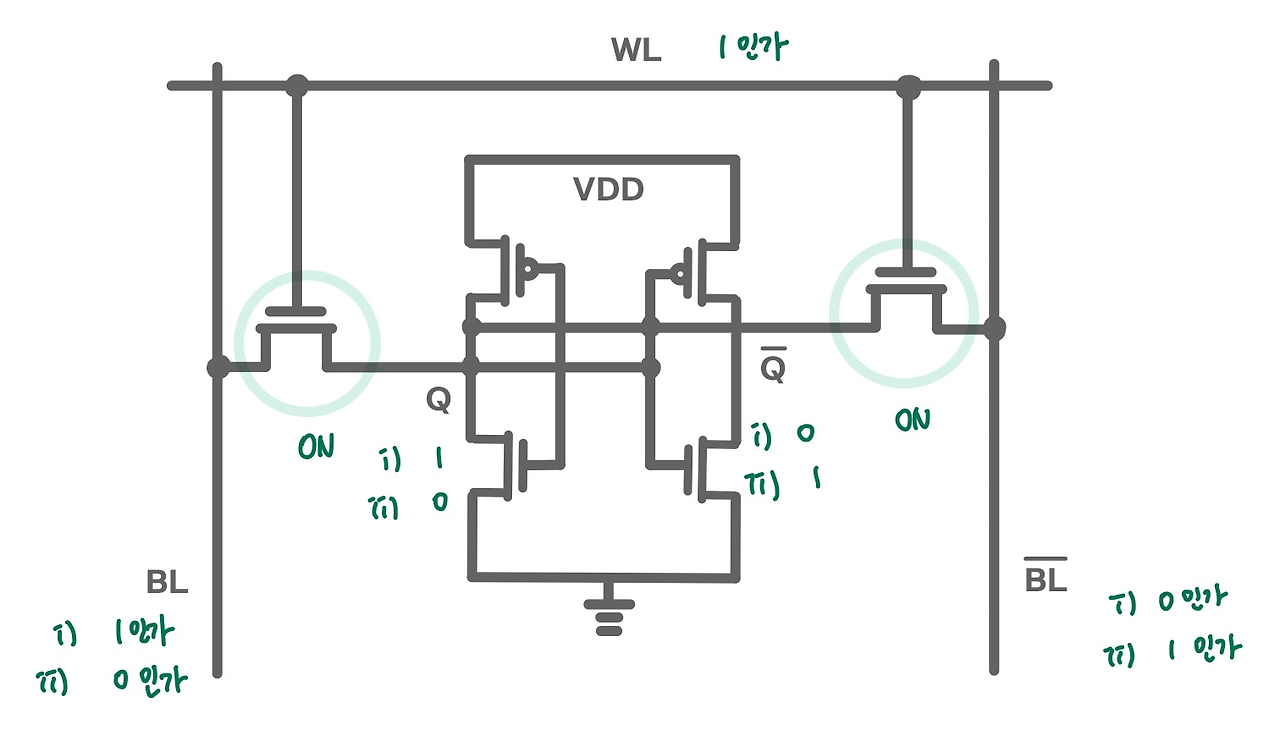

▶ 동작 단계:

- 쓰기 (Write)

" WL = 1(High) 인 상태에서 쓸 데이터를 BL에 주면 데이터가 써짐 "

- Word선 전위를 high

- Bit선의 전위를 부여 (D=low, D=high) → Flip-Flop 상태 결정

(Write data by setting BL & BLb.) - Word선 전위를 low

Return to hold mode.

※ BL과 BLb에는 각각 반대되는 데이터를 주어야한다.

※ Hold mode로 돌아가 WL = 0이 되면 access tr이 꺼지면서 새로운 데이터가 들어가지 않아 내부 래치 회로에서 현재값을 유지하게 된다. 이에 따라 DRAM처럼 주기적으로 refresh를 해줄 필요가 없다.

-

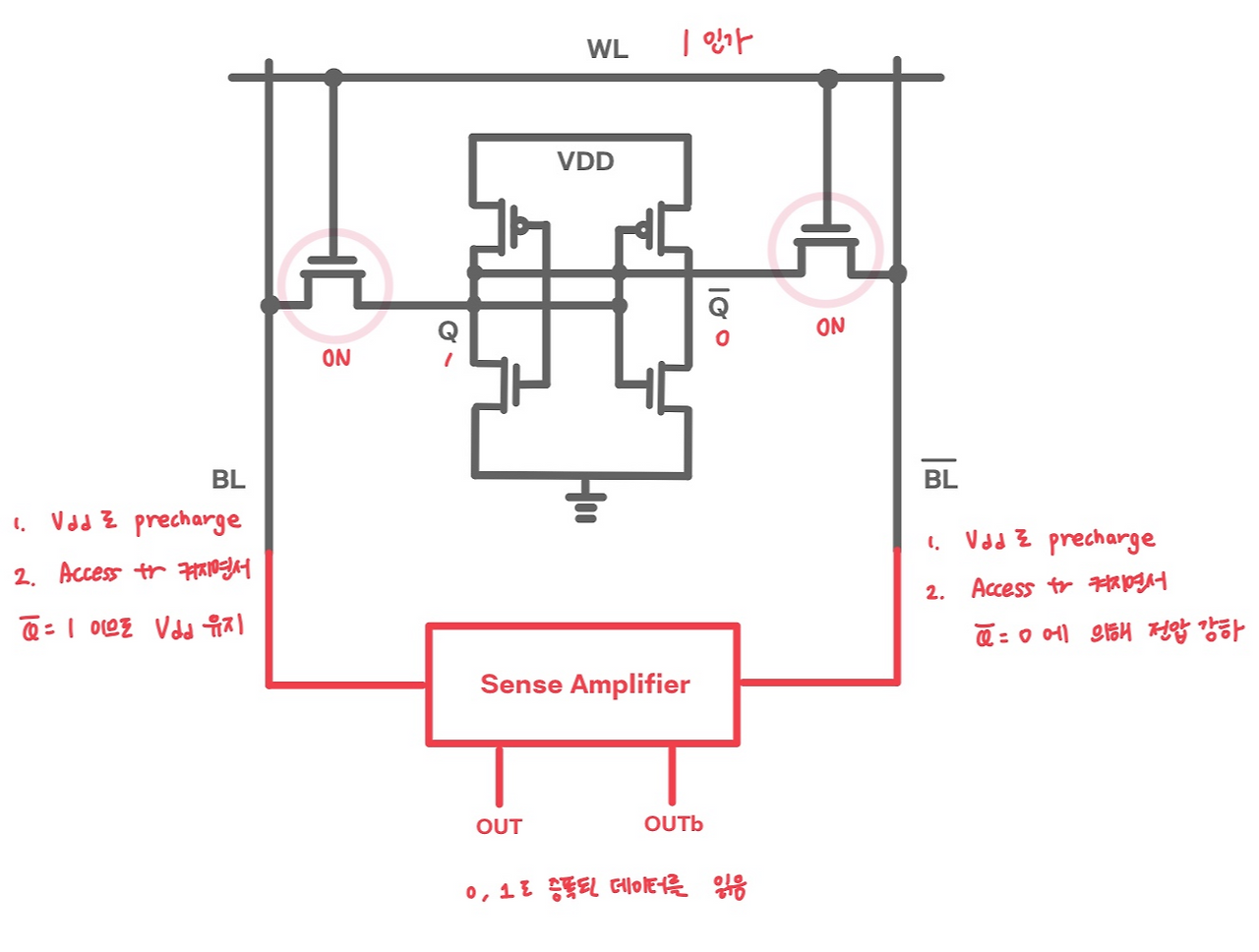

읽기 (Read)

-

Word선 전위를 off

Bit선을 프리차지 (D, D에 동일 전위)

Word선 전위를 high

Bit선이 low, high의 상태가 됨

센스 앰프로 증폭

Refresh 필요 없음

※ SRAM의 bit cell은 누설 전류와 사이즈 측면에서 매우 작게 설계되기 때문에 그 전압차를 판별하기 힘들다. 따라서 BL과 BLb를 Vdd로 precharge하고 cell data에 의해 발생하는 전압차를 sense amplifier로 증폭시킨다.

Ref

https://www.rohm.co.kr/electronics-basics/memory/memory_what2

https://boaaaang.tistory.com/entry/DRAM%EC%9D%98-%EB%8F%99%EC%9E%91-%EB%8C%80%EA%B8%B0-%EC%9D%BD%EA%B8%B0-%EC%93%B0%EA%B8%B0-REFRESH-%EB%8F%99%EC%9E%91